# RONTGRADE

## AMD Versal<sup>™</sup> VSC1902 + Frontgrade Ecosystem Design Examples

January 2025

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents, rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.

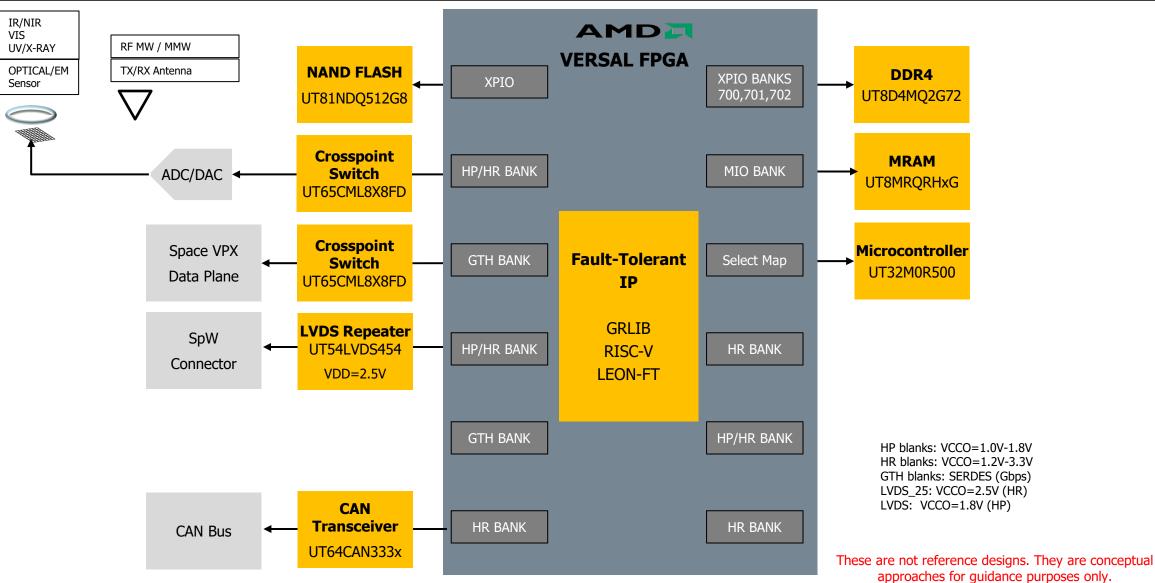

## Frontgrade Versal FPGA Ecosystem

For more information, please contact us at Frontgrade.com

FRONTGRADE

Frontgrade Private - This document includes Frontgrade confidential and or proprietary information that shall not be duplicated, used, or disclosed, in whole or in part, except for the limited purpose for which it has been furnished.

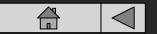

## UT8MRQxG MRAM Memory

## MRAM Memory Product Details

#### Functional Block Diagram

(Dual Quad SPI Interface)

| Part Number                | UT8MRQRHxG                              |

|----------------------------|-----------------------------------------|

| Density                    | 1,2,4,8 Gb                              |

| Interface                  | SPI                                     |

| Configuration              | 2x Quad                                 |

| Supply Voltage             | +3.3V core; 1.8, 2.5V, 3.3V IO supplies |

| Write Endurance            | 10 <sup>16</sup> write cycles           |

| Data Retention             | > 10 years @ 85°C                       |

| Process Technology         | 22nm pMTJ STT                           |

| Temp Range                 | -40°C to +125°C                         |

| Package                    | 224-ball FBGA (20x20 mm)                |

| Operational<br>Environment |                                         |

| TID:                       | 100 krad (Si)                           |

| SEL:                       | 78 MeV-cm²/mg @105°C,<br>2.7V           |

| Qualifications             | PEM L2, L1                              |

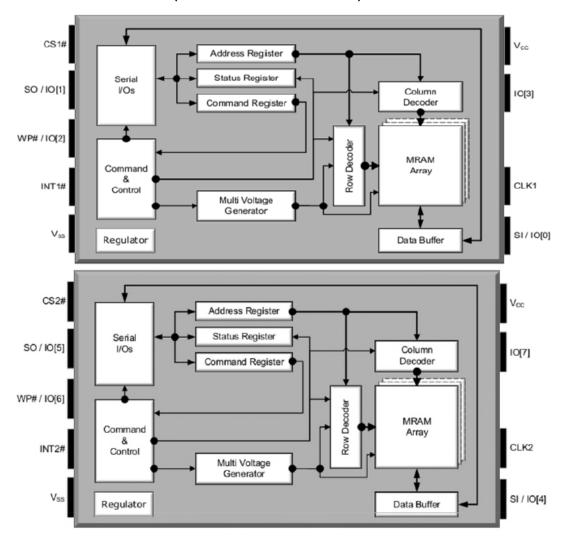

## UT8MRQxG MRAM Memory SPI Interface

#### Interface:

UT8MRQRHxG – Dual Quad SPI bus operated

#### **Operation**:

- UT8MRQRHxG stores Versal configuration

image

- Utilizes Master SPI configuration mode to auto load the image to the FPGA

Frontgrade Private - This document includes Frontgrade confidential and or proprietary information that shall not be duplicated, used, or disclosed, in whole or in part, except for the limited purpose for which it has been furnished.

## UT8SD4MQ2G72 DDR4 Memory

# UT8SD4MQ2G72 - 18GB ( 16GB + 2GB ECC ) DDR4

**Product Details**

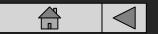

#### Functional Block Diagram

| Part Number             | UT8SD4MQ2G72                                               |  |

|-------------------------|------------------------------------------------------------|--|

| Density                 | 18GB (16GB + 2GB ECC)                                      |  |

| Configuration           | 2G x 72 (9 die)                                            |  |

| Read/Write time         | 220mW burst read/write power per die                       |  |

| Supply Voltage          | 1.2V V <sub>DD</sub> & V <sub>DDQ</sub>                    |  |

| Data Rate               | 2400 MT/s                                                  |  |

| Temp Range              | -55°C to +125°C                                            |  |

| Typical Power           | ThetaJ-C = 4 °C/W                                          |  |

| Package                 | 266-pin PBGA, 15mm x 20mm x 1.9mm.<br>1.17gm and 1mm pitch |  |

| Operational Environment |                                                            |  |

| TID target:             | 100 krad                                                   |  |

| SEL Event Rate:         | 6.0E-8 events/device-day at GEO (LET from 37 to 82) @105C  |  |

| SEU:                    | 2.23E-14 Errors/Bit-Day                                    |  |

| Qualification           | Frontgrade Space PEM L2                                    |  |

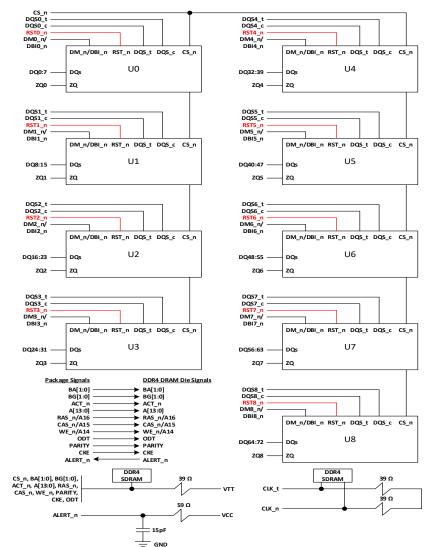

# UT8SD4MQ2G72 DDR4 Memory

#### Interface

#### Interface:

• UT8SD4MQ2G72 – Standard DDR4 interface

#### **Operation**:

UT8SD4MQ2G72 works with Versal integrated DDR4 Controller

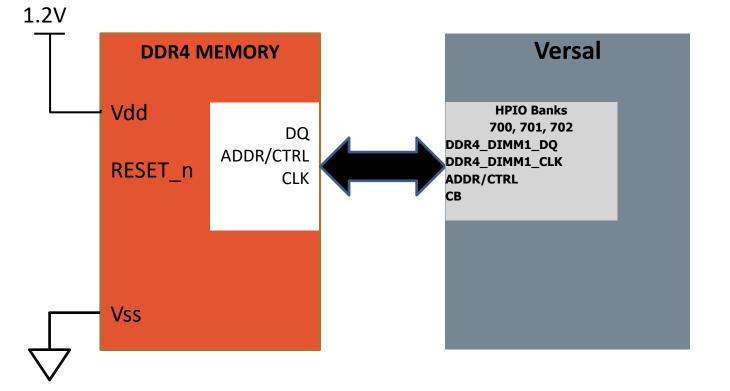

## UT81NDQ512G8T 4Tb NAND Flash

## UT81NDQ512G8T 4Tb NAND Flash Product Details

| Part Number UT81NDQ512G8T            |                                                                                     |  |

|--------------------------------------|-------------------------------------------------------------------------------------|--|

| SMD#                                 | n/a                                                                                 |  |

| Density                              | 4Tb                                                                                 |  |

| Configuration                        | uration 4 Target, 8 LUN 64Gb x8 module                                              |  |

| Page Size                            | 18,592 bytes (TLC Mode)                                                             |  |

| Block Size                           | ck Size 2304 Pages                                                                  |  |

| Interface                            | ONFI 4.0 Compliant (132 ball footprint)<br>Backward compatible to ONFI 2.x          |  |

| Supply Voltage                       | +3.3V (core) and +1.2V or 1.8V (I/O)                                                |  |

| Transaction Rate                     | Asyn Mode 5: 50MT/s/pin<br>DDR2 Mode 8: 533 MT/s/pin<br>DDR3 Mode 9: 667 MT/s/pin   |  |

| Endurance                            | Endurance 40K Program/Erase Cycles (SLC Mode)<br>3K Program/Erase Cycles (TLC Mode) |  |

| Data Retention                       | JESD47G compliant                                                                   |  |

| Temp Range                           | -40°C to +85°C                                                                      |  |

| Typical Power 150mW (per active die) |                                                                                     |  |

| Package                              | JEDEC 132-PBGA, 12mm x 18mm x 1.4mm, 0.5g                                           |  |

| Operational Environment              |                                                                                     |  |

| TID:                                 | 30 - 50krad (Si) – Wafer lot RHA Qual Dependent                                     |  |

| SEL:                                 | <60 MeV-cm <sup>2</sup> /mg @85°C                                                   |  |

| Qualifications                       | PEM-INST-001 (NASA EEE-INST-002) – Level 2                                          |  |

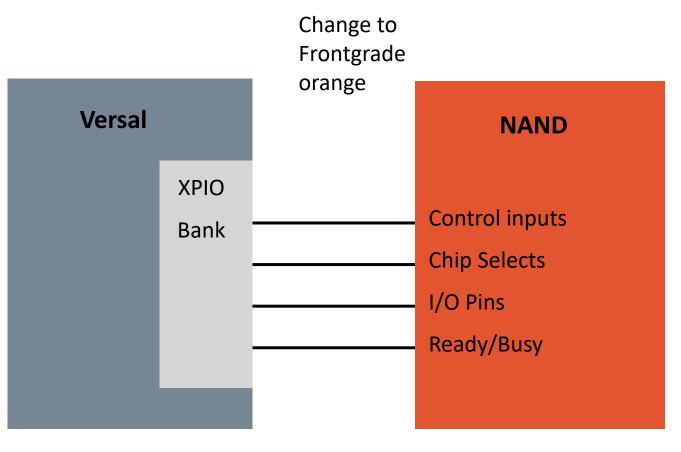

## UT81NDQ512G8T, 4Tb NAND Flash Interface

### Interface:

- Recommend using XP I/O Banks to connect the NAND to the Versal

- 8-bit operation can fit in one I/O bank

- 16-bit operation can fit in one I/O bank minus signals Eno, Eni, and Vpp

## **Operation**:

- Will require NAND controller IP to interface to the NAND

- Recommend ONFi 4.0 or higher controller

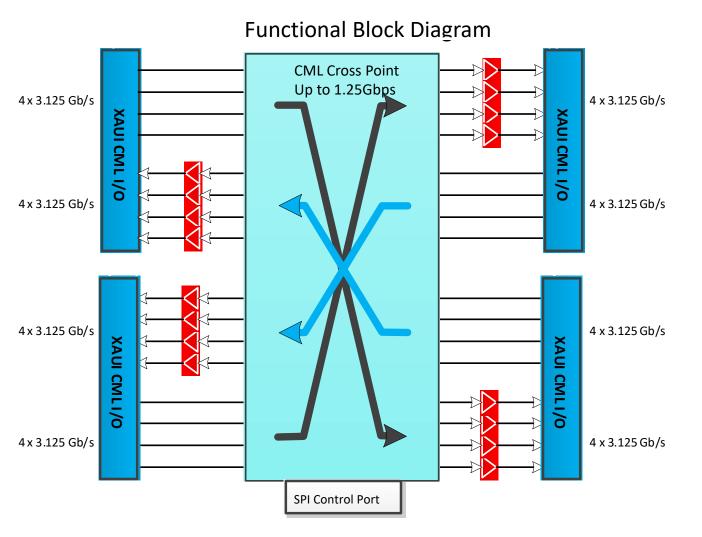

UT65CML8X8FD 3.125 Gbps Crosspoint Switch (XPS)

## UT65CML8X8FD 8x8 High-Speed Crosspoint Switch Product Features

| Part Number             | UT65CML8X8FC                                                                                                                                                                                                                                                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMD#                    | 5962-17213                                                                                                                                                                                                                                                                     |

| Channels                | 8x8                                                                                                                                                                                                                                                                            |

| Data Rate               | 3.125Gbps per channel (50Gbps total)                                                                                                                                                                                                                                           |

| Supply Voltages         | +1.2V Core <sup>1</sup> , +1.2V-+1.8V CML,<br>+2.5V SPI Port                                                                                                                                                                                                                   |

| Features                | <ul> <li>8 x 8, full duplex crosspoint switch<br/>matrix</li> <li>Protocol independent</li> <li>Low latency</li> <li>Low channel-to-channel skew</li> <li>SPI port control interface</li> <li>Power down of unused lanes</li> <li>Trimmable high-speed terminations</li> </ul> |

| Process Technology      | 130nm CMOS                                                                                                                                                                                                                                                                     |

| Typical Power           | 1.6W                                                                                                                                                                                                                                                                           |

| Package                 | 143 pin CLGA, CBGA, CCGA options<br>14.5 mm x 14.5 mm, 1mm pitch                                                                                                                                                                                                               |

| Operational Environment |                                                                                                                                                                                                                                                                                |

| Temp Range:             | -55°C to +105°C                                                                                                                                                                                                                                                                |

| TID:                    | 100 krad (Si)                                                                                                                                                                                                                                                                  |

| SEL Immune:             | LET ≤ 100 MeV-cm²/mg @105°C                                                                                                                                                                                                                                                    |

| Qualifications          | QML-Q, V (pending)                                                                                                                                                                                                                                                             |

FRONTGRADE

These are not reference designs. They are conceptual approaches for guidance purposes only. Frontgrade Private - This document includes Frontgrade confidentiation promotified in the seen furnished.

## RONTGRADE

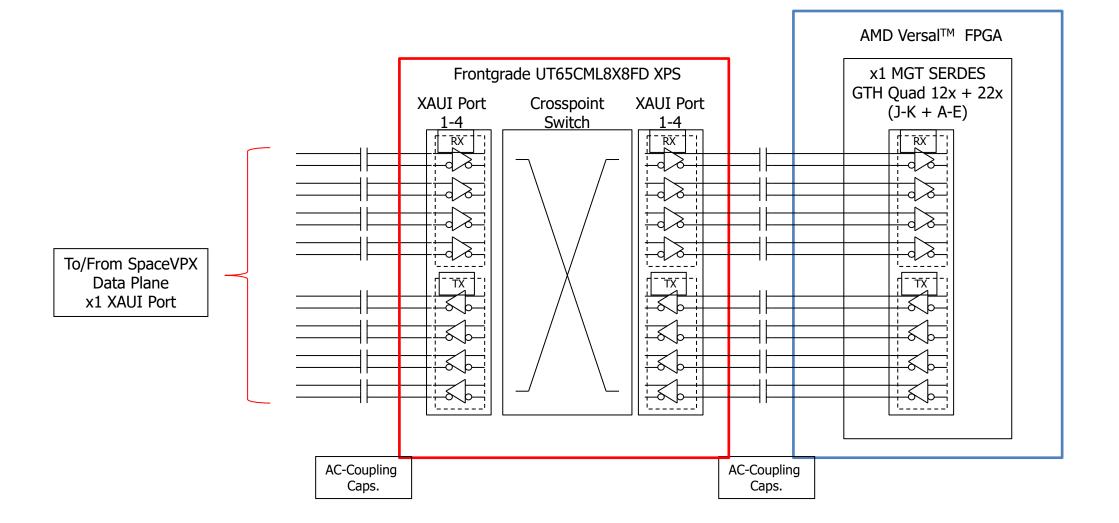

## **Versal<sup>TM</sup> FPGA + UT65CML8X8FD XPS** SpaceVPX Data Plane Interface Application

These are not reference designs. They are conceptual approaches for guidance purposes only.

Frontgrade Private - This document includes Frontgrade confidenti and popeoprifter interpretion tion to the limited purpose for which it has been furnished.

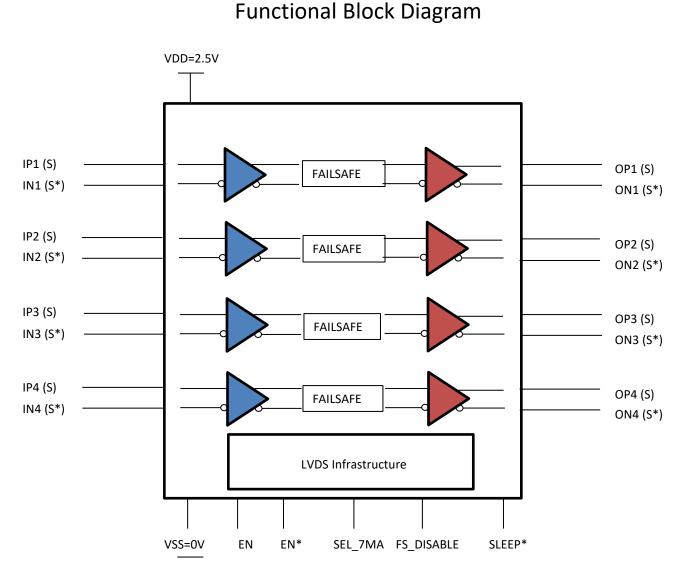

## UT54LVDS454 1.25 Gbps Quad LVDS Repeater

## UT54LVDS454 Quad Repeater High-Speed (1.25Gbps) LVDS Quad Repeater Product Details

| Part Number             | UT54LVDS454                                                                                                                                                                                                                                     |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SMD#                    | 5962-21211                                                                                                                                                                                                                                      |  |

| Channels                | Quad Repeater                                                                                                                                                                                                                                   |  |

| Data Rate               | 1.25Gbps per channel                                                                                                                                                                                                                            |  |

| Supply Voltage          | 2.5V single supply                                                                                                                                                                                                                              |  |

| Features                | <ul> <li>Selectable drive strength</li> <li>Cold sparing all pins</li> <li>Enable/Disable input to disable LVDS drivers</li> <li>Sleep mode for ultra-low power dissipation</li> <li>Fail-safe function for loss-of-signal detection</li> </ul> |  |

| Process Technology      | 130nm (LP)                                                                                                                                                                                                                                      |  |

| Typical Power           | 170mW                                                                                                                                                                                                                                           |  |

| Package                 | 72 pin CLGA<br>9mm x 10mm, 1mm pitch                                                                                                                                                                                                            |  |

| Operational Environment |                                                                                                                                                                                                                                                 |  |

| Temp Range:             | -55°C to +105°C                                                                                                                                                                                                                                 |  |

| TID:                    | 100 krad (Si)                                                                                                                                                                                                                                   |  |

| SEL Immune:             | LET ≤ 100 MeV-cm²/mg @105°C                                                                                                                                                                                                                     |  |

| Qualifications          | QML-Q, -V (pending)                                                                                                                                                                                                                             |  |

FRONTGRADE

Frontgrade Private - This document includes Frontgrade confidential and or proprietary information that shall not be duplicated, used, or disclosed, in whole or in part, except for the limited purpose for which it has been furnished.

#### FRONTGRADE

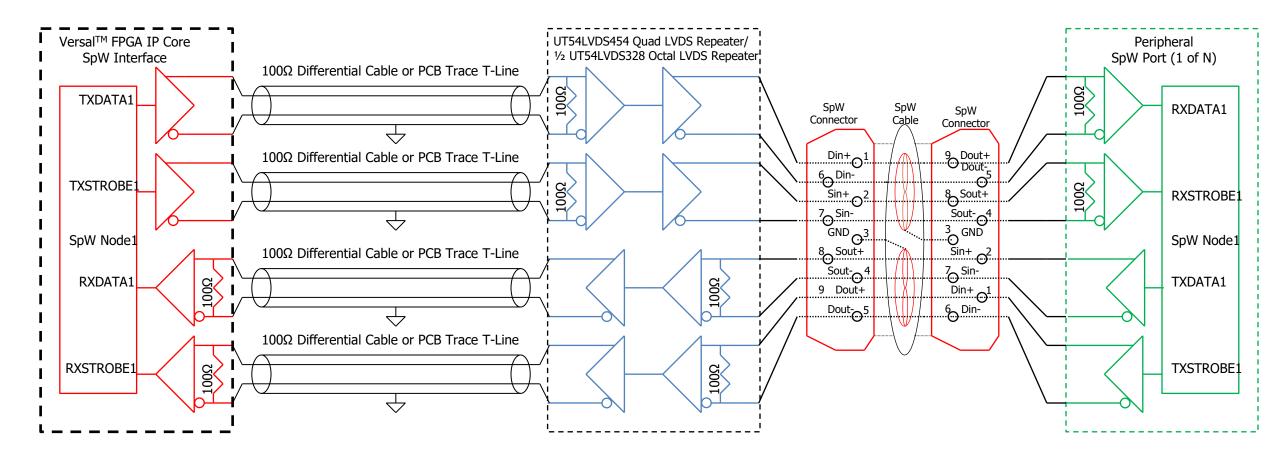

## SpW/LVDS Repeater: x1 SpW Port

These are not reference designs. They are conceptual approaches for guidance purposes only. For more information, please contact us at Frontgrade.com

# LVDS Repeaters For SpW Interfacing & AMD Versal<sup>TM</sup> FPGA I/O Protection

#### Frontgrade UT54LVDS328 400 Mbps Octal LVDS Repeater Device Features

- Data rates up to 400.0 Mbps per channel / 200 MHz clock channel

- 3.3V power supply / 3.5mA LVDS TX output drive current / Total integrated dose (TID): 1Mrad(Si)

- Extends SpW channel reach x1 UT54LVDS328 octal LVDS repeater supports x2 SpW ports

- Protects Versal<sup>™</sup> FPGA LVDS I/Os: General High-Speed Serial LVDS, ADC JESD204, and SpW Interfaces

- Cold sparing all pins / 48-lead CFP package

## Frontgrade UT54LVDS454 1.25 Gbps Dual, Full-Duplex / Quad, Simplex LVDS Repeater Device Features

- Data rates up to 1.25 Gbps per channel / protocol independent

- 2.5V power supply / Selectable 3.5mA or 7.0mA TX output drive currents / Total integrated dose (TID): 100krad(Si)

- Extends SpW channel reach x1 UT54LVDS454 quad LVDS repeater supports x1 SpW port

- Protects Versal<sup>™</sup> FPGA LVDS I/Os: General High-Speed Serial LVDS, ADC JESD204, and SpW Interfaces

- Cold sparing all pins / 71-land C-CGA/C-LGA package

### AMD Versal<sup>™</sup> FPGA to LVDS Repeater Design Considerations

- SpW Interfacing: SpW IP Cores are Available for the Versal<sup>™</sup> FPGA

- <u>https://www.xilinx.com/products/intellectual-property/1-12nthtb.html</u> / <u>https://soc-e.com/spacewire-ip-core/</u>

- Frontgrade LVDS Repeaters Support SpW Interfacing to the Versal<sup>™</sup> FPGA once the Versal I/Os are Configured as a SpW Port or Ports

- Frontgrade LVDS Repeaters Also Protect Versal<sup>™</sup> FPGA LVDS I/Os: General High-Speed Serial LVDS, ADC JESD204, and SpW Interfaces

For more information, please contact us at Frontgrade.com