# sysCLOCK PLL Design and User Guide for Nexus Platform

**Technical Note**

FPGA-TN-02095-2.5

July 2024

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information provided in this document any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

## Contents

| Contents |                                   | 3   |

|----------|-----------------------------------|-----|

| Acronyms | in This Document                  | 7   |

| 1. Intro | duction                           | 8   |

| 2. Clock | <td>8</td>                        | 8   |

| 3. Nexu  | ıs Top-Level View                 | 9   |

| 4. Clock | king Architecture Overview        |     |

| 4.1.     | Primary Clock Network             | .12 |

| 4.2.     | Edge Clock Network                | .12 |

| 5. Over  | view of Clocking Components       | .13 |

| 5.1.     | Edge Clock Dividers (ECLKDIV)     | .13 |

| 5.2.     | Primary Clock Divider (PCLKDIVSP) | .13 |

| 5.3.     | Dynamic Clock Select (DCS)        | .13 |

| 5.4.     | Dynamic Clock Control (DCC)       |     |

| 5.5.     | Edge Clock Sync (ECLKSYNC)        |     |

| 5.6.     | Oscillator (OSC)                  |     |

| 6. Prim  | ary Clocks                        |     |

| 6.1.     | Primary Clock Sources             |     |

| 6.2.     | Primary Clock Routing             |     |

| 6.3.     | Dedicated Clock Inputs            | .15 |

| 7. Prim  | ary Clock Divider (PCLKDIVSP)     |     |

| 7.1.     | PCLKDIVSP Component Definition    |     |

| 7.2.     | PCLKDIVSP Usage in VHDL           |     |

| 7.3.     | PCLKDIVSP Usage in Verilog        |     |

| •        | imic Clock Select (DCS)           |     |

| 8.1.     | DCS Timing Diagrams               |     |

| 8.1.1    |                                   |     |

| 8.1.2    |                                   |     |

| 8.1.3    |                                   |     |

| 8.2.     | DCS Component Definition          |     |

| 8.3.     | DCS Usage in VHDL                 |     |

| 8.4.     | DCS Usage in Verilog              |     |

|          | amic Clock Control (DCC)          |     |

| 9.1.     | Component Definition              |     |

| 9.2.     | DCC Usage in VHDL                 |     |

| 9.3.     | DCC Usage in Verilog              |     |

|          | nal Oscillator (OSCA)             |     |

| 10.1.    | OSCA Component Definition         |     |

| 10.2.    | OSCA Usage in VHDL                |     |

| 10.3.    | OSCA Usage in Verilog             |     |

| -        | Clocks                            |     |

| 11.1.    | Edge Clock Dividers (ECLKDIV)     |     |

| 11.2.    | ECLKDIV Component Definition      |     |

| 11.3.    | ECLKDIV Usage in VHDL             |     |

| 11.4.    | ECLKDIV Usage in Verilog          |     |

| -        | Clock Synchronization (ECLKSYNC)  |     |

| 12.1.    | ECLKSYNC Component Definition     |     |

| 12.2.    | ECLKSYNC Usage in VHDL            |     |

| 12.3.    | ECLKSYNC Usage in Verilog         |     |

|          | eral Routing for Clocks           |     |

| -        |                                   |     |

| 14.1.    | sysCLOCK PLL Overview             |     |

| 14.2.    | PLL Features                      | .36 |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| 14.2.1. Dedicated PLL Inputs                                                 |    |

|------------------------------------------------------------------------------|----|

| 14.2.2. Clock Injection Delay Removal                                        |    |

| 14.2.3. Clock Phase Adjustment                                               |    |

| 14.2.4. Frequency Synthesis                                                  |    |

| 14.2.5. Legacy Mode (Standby)                                                |    |

| 14.3. sysCLOCK PLL Component Definition                                      |    |

| 14.4. Functional Description                                                 |    |

| 14.4.1. Refclk (CLKI) Divider                                                |    |

| 14.4.2. Feedback Loop (CLKFB) Divider                                        |    |

| 14.4.3. Output Clock Dividers (CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, CLKOS5) |    |

| 14.4.4. Phase Adjustment (Static Mode)                                       |    |

| 14.4.5. Phase Adjustment (Dynamic Mode)                                      |    |

| 14.5. PLL Inputs and Outputs                                                 |    |

| 14.5.1. CLKI Input                                                           | 40 |

| 14.5.2. CLKFB Input                                                          |    |

| 14.5.3. RST Input                                                            | 40 |

| 14.5.4. Dynamic Clock Enables                                                | 41 |

| 14.5.5. PLLPD_EN_N Input                                                     | 41 |

| 14.5.6. Dynamic Phase Shift Inputs                                           | 41 |

| 14.5.7. PHASESEL Input                                                       | 41 |

| 14.5.8. PHASEDIR Input                                                       | 42 |

| 14.5.9. PHASESTEP Input                                                      | 42 |

| 14.5.10. PLL Clock Outputs                                                   | 42 |

| 14.5.11. LOCK Output                                                         |    |

| 14.6. Dynamic Phase Adjustment                                               | 43 |

| 14.6.1. VCO Phase Shift                                                      |    |

| 14.7. Fractional-N Synthesis Operation                                       | 44 |

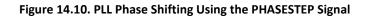

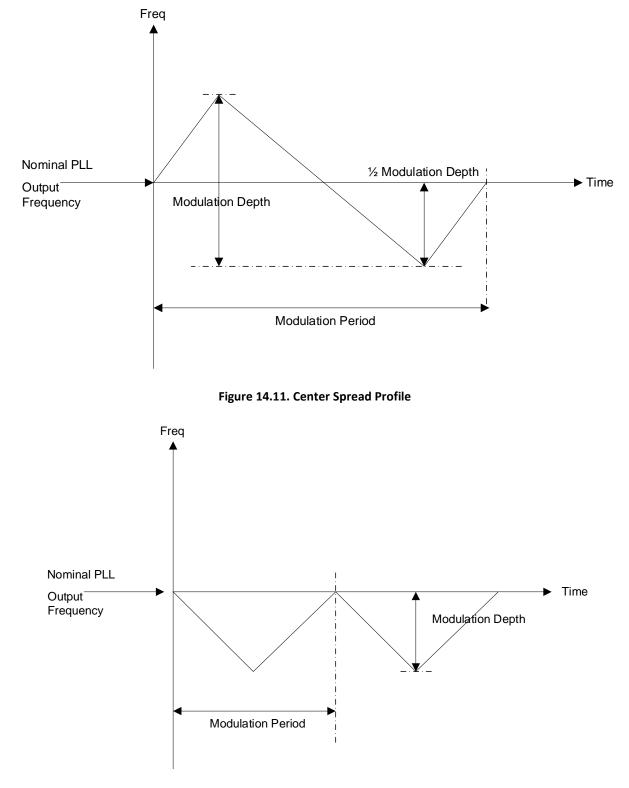

| 14.8. Spread Spectrum Clock Generation                                       |    |

| 14.9. Low Power Features                                                     |    |

| 14.9.1. Dynamic Clock Enable                                                 |    |

| 14.10. PLL Usage in IP Catalog                                               |    |

| 14.10.1. Configuration Tab                                                   |    |

| 14.10.2. PLL Frequency and Phase Configuration                               |    |

| Appendix A. Primary Clock Sources and Distribution                           |    |

| Appendix B. Pinout Rules for Clocking in Nexus Devices                       |    |

| Appendix C. PLL LMMI Operation                                               |    |

| PLL Architecture                                                             |    |

| LMMI Register Map                                                            |    |

| References                                                                   |    |

| Technical Support Assistance                                                 |    |

| Revision History                                                             |    |

|                                                                              |    |

## **Figures**

| Figure 3.1. CrossLink-NX and Certus-NX Clocking Structure                                            | 9  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 3.2. CertusPro-NX Clocking Structure                                                          | 10 |

| Figure 3.3. MachXO5-NX Clocking Structure                                                            | 10 |

| Figure 3.4. CrossLink-NX-33 and CrossLink-NX-33U Clocking Structure                                  | 11 |

| Figure 6.1. Primary Clock Routing Architecture for CrossLink-NX, Certus-NX, and MachXO5-NX           | 14 |

| Figure 6.2. Primary Clock Routing Architecture for CertusPro-NX                                      |    |

| Figure 7.1. PCLKDIVSP Component Symbol                                                               | 16 |

| Figure 8.1. DCS_CMUX Structure for CrossLink-NX, Certus-NX, and MachXO5-NX                           |    |

| Figure 8.2. DCS_CMUX Structure for CertusPro-NX                                                      |    |

| Figure 8.3. DCS Logic Structure                                                                      |    |

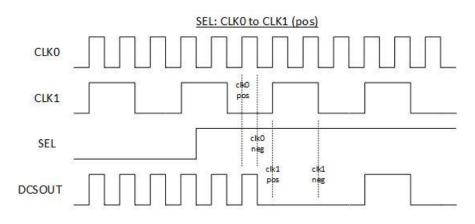

| Figure 8.4. Posedge DCS Switch from SEL: 0 => 1                                                      |    |

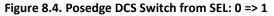

| Figure 8.5. Posedge DCS Switch from SEL: 1 => 0                                                      |    |

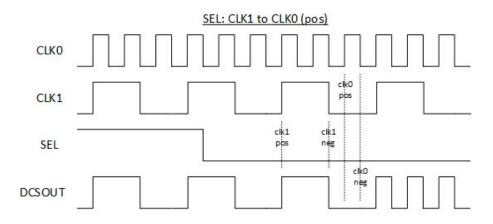

| Figure 8.6. Negedge DCS Switch from SEL: 0 => 1                                                      | 20 |

| Figure 8.7. SELFORCE = 1 DCS Clock Switch                                                            |    |

| Figure 8.8. DCS Component Symbol                                                                     | 21 |

| Figure 9.1. Glitchless DCC Functional Waveform                                                       | 24 |

| Figure 9.2. DCC Component Symbol                                                                     |    |

| Figure 10.1. OSCA Component Symbol                                                                   | 26 |

| Figure 11.1. Edge Clock Sources Per Bank                                                             |    |

| Figure 11.2. ECLKDIV Component Symbol                                                                |    |

| Figure 12.1. ECLKSYNC Component Symbol                                                               |    |

| Figure 12.2. ECLKSYNC Functional Waveform                                                            |    |

| Figure 13.1. Gated Clock to the Primary Clock Routing                                                |    |

| Figure 13.2. Gated Clock to Small Logic Domain                                                       |    |

| Figure 14.1. Nexus PLL Block Diagram                                                                 |    |

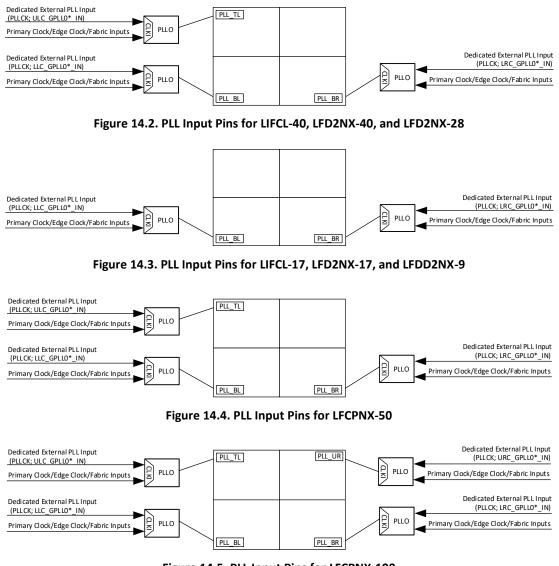

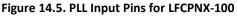

| Figure 14.2. PLL Input Pins for LIFCL-40, LFD2NX-40, and LFD2NX-28                                   |    |

| Figure 14.3. PLL Input Pins for LIFCL-17, LFD2NX-17, and LFDD2NX-9                                   |    |

| Figure 14.4. PLL Input Pins for LFCPNX-50                                                            |    |

| Figure 14.5. PLL Input Pins for LFCPNX-100                                                           | 36 |

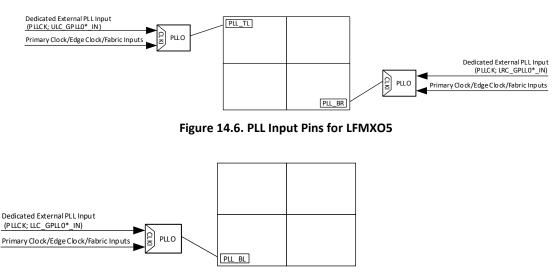

| Figure 14.6. PLL Input Pins for LFMXO5                                                               |    |

| Figure 14.7. PLL Input Pins for LIFCL-33 and LIFCL-33U                                               |    |

| Figure 14.8. PLL Component Instance                                                                  | 38 |

| Figure 14.9. RST Input Timing Diagram                                                                |    |

| Figure 14.10. PLL Phase Shifting Using the PHASESTEP Signal                                          |    |

| Figure 14.11. Center Spread Profile                                                                  |    |

| Figure 14.12. Down Spread Profile                                                                    |    |

| Figure 14.13. Dynamic Clock Enable for PLL Outputs                                                   |    |

| Figure 14.14. IP Catalog Main Window for PLL Module                                                  |    |

| Figure 14.15. Nexus PLL Frequency Configuration in General Tab                                       |    |

| Figure 14.16. Nexus PLL Optional Ports Configuration Tab                                             |    |

| Figure A.1. Nexus Primary Clock Sources and Distribution, LIFCL-40, LFD2NX-40, and LFD2NX-28 Devices |    |

| Figure A.2. Nexus Primary Clock Sources and Distribution, LIFCL-17, LFD2NX-17, and LFDD2NX-9 Devices |    |

| Figure A.3. Nexus Primary Clock Sources and Distribution, LFCPNX-50 Devices                          |    |

| Figure A.4. Nexus Primary Clock Sources and Distribution, LFCPNX-100 Devices                         |    |

| Figure A.5. Nexus Primary Clock Sources and Distribution, LIFCL-33 and LIFCL-33U Devices             | 57 |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Tables

| 8   |

|-----|

| .16 |

| .16 |

| .21 |

| .22 |

| .25 |

| .25 |

| .26 |

| .27 |

| .30 |

| .30 |

| .32 |

| .32 |

| .39 |

| .41 |

| .42 |

| .42 |

| .42 |

| .49 |

| .51 |

| .58 |

| .59 |

| .59 |

| .61 |

|     |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Acronyms in This Document

| A list of acron | yms used in | this document. |

|-----------------|-------------|----------------|

|-----------------|-------------|----------------|

| Acronym | Definition                      |  |

|---------|---------------------------------|--|

| CIB     | Common Interface Block          |  |

| DCC     | Dynamic Clock Control           |  |

| DCS     | Dynamic Clock Select            |  |

| DDR     | Double Data Rate                |  |

| DLL     | Delay Locked Loop               |  |

| DTR     | Digital Temperature Readout     |  |

| GSR     | Global Set Reset                |  |

| LMMI    | Lattice Memory Mapped Interface |  |

| MIB     | Memory Interface Block          |  |

| PLC     | Programmable Logic Cell         |  |

| PLL     | Phase Locked Loop               |  |

| SED     | Soft Error Detect               |  |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 1. Introduction

This user guide describes the clock resources available in the Lattice Nexus<sup>™</sup> Platform architecture, which includes CrossLink<sup>™</sup>-NX, Certus<sup>™</sup>-NX, Certus<sup>Pro<sup>™</sup></sup>-NX, and MachXO5<sup>™</sup>-NX product families.

The details are provided for Primary Clocks, Edge Clocks, PLLs, the Internal Oscillator, and clocking elements such as Clock Dividers, Clock Multiplexers, and Clock Stop Blocks available in the Nexus device.

The number of PLLs, Edge Clocks, and Clock Dividers for each device is listed in Table 1.1.

| Parameter                                 | Description                                                                 | LIFCL-17<br>LFD2NX-17<br>LFD2NX-9 | LIFCL-33<br>LIFCL-33U | LIFCL-40<br>LFD2NX-40<br>LFD2NX-28 | LFCPNX-50 | LFCPNX-100 | LFMXO5 |

|-------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------|-----------------------|------------------------------------|-----------|------------|--------|

| Number of<br>PLLs                         | General purpose Phase Locked<br>Loops.                                      | 2                                 | 1                     | 3                                  | 3         | 4          | 2      |

| Number of<br>Edge Clocks                  | Edge Clocks for high-speed<br>interfaces.                                   | 12                                | 12                    | 12                                 | 12        | 12         | 8      |

| Number of<br>Edge Clock<br>Dividers       | Edge Clock Dividers for high-<br>speed interfaces.                          | 12                                | 12                    | 12                                 | 12        | 12         | 8      |

| Number of<br>Primary<br>Clock<br>Dividers | Programmable Primary Clock<br>dividers for domain crossing<br>applications. | 1                                 | 1                     | 1                                  | 2         | 2          | 1      |

| Number of<br>DDRDLLs                      | DDRDLL used for DDR memory<br>and High Speed I/O interfaces                 | 2                                 | 2                     | 2                                  | 2         | 2          | 2      |

Table 1.1. Number of PLLs, Edge Clocks, and Clock Dividers

It is very important to validate the device pinout using the Lattice Radiant<sup>™</sup> tool to avoid implementation issues.

## 2. Clock/Control Distribution Network

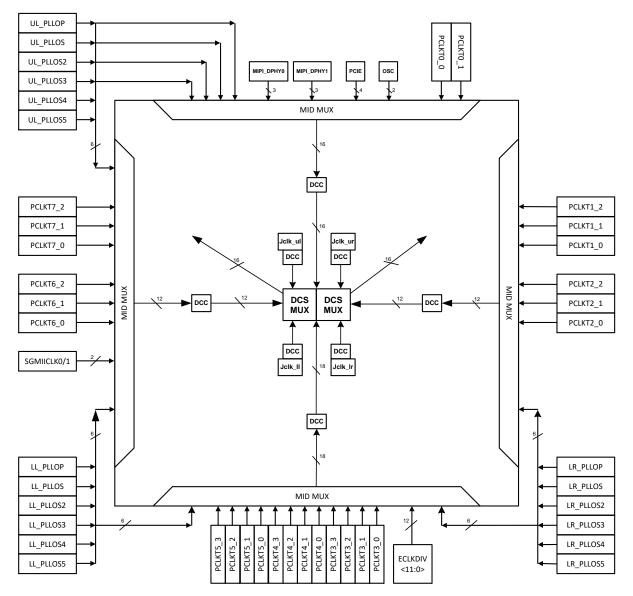

Nexus devices provide global clock distribution in the form of global primary clocks. The device is organized into clock regions; each clock region can accommodate 16 primary clocks. For CrossLink-NX, Certus-NX, and MachXO5-NX, there are two clock regions and for CertusPro-NX there are four clock regions. There is a maximum of 64 unique clock input sources. The Nexus primary clocking structure is Edge Clock rich and contains generous low-skew Primary clock resources.

## 3. Nexus Top-Level View

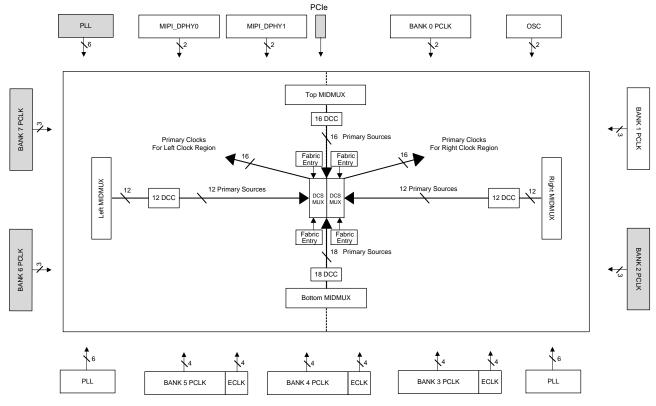

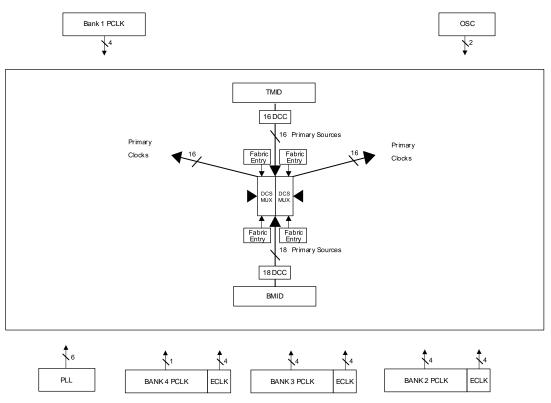

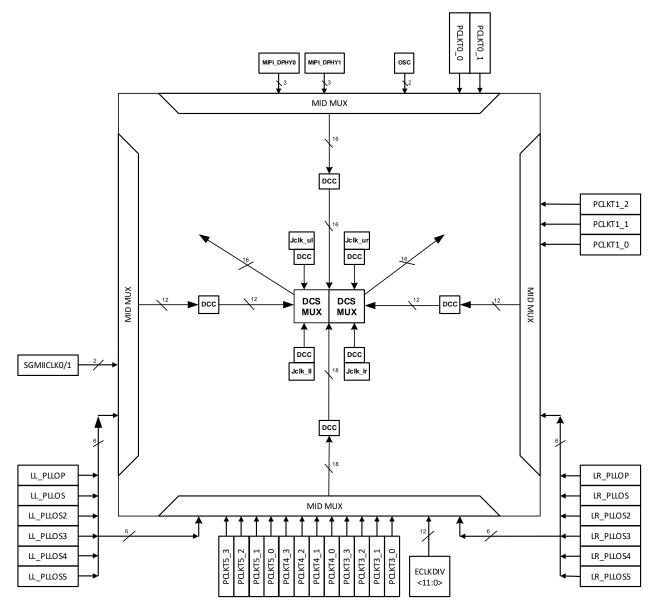

A top-level view of the major clocking resources for the CrossLink-NX and Certus-NX devices are shown in Figure 3.1. The shaded blocks (PCIe<sup>®</sup>, upper left PLL, and I/O Bank 2/Bank 6/Bank 7) are not available in the LIFCL-17, LFD2NX-17, and LFD2NX-9 devices. The MIPI\_DPHY0 and MIPI\_DPHY1 on the top are only available for the CrossLink-NX family.

Figure 3.1. CrossLink-NX and Certus-NX Clocking Structure

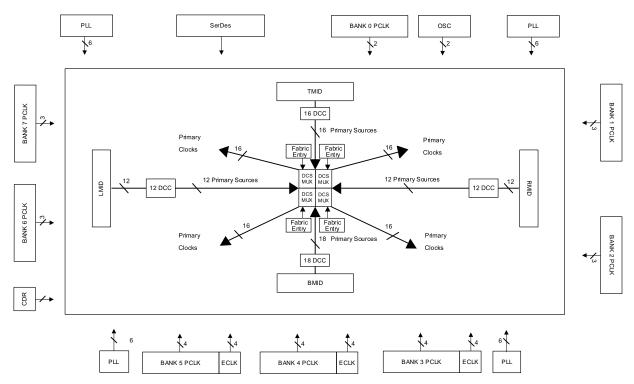

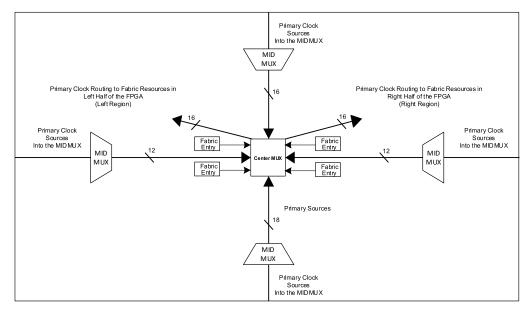

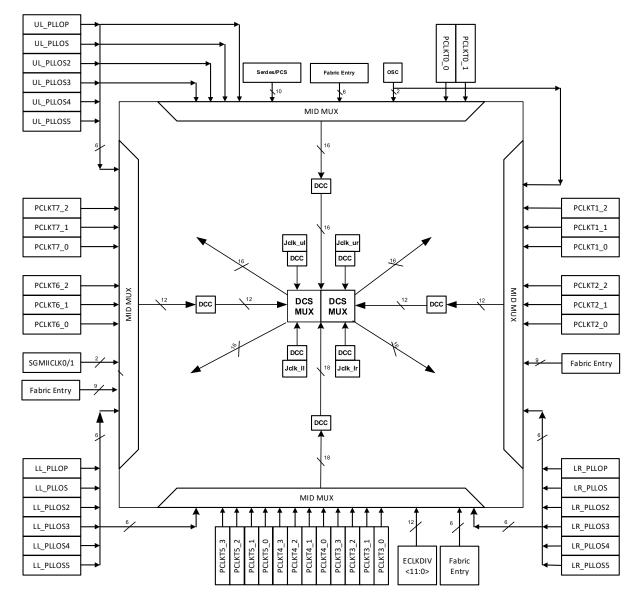

A top-level view of the major clocking resources for the CertusPro-NX devices are shown in Figure 3.2. The Upper Right PLL is only for LFCPNX-100.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 3.2. CertusPro-NX Clocking Structure

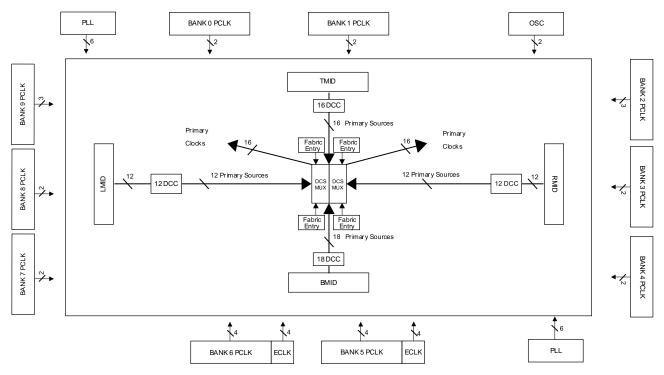

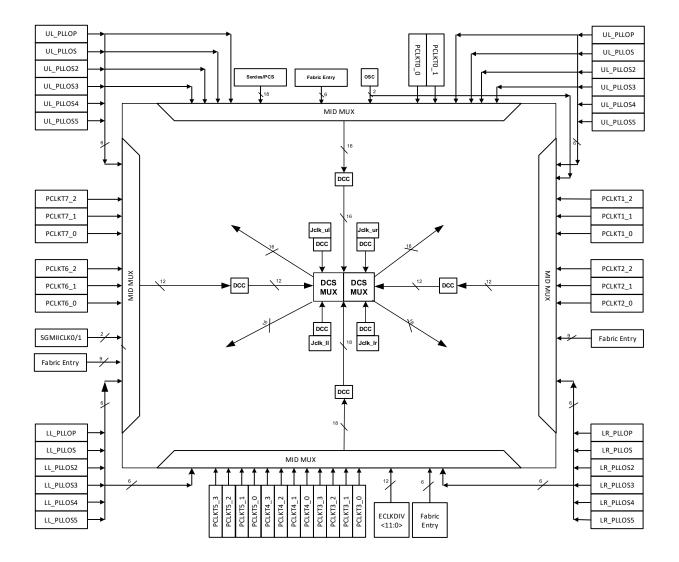

A top-level view of the major clocking resources for the MachXO5-NX devices is shown in Figure 3.3.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

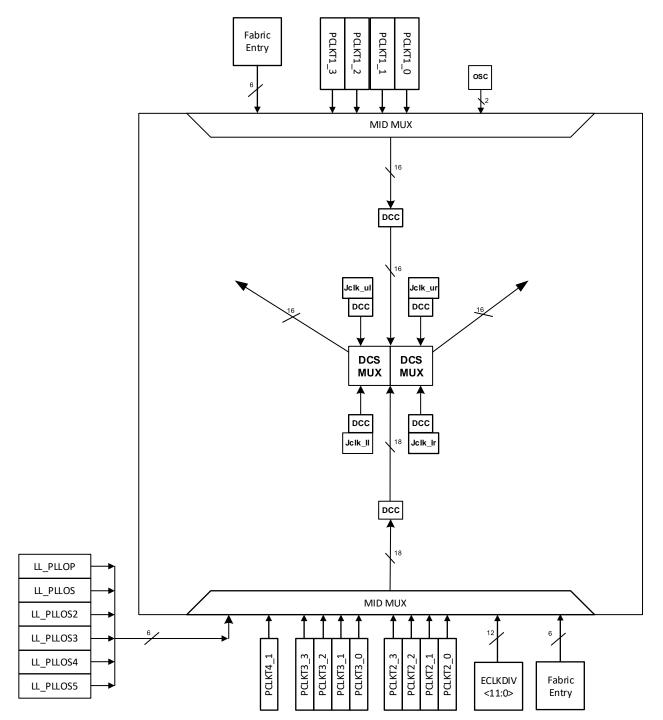

A top-level view of the major clocking resources for the CrossLink-NX-33 and CrossLink-NX-33U devices are shown in Figure 3.4.

Figure 3.4. CrossLink-NX-33 and CrossLink-NX-33U Clocking Structure

## 4. Clocking Architecture Overview

This section provides a brief overview of the clocking structure, elements, and PLL. Greater detail is provided starting with the Appendix A. Primary Clock Sources and Distribution and Appendix B. Pinout Rules for Clocking in Nexus Devices section.

## 4.1. Primary Clock Network

Up to 32 primary clocks (for CrossLink-NX, CrossLink-NX-33, CrossLink-NX-33U, Certus-NX, and MachXO5-NX) or 64 primary clocks (for CertusPro-NX) can be selected from up to 64 Primary Clock Sources (PLLs, External Inputs, SerDes, and others) and routed to the Primary Clock Network.

The Primary Clock Network provides low-skew, high fan-out clock distribution to all synchronous elements in the FPGA fabric. The Primary Clock Network is divided into two clocking regions (for CrossLink-NX, CrossLink-NX-33, CrossLink-NX-33U, Certus-NX, and MachXO5-NX) or four clocking regions (for CertusPro-NX), each region associated with a DCS\_CMUX. Each of these regions has 16 clocks that can be distributed to the fabric in the region. Initially, the Lattice Radiant software automatically routes each clock region; up to a maximum of 16 clocks. The user can change how the clocks are routed by specifying a preference in the Lattice Radiant project constraints file to locate the clock to specific region.

## 4.2. Edge Clock Network

Edge Clocks are low skew, high speed clock resources used to clock data into/out of the I/O logic of Nexus devices. There are four Edge Clocks per bank located on the bottom side of the device.

## 5. Overview of Clocking Components

## 5.1. Edge Clock Dividers (ECLKDIV)

Edge Clock dividers are provided to create the divided down clocks used for the I/O Mux/DeMux gearing logic (SCLK inputs of DDR I/O) and they drive the Primary Clock network. There are twelve Edge Clock Dividers on the Nexus device.

## 5.2. Primary Clock Divider (PCLKDIVSP)

For CrossLink-NX, Certus-NX, and MachXO5-NX, one programmable Primary Clock Divider is provided to create the divided down clocks. For CertusPro-NX, two programmable Primary Clock Dividers are available.

## 5.3. Dynamic Clock Select (DCS)

The dynamic clock select provides run-time selectable glitchless or non-glitchless operation between two independent clock sources to the primary clock network. This clock select allows the selection of clock sources without leaving the dedicated clock resources in the device. There is one dynamic clock select block on the CrossLink-NX, Certus-NX, and MachXO5-NX devices, and there are two dynamic clock select blocks on the CertusPro-NX device.

## 5.4. Dynamic Clock Control (DCC)

Dynamic Clock Control allows dynamic clock to enable and disables the MIDMUX Feed Line and the four special common interface block (CIB) clocks from the core. When a Feed Line is disabled, all the logic and clock signals that are fed by this Feed Line do not toggle. Hence, it reduces the overall dynamic power consumption of the device.

## 5.5. Edge Clock Sync (ECLKSYNC)

The Nexus devices have dynamic edge clock synchronization control (ECLKSYNC) which allows each edge clock to be disabled or enabled glitchlessly from core logic if desired. This allows the user to synchronize the edge clock to an event or external signal, if desired. It also allows the design to dynamically disable a clock and its associated logic in the design when it is not needed and thus save power.

## 5.6. Oscillator (OSC)

An internal programmable rate oscillator is provided. The oscillator can be used for FPGA configuration, Soft Error Detect (SED), and as a user logic clock source that is available after FPGA configuration. There is one OSCA on the Nexus device. The oscillator clock output is routed directly to primary clocking.

The oscillator output is not a high-accuracy clock, having a +/- 7% variation in its output frequency. It is mainly used for circuits that do not require a high degree of clock accuracy. Examples of usage are asynchronous logic blocks such as a timer or reset generator, or other logic that require a constantly running clock.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 6. Primary Clocks

### 6.1. Primary Clock Sources

The primary clock network has multiple inputs, called primary clock sources, which can be routed directly to the primary clock routing to clock the FPGA fabric.

The primary clock sources that can connect to the primary clock routing are:

- Dedicated Clock Input Pins

- PLL Outputs

- PCLKDIVSP/ECLKDIV Outputs

- Internal FPGA Fabric Entries (with minimum general routing)

- SGMII-CDR, SerDes/PCS clocks

- OSC Clock

All potential primary clock sources are multiplexed prior to going to the primary clock routing by a MIDMUX. There are 58 MIDMUX connections and four FPGA fabric connections, 62 total, routed to a multiplexor in the center of the chip called the centermux. From the centermux, primary clocks are selected and distributed to the FPGA fabric.

The maximum number of unique clock sources is:

18 bottom MIDMUX sources + 16 top MIDMUX sources + 12 left MIDMUX sources + 12 right MIDMUX sources + 4 direct FPGA fabric entry points (from general routing) = 62.

The basic clocking structure is shown in Figure 3.1 and Figure 3.2, elaborated in Appendix A. Primary Clock Sources and Distribution.

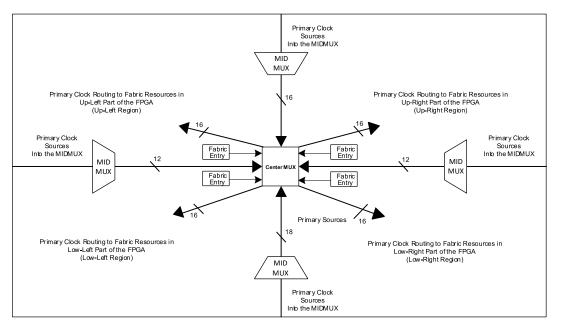

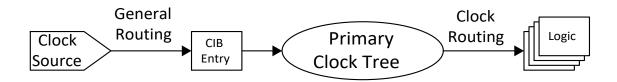

## 6.2. Primary Clock Routing

The primary clock routing network is made up of low skew clock routing resources with connectivity to every synchronous element of the device. Primary clock sources are selected at the MIDMUX, then selected in the centermux and distributed on the primary clock routing to clock the synchronous elements in the FPGA fabric. For CrossLink-NX, Certus-NX, and MachXO5-NX, the primary clock routing network is divided into left and right regions. Figure 6.1 is the simplified view of Figure 3.1. For CertusPro-NX, the primary clock routing network is divided into four regions, up-left, up-right, low-left, and low-right. Figure 6.2 is the simplified view of Figure 3.2.

Figure 6.1. Primary Clock Routing Architecture for CrossLink-NX, Certus-NX, and MachXO5-NX

Figure 6.2. Primary Clock Routing Architecture for CertusPro-NX

The centermux can source up to 16 independent primary clocks per region, which can clock the logic located in that region. The centermux can also route each clock source to all regions. The Lattice Radiant software automatically routes a primary clock to the regions in the FPGA.

### 6.3. Dedicated Clock Inputs

The Nexus device has dedicated pins called PCLK pins, to bring an external clock source into the FPGA and allow them to be used as FPGA primary clocks. These inputs route directly to the Primary clock network and to Edge Clock routing resources. A dedicated PCLK clock pin must always be used to route an external clock source to FPGA and I/O logic.

If an external input clock is being sourced to a PLL, then in most cases, the input clock should use a dedicated PLL input pin as described in Dedicated PLL Inputs section. SerDes reference clocks also have dedicated SerDes reference clock pins. The Nexus device allows a PLL reference clock or a SerDes reference clock to come from an external Primary Clock (PCLK) pin and route through the Primary clock network to drive the reference clock to the SerDes or the input of a PLL. See Appendix A for more details.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 7. Primary Clock Divider (PCLKDIVSP)

Inside the centermux, one (for CrossLink-NX, Certus-NX, and MachXO5-NX) or two (for CertusPro-NX) Primary Clock Dividers are available. Each Primary Clock Divider provides the following functionalities:

- PCLK Divider supports ÷2, ÷4, ÷8, ÷16, ÷32, ÷64, and ÷128. When PCLK divider is bypassed, it is ÷1 mode.

- PCLK Divider can be reset by global Reset signals and sleep mode control signals. The global reset can be disabled by a configuration bit.

- PCLK Divider supports user Local Reset through CIB port.

- The reset is Asynchronous assert and synchronous de-assert. The divider output starts at the next cycle after the reset is synchronously released.

- Allow GSR activity to be ignored during device power up by gating this signal with internal DONE.

- When exiting from sleep mode, the retention registers are released from the asynchronous reset control.

## 7.1. PCLKDIVSP Component Definition

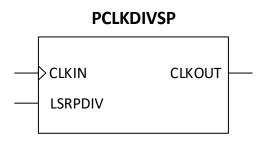

The PCLKDIVSP component can be instantiated in the source code of a design as defined in this section. Figure 7.1, Table 7.1, and Table 7.2 define the PCLKDIVSP component. Verilog and VHDL instantiations are included.

Figure 7.1. PCLKDIVSP Component Symbol

| Port Name | I/O | Description                                                                                                                                    |

|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKIN     | Ι   | Primary Clock Input                                                                                                                            |

| LSRPDIV   | I   | Local Reset — Active High, asynchronously forces all outputs low.<br>LSRPDIV = 0 Clock outputs are active<br>LSRPDIV = 1 Clock outputs are OFF |

| CLKOUT    | 0   | Divide by 1, 2, 4, 8, 16, 32, 64, or 128 Output Port                                                                                           |

| Table 7.2. PCLKDIVSP | Component Attribute Definition |

|----------------------|--------------------------------|

|----------------------|--------------------------------|

| Name        | Value                                  | Default | Description                          |

|-------------|----------------------------------------|---------|--------------------------------------|

| DIV_PCLKDIV | X1, X2, X4, X8, X16, X32, X64,<br>X128 | X1      | Primary Clock Divide Ratio Selection |

| GSR         | ENABLE<br>DISABLE                      | ENABLED | GSR ENABLE/DISABLE Selection         |

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### 7.2. PCLKDIVSP Usage in VHDL

#### **Component Instantiation**

```

Library lattice;

use lattice.components.all;

```

#### **Component and Attribute Declaration**

```

component PCLKDIVSP

generic (DIV_PCLKDIV : string;

GSR : string);

port (CLKIN : in STD_LOGIC;

LSRPDIV : in STD_LOGIC;

CLKOUT : out STD_LOGIC);

end component;

```

#### **PCLKDIVSP** Instantiation

```

attribute DIV_PCLKDIV : string;

attribute DIV_PCLKDIV of I1 : label is "X1";

attribute GSR : string;

attribute GSR of I1 : label is "DISABLED";

```

```

I1: PCLKDIVSP

generic map (DIV_PCLKDIV => "X2",

GSR => "DISABLED")

port map (CLKIN => CLKIN,

LSRPDIV => LSRPDIV,

CLKOUT => CLKOUT);

```

### 7.3. PCLKDIVSP Usage in Verilog

#### **Component and Attribute Declaration**

```

module PCLKDIVSP (CLKIN, LSRPDIV, CLKOUT);

parameter DIV_PCLKDIV = "X2"; // "X1", "X2", "X4", "X8", "X16", "X32", "X64", "X128"

parameter GSR = "DISABLED"; // "ENABLED", "DISABLED"

input CLKIN, LSRPDIV;

output CLKOUT;

endmodule

PCLKDIVSP Instantiation

defparam I1.DIV_PCLKDIV = "X2";

defmamare I1 CSR = "DISABLED";

```

defparam I1.GSR = "DISABLED";

PCLKDIVSP I1 (

.CLKIN (CLKIN),

.LSRPDIV (LSRPDIV),

.CLKOUT (CLKOUT));

## 8. Dynamic Clock Select (DCS)

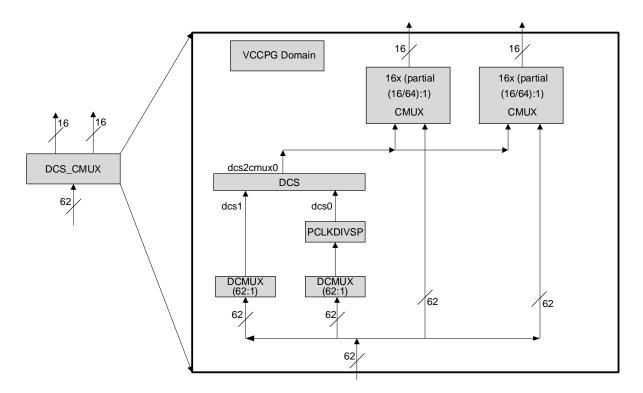

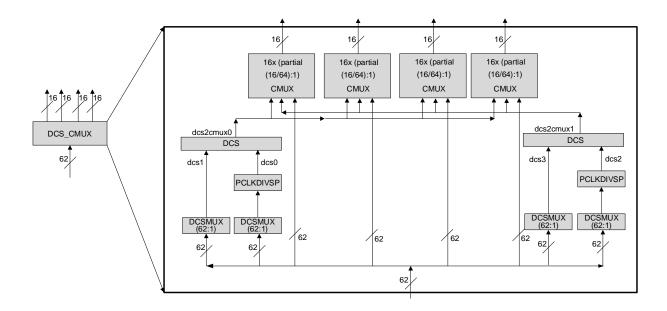

One (for CrossLink-NX, Certus-NX, and MachXO5-NX) or two (for CertusPro-NX) dynamic clock select (DCS) blocks are located at the center of the PLC array, which can drive to any or all the regions. The DCS\_CMUX Structures are shown in Figure 8.1 and Figure 8.2.

Figure 8.1. DCS\_CMUX Structure for CrossLink-NX, Certus-NX, and MachXO5-NX

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

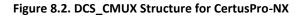

The DCS block allows dynamic and glitchless selection between two PCLK clock sources. The DCS block shares the same clock resource as any PCLK CMUX. This way the DCS function can be performed on any two primary clock sources. The inputs to the DCS block come from all the outputs of MIDMUXs and local routing that is located at the center of the PLC array. The output of the DCS is connected to the inputs of Primary Clock Center MUXs. The DCS logic structure is shown in Figure 8.3.

Figure 8.3. DCS Logic Structure

The DCSMODE attribute sets the behavior of the DCS output. The DCS attributes are described in Table 8.2.

### 8.1. DCS Timing Diagrams

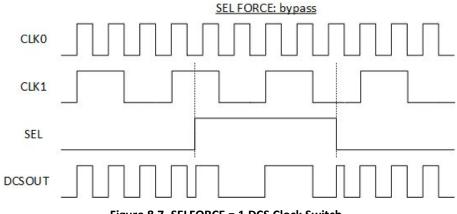

The DCS block allows dynamic and glitchless selection between two PCLK clock sources. The DCS block shares the same clock resource as any PCLK CMUX. Therefore, the DCS function can be performed on any two primary clock sources. Figure 8.4, Figure 8.5, and Figure 8.6 show the DCS in glitchless operation in conjunction with the DCSMODE attribute. Figure 8.7 shows the non-glitchless bypass operation scenario.

### 8.1.1. Functionality – posedge SEL switch

The selection switches from current clock to target clock. For posedge configuration, the latch state is low. Below is the sequence of events once SEL toggles:

- 1. Current clock must see posedge then negedge, then is deactivated.

- 2. Target clock must see posedge then negedge, then output is successfully switched over.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 8.5. Posedge DCS Switch from SEL: 1 => 0

#### 8.1.2. Functionality – negedge SEL switch

The selection switches from current clock to target clock. For negedge configuration, the latch state is high. Below is the sequence of events once SEL toggles:

- 1. Current clock must see negedge then posedge, then is deactivated.

- 2. Target clock must see negedge then posedge, then output is successfully switched over.

Figure 8.6. Negedge DCS Switch from SEL: 0 => 1

### 8.1.3. Functionality – bypass

When SELFORCE is high, the switch is in bypass mode. The output clock transitions immediately from the current clock to the target clock and may have glitches.

Figure 8.7. SELFORCE = 1 DCS Clock Switch

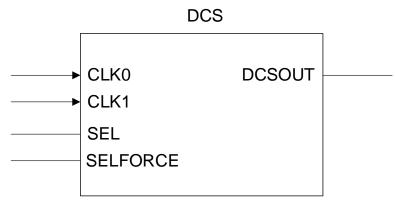

### 8.2. DCS Component Definition

The DCS component can be instantiated in the source code of a design as defined in this section.

#### **Table 8.1. DCS Component Port Definition**

| Port Name | I/O | Description                                           |  |

|-----------|-----|-------------------------------------------------------|--|

| CLKO      | Ι   | ock Input port 0 — Default                            |  |

| CLK1      | I   | ock Input port 1                                      |  |

| SEL       | I   | nput Clock Select                                     |  |

| SELFORCE  | I   | Selects Glitchless (0) or Non-Glitchless (1) behavior |  |

| DCSOUT    | 0   | Clock Output Port                                     |  |

Table 8.2 provides the behavior of the DCS output based on the setting of the *DCSMODE* attribute and the SELFORCE pin input. The SELFORCE pin is dynamic and can toggle during operation. The glitchless switching is only achievable when SELFORCE = 0.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Table 8.2. DCS – DCSMODE Attribute

| Attribute Name            | Attribute Value | Output  |         | Description                                  |

|---------------------------|-----------------|---------|---------|----------------------------------------------|

| Attribute Name            |                 | SEL = 0 | SEL = 1 | Description                                  |

|                           | VCC             | 1       | 1       | VCC                                          |

|                           | GND             | 0       | 0       | VSS                                          |

|                           | DCS             | CLK0    | CLK1    | Falling edge triggered, latched state is low |

|                           | DCS_1           | CLK0    | CLK1    | Rising edge triggered, latched state is high |

| DCSMODE<br>(SELFORCE = 0) | BUFGCECLK1      | 0       | CLK1    | SEL is active high, disabled output is low   |

|                           | BUFGCECLK1_1    | 1       | CLK1    | SEL is active high, disabled output is high. |

|                           | BUFGCECLKO      | CLK0    | 0       | SEL is active low, disabled output is low.   |

|                           | BUFGCECLK0_1    | CLK0    | 1       | SEL is active low, disabled output is high.  |

|                           | BUFO            | CLK0    | CLK0    | Buffer for CLK0                              |

|                           | BUF1            | CLK1    | CLK1    | Buffer for CLK1                              |

| SELFORCE = 1              | Non-Glitchless  | CLK0    | CLK1    | _                                            |

### 8.3. DCS Usage in VHDL

#### **Component Instantiation**

Library lattice; use lattice.components.all;

#### **Component and Attribute Declaration**

```

COMPONENT DCS

```

```

GENERIC(DCSMODE : string := "DCS");

PORT (CLK0 :IN STD_LOGIC;

CLK1 :IN STD_LOGIC;

SEL :IN STD_LOGIC;

SELFORCE :IN STD_LOGIC;

DCSOUT :OUT STD_LOGIC);

END COMPONENT;

```

#### **DCS** Instantiation

```

attribute DCSMODE : string;

attribute DCSMODE of DCSinst0 : label is "DCS";

I1: DCS

generic map(

DCSMODE => "DCS")

port map (

CLK0 => CLK0

,CLK1 => CLK1

,SEL => SEL

,SELFORCE => SELFORCE

,DCSOUT => DCSOUT);

```

## 8.4. DCS Usage in Verilog

#### **Component and Attribute Declaration**

module DCS(CLK0,CLK1,SEL,SELFORCE,DCSOUT);

input CLK0; input CLK1; input SEL; input SELFORCE; output DCSOUT; endmodule

#### **DCS Instantiation**

defparam DCSInst0.DCSMODE = "DCS"; DCS DCSInst0 ( .CLK0 (CLK0), .CLK1 (CLK1), .SEL (SEL), .SELFORCE (SELFORCE), .DCSOUT (DCSOUT));

## 9. Dynamic Clock Control (DCC)

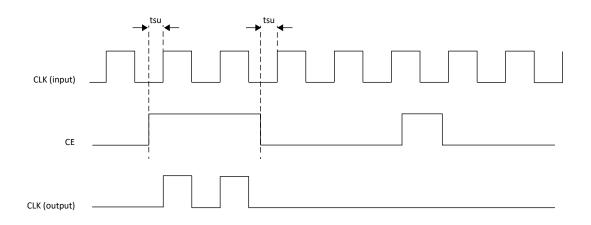

The Nexus device has a Dynamic Clock Control feature which allows internal logic to dynamically enable or disable the region primary clock network. This gating function does not create glitches or increase the clock latency to the primary clock network. Also, this dynamic clock control function can be disabled by a configuration memory fuse to always enable the primary clock network.

The DCC controls the clock sources from the Primary CLOCK MIDMUX before they are fed to the Primary Center MUXs that drive the region clock network. When a clock network is disabled, the power consumption of all the associated logic is greatly reduced.

The Nexus device clock architecture allows both DCC and DCS to function at the same time. Care must be taken when the clock source is used as input to the PLL. The DCC should remain enabled, otherwise if the PLL input clock stops toggling, the PLL loses locked and the PLL output clock also stops toggling.

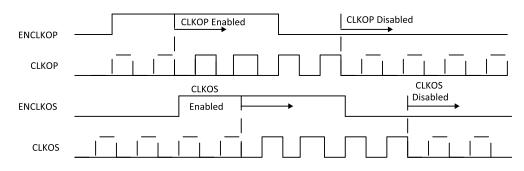

Figure 9.1. Glitchless DCC Functional Waveform

Dynamic Clock Control allows the four clocks from the FPGA fabric feeding to the MIDMUX be dynamically enabled and disabled. When a Feed Line is disabled, all the logic and clock signals that are fed by this Feed Line do not toggle. Hence, it reduces the overall dynamic power.

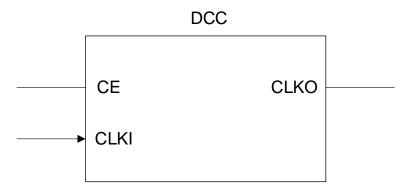

## 9.1. Component Definition

The DCC component can be instantiated in the source code of a design as defined in this section. Figure 9.2, Table 9.1, and Table 9.2 show the DCC definitions.

#### Figure 9.2. DCC Component Symbol

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### **Table 9.1. DCC Component Port Definition**

| Port Name | I/O | Description                                                                                           |

|-----------|-----|-------------------------------------------------------------------------------------------------------|

| CLKI      | Ι   | Clock Input port.                                                                                     |

| CE        | I   | Clock Enable port<br>— CE = 0 CLKO is disabled (CLKO = '0')<br>— CE = 1 CLKO is enabled (CLKO = CLKI) |

| CLKO      | 0   | Clock Output Port                                                                                     |

#### **Table 9.2. DCC Component Attribute Definition**

| Name  | Value  | Default | Description                                                                                                    |

|-------|--------|---------|----------------------------------------------------------------------------------------------------------------|

| DCCEN | 0<br>1 | 0       | Enables dynamic control.<br>"0": CLKO = CLKI regardless of the CE input.<br>"1": CLKO depends on the CE input. |

### 9.2. DCC Usage in VHDL

#### **Component Instantiation**

```

library lattice;

use lattice.components.all;

Component and Attribute Declaration

COMPONENT DCC

PORT (CLKI :IN STD_LOGIC;

CE :IN STD_LOGIC;

CLKO :OUT STD_LOGIC);

END COMPONENT;

```

#### **DCC** Instantiation

```

I1: DCC

port map (

CLKI => CLKI,

CE => CE,

CLKO => CLKO);

DCC Usage in Verilog

Component and Attribute Declaration

module DCC(CLKI,CE,CLKO);

input CLKI;

input CE;

output CLKO;

endmodule

```

### 9.3. DCC Usage in Verilog

#### **DCC** Instantiation

DCC DCSInst0 (

.CLKI (CLKI),

.CE (CE),

.CLK0 (CLKO));

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **10. Internal Oscillator (OSCA)**

The OSCA component performs multiple functions on the Nexus device. It is used for configuration, SED, as well as optionally in user mode. In user mode, the OSCA component has the following features:

- It permits a design to be fully self-clocked, as long as the quality of the OSCA component's silicon-based oscillator is adequate.

- If it is unused, it can be turned off for power savings.

- It has an input to dynamically control standby/normal operation.

- It has a direct connection to primary clock routing through the top MIDMUX. For CertusPro-NX, the right MIDMUX can also be used for the direct connection to primary clock routing.

- It can be configured for operation at a wide range of frequencies through the configuration bits.

### 10.1. OSCA Component Definition

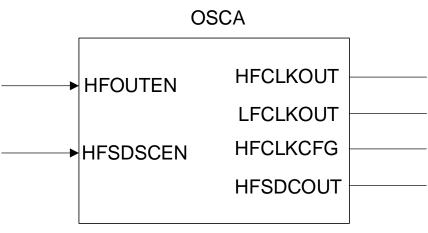

The OSCA component can be instantiated in the source code of a design as defined in this section. Figure 10.1 and Table 10.1 show the OSCA definitions.

Figure 10.1. OSCA Component Symbol

| Table 10.1. | <b>OSCA</b> Compo | nent Port Definition |

|-------------|-------------------|----------------------|

|-------------|-------------------|----------------------|

| Port Name | I/O | Description                                                               |  |

|-----------|-----|---------------------------------------------------------------------------|--|

| HFOUTEN   | Ι   | High Frequency User Clock Output Enable                                   |  |

| HFSDSCEN  | Ι   | High Frequency User Clock Output Enable                                   |  |

| HFCLKOUT  | 0   | 450 MHz with Programmable Divider (2~256) to User                         |  |

| HFSDCOUT  | 0   | 450 MHz with Programmable Divider (2~256) to User for SED/SEC Application |  |

| LFCLKOUT  | 0   | Low Frequency Clock Output; 32 kHz                                        |  |

| HFCLKCFG  | 0   | High Frequency Reference Clock; 450 MHz                                   |  |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Table 10.2. OSCA Component Attribute Definition

| Name           | Value    | Default  | Description                                   |

|----------------|----------|----------|-----------------------------------------------|

| HF_CLK_DIV     | 0000001  | 0000001  | User-assignable HF oscillator output divider  |

|                | 11111111 |          | configuration (div2~div256)                   |

|                | 0000001  |          | User-assignable HF oscillator output divider  |

| HF_SED_SEC_DIV | ~        | 0000001  | configuration (div2~div256)                   |

|                | 11111111 |          |                                               |

| HF OSC EN      | DISABLED | DISABLED | HF oscillator enable, controlled by the user  |

| TIF_03C_EN     | ENABLED  | DISABLED | The oscillator enable, controlled by the user |

| LF OUTPUT EN   | DISABLED | DISABLED | Low frequency clock output enable             |

|                | ENABLED  | DISABLED | Low frequency clock output enable             |

### 10.2. OSCA Usage in VHDL

#### **Component Instantiation**

```

Library lattice;

use lattice.components.all;

```

#### **Component and Attribute Declaration**

#### **OSCA** Instantiation

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 10.3. OSCA Usage in Verilog

#### **OSCA** Instantiation

```

OSCA I1 #(

.HF_CLK_DIV ("1"), //DIV = 2

.HF_SED_SEC_DIV ("1"), //DIV = 2

.HF_OSC_EN ("ENABLED"),

.LF_OUTPUT_EN ("ENABLED"),

)(

.HFOUTEN (HFOUTEN ),

.HFSDSCEN (HFSDSCEN),

.HFCLKOUT (HFSDSCEN),

.HFCLKOUT (HFCLKOUT),

.HFCLKCFG (HFCLKCFG),

.HFSDCOUT (HFSDCOUT)

);

```

## 11. Edge Clocks

Each Nexus device bottom I/O bank has four ECLK resources. There are three I/O banks at the bottom of the device. These clocks, which have low injection time and skew, are used to clock I/O registers. Edge Clock resources are designed for high-speed I/O interfaces with high fan-out capability. See Figure 3.1 for ECLK locations and connectivity.

The sources of Edge Clocks are:

- Dedicated Clock (PCLK) pins

- DLLDEL output

- Bottom PLL outputs (CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, and CLKOS5)

- ECLK Bridge

- Internal nodes

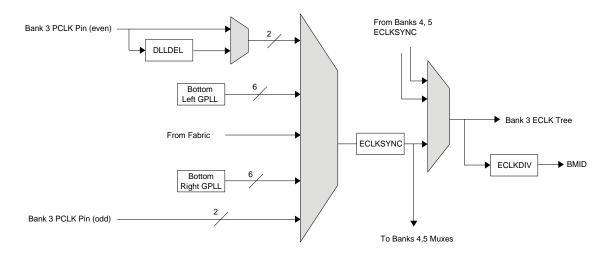

The Nexus device has Edge Clock (ECLK) at the bottom of the device. There are four ECLK networks per I/O bank. ECLK Input MUX collects all clock sources available as shown in Figure 11.1. There are three ECLK Input MUXs, one for each I/O bank on the bottom side of the device. Each of these MUX generates total of four ECLK Clock sources for each I/O bank. Each ECLK network from one I/O bank can be bridged to another I/O bank from a wider bus if it is needed.

Figure 11.1. Edge Clock Sources Per Bank

## 11.1. Edge Clock Dividers (ECLKDIV)

There are twelve Edge Clock dividers available in the Nexus device, four for each I/O bank at the bottom of the device. The Clock Divider provides a single divided output with available divide values of 2, 3.5, 4, or 5. The inputs to the Clock Dividers are the Edge Clocks, PLL outputs and Primary Clock Input pins. The outputs of the Clock Divider drive the primary clock network and are mainly used for DDR I/O domain crossing.

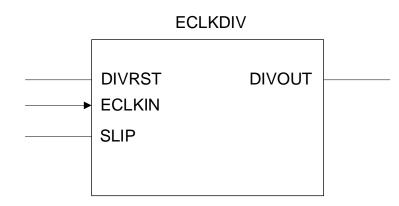

## **11.2. ECLKDIV Component Definition**

The ECLKDIV component can be instantiated in the source code of a design as defined in this section. Figure 11.2, Table 11.1, and Table 11.2 define the ECLKDIV component. Verilog and VHDL instantiations are included.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 11.2. ECLKDIV Component Symbol

#### Table 11.1. ECLKDIV Component Port Definition

| Port Name | I/O | Description                                                                                                                                  |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| ECLKIN    | I   | Edge Clock Input                                                                                                                             |

| DIVRST    | I   | Reset input — Active High, asynchronously forces all outputs low.<br>DIVRST = 0 Clock outputs are active<br>DIVRST = 1 Clock outputs are OFF |

| SLIP      | I   | Signal is used for word alignment. When enabled it slips the output one cycle relative to the input clock.                                   |

| DIVOUT    | 0   | Divide by 1, 2, 3.5, 4, or 5 Output Port                                                                                                     |

#### Table 11.2. ECLKDIV Component Attribute Definition

| Name     | Value                                 | Default | Description                               |

|----------|---------------------------------------|---------|-------------------------------------------|

| GSR      | ENABLED<br>DISABLED                   | ENABLED | GSR ENABLE/DISABLE Selection              |

| ECLK_DIV | DISABLE<br>"2"<br>"3P5"<br>"4"<br>"5" | DISABLE | ECLK DIVIDE Ratio selection ("3P5" = 3.5) |

The SLIP input is intended for use with high-speed data interfaces such as DDR or 7:1 LVDS Video.

### 11.3. ECLKDIV Usage in VHDL

### **Component Instantiation**

```

Library lattice;

use lattice.components.all;

Component and Attribute Declaration

```

```

component ECLKDIV

Generic (ECLK_DIV : string;

GSR : string);

Port (DIVRST : in STD_LOGIC;

ECLKIN : in STD_LOGIC;

SLIP : in STD_LOGIC;

DIVOUT : out STD_LOGIC);

end component;

```

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### **ECLKDIV** Instantiation

attribute ECLK\_DIV : string; attribute ECLK\_DIV of I1 : label is "2.0"; attribute GSR : string; attribute GSR of I1 : label is "DISABLED";

### 11.4. ECLKDIV Usage in Verilog

#### **Component and Attribute Declaration**

```

module ECLKDIV (DIVRST, ECLKIN, SLIP, DIVOUT);

parameter ECLK_DIV = "2.0"; // "2.0", "3.5"

parameter GSR = "DISABLED"; // "ENABLED", "DISABLED"

input DIVRST, ECLKIN, SLIP;

```

```

output DIVOUT;

endmodule

```

#### **ECLKDIV** Instantiation

```

defparam I1.ECLK_DIV = "2.0";

defparam I1.GSR = "DISABLED";

ECLKDIV I1 (

.DIVRST (DIVRST),

.ECLKIN (ECLKIN),

.SLIP (SLIP),

.DIVOUT (DIVOUT));

```

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

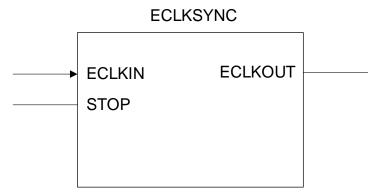

## 12. Edge Clock Synchronization (ECLKSYNC)

Nexus devices have a dynamic Edge Clock synchronization control (ECLKSYNC) which allows each Edge Clock to be disabled or enabled glitchlessly from core logic if desired. This allows the user to synchronize the Edge Clock to an event or external signal if desired. It also allows the design to dynamically disable a clock and its associated logic in the design when it is not needed and thus, save power. Applications such as DDR2, DDR3, and 7:1 LVDS for display use this component for clock synchronization.

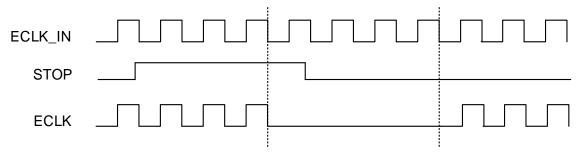

## 12.1. ECLKSYNC Component Definition

The ECLKSYNC component can be instantiated in the source code of a design as defined in this section. Asserting the STOP control signal has the ability to stop the Edge Clock to synchronize the signals derived from ECLK and used in high-speed DDR mode applications such as DDR memory, generic DDR, and 7:1 LVDS.

Control signal STOP is synchronized with ECLK when asserted. When control signal STOP is asserted, the clock output is forced to low after the fourth falling edge of the input ECLKI. When the STOP signal is released, the clock output starts to toggle at the fourth rising edge of the input ECLKI clock.

Figure 12.1 and Table 12.1 show the ECLKSYNC component definition.

Figure 12.1. ECLKSYNC Component Symbol

| Table 12.1. | ECLKSYNC | Component | Port | Definition |

|-------------|----------|-----------|------|------------|

|-------------|----------|-----------|------|------------|

| Port Name | I/O | Description                       |  |

|-----------|-----|-----------------------------------|--|

| ECLKIN    | Ι   | Clock Input port.                 |  |

|           |     | Control signal to stop Edge Clock |  |

| STOP      | I   | • STOP = 0 Clock is Active        |  |

|           |     | • STOP = 1 Clock is Off           |  |

| ECLKOUT   | 0   | Clock Output Port                 |  |

#### Table 12.2. ECLKSYNC Component Attribute Definition

| Name    | Value   | Default | Description                   |

|---------|---------|---------|-------------------------------|

| STOP EN | DISABLE | DISABLE | STOP ENABLE/DISABLE Selection |

| STOP_EN | ENABLE  | DISABLE | STOP ENABLE/DISABLE Selection |

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 12.2. ECLKSYNC Usage in VHDL

#### **Component Instantiation**

```

Library lattice;

use lattice.components.all;

```

#### **Component and Attribute Declaration**

```

COMPONENT ECLKSYNC

PORT (ECLKIN :IN STD_LOGIC;

STOP :IN STD_LOGIC;

ECLKOUT :OUT STD_LOGIC);

END COMPONENT;

```

#### **ECLKSYNC** Instantiation

```

I1: ECLKSYNC

port map (

ECLKIN => ECLKIN,

STOP => STOP,

ECLKOUT => ECLKOUT);

```

### 12.3. ECLKSYNC Usage in Verilog

#### **Component and Attribute Declaration**

```

module ECLKSYNC (ECLKIN,STOP,ECLKOUT);

input ECLKIN;

input STOP;

output ECLKOUT;

endmodule

```

#### **ECLKSYNC** Instantiation

```

ECLKSYNC ECLKSYNCInst0 (

.ECLKIN (ECLKIN),

.STOP (STOP),

.ECLKOUT (ECLKOUT));

```

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

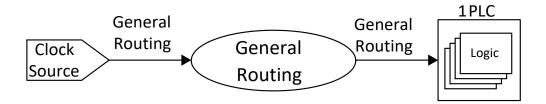

## **13. General Routing for Clocks**

The Nexus device architecture supports the ability to use general routing for a clock. This capability is intended to be used for small areas of the design to allow additional flexibility in linking dedicated clocking resources and building very small clock trees. General routing cannot be used for Edge Clocks for applications that use the DDR registers in the I/O components of the FPGA.

Software limits the distance of a general routing based (gated) clock to one PLC in distance to a primary clock entry point. If the software cannot place the clock gating logic close enough to a primary clock entry point, the error below occurs:

• ERROR-par – Unable to reach a primary clock entry point for general route clock <net> in the minimum required distance of one PLC.

There are multiple entry points to the Primary clock routing throughout the Nexus device fabric. In this case, it is recommended to add a preference for this gated clock to use primary routing.

Figure 13.1. Gated Clock to the Primary Clock Routing

For a very small clock domain, user can limit the distance of a general routing based (gated) clock to one PLC in distance to the logic it clocks. The user must group this logic (UGROUP) with a *BBOX* (see Lattice Radiant Help > Constraints Reference Guide > Preferences > UGROUP) and specify a *PROHIBIT PRIMARY* on the generated clock. The *PROHIBIT\_PRIMARY* constraint allows the pin to be used as a clock source while the *BBOX* constraint is also included to ensure that timing closure can be obtained even without using a dedicated PCLK pin. If the software cannot place the logic tree within the *BBOX*, an error occurs.

Figure 13.2. Gated Clock to Small Logic Domain

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 14. sysCLOCK PLL

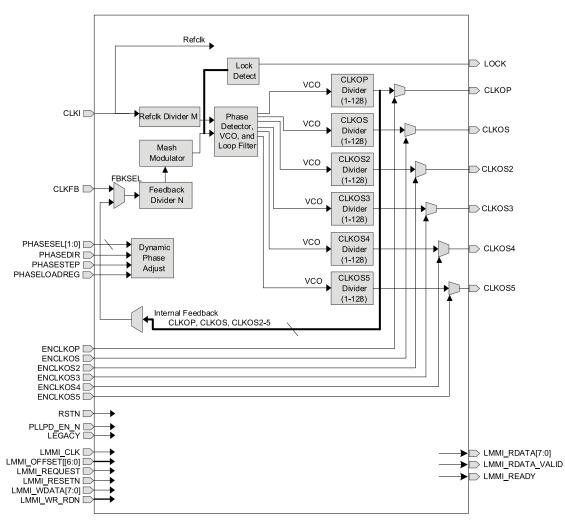

### 14.1. sysCLOCK PLL Overview

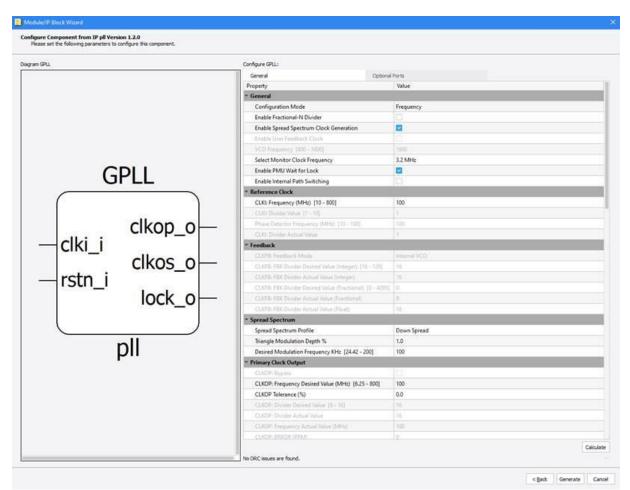

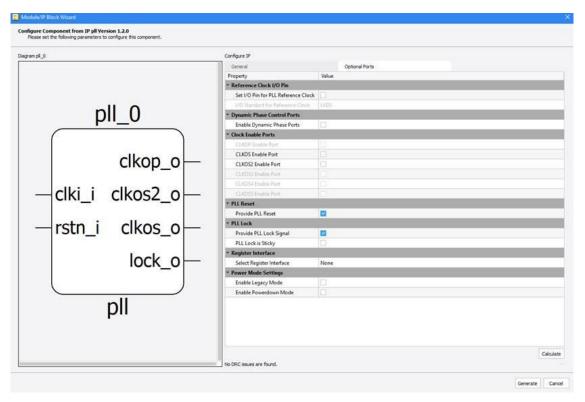

The sysCLOCK<sup>™</sup> PLLs can be used in a variety of clock management applications such as clock injection delay removal, clock phase adjustment, clock timing adjustment, and frequency synthesis (multiplication and division of a clock). The PLL supports Fractional-N synthesis. The Nexus IP Catalog PLL user interface shows important timing parameters such as the VCO rate and the PLL loop bandwidth.

The PLL Input sources are:

- Dedicated PLL Input Pins. See Appendix A for more details.

- Primary Clock Routing

- Edge Clock Routing

- FPGA Fabric

Figure 14.1. Nexus PLL Block Diagram

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

There are three PLLs for LIFCL-40, LFD2NX-40, and LFD2NX-28 at three corners as Upper Left, Lower Left and Lower Right, two PLLs for LIFCL-17, LFD2NX-17, and LFD2NX-9 at two corners as Lower Left and Lower Right corners. There are three PLLs for LFCPNX-50 at three corners as Upper Left, Lower Left and Lower Right, four PLLs for LFCPNX-100 at four corners as Upper Left, Upper Right, Lower Left and Lower Right. There are two PLLs for LFMXO5 at two corners as Upper Left and Lower Right. There is one PLL for LIFCL-33 at Lower Left corner. Each PLL has six outputs. All six PLL outputs can feed the Primary Clock and Edge Clock networks.

## 14.2. PLL Features

### 14.2.1. Dedicated PLL Inputs

Every PLL has a dedicated low skew input (PLLCK) that routes directly to its reference clock input. These are the recommended inputs for a PLL. It is possible to route a PLL input from the Primary clock routing, but it incurs more clock input injection delays, which are not natively compensated for using feedback, compared to a dedicated PLL input. In each corner of one Nexus device, there is one PLL at most. Each PLL on the Nexus device has one pair of dedicated PLL input pins.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 14.7. PLL Input Pins for LIFCL-33 and LIFCL-33U

# 14.2.2. Clock Injection Delay Removal

The clock injection delay removal feature of the PLL removes the delay associated with the PLL and clock tree. This feature is typically used to reduce the clock path delay which benefits system synchronous input and output timing. This feature is performed by aligning the PLL input clock with a feedback clock from the clock tree. Optional delay may also be added to the feedback path to further reduce the clock injection time.

## 14.2.3. Clock Phase Adjustment

The clock phase adjustment feature of the PLL provides the ability to set a specific phase offset between the outputs of the PLL. New to the Nexus device, phase adjustments can be calculated in much finer increments since the frequency is used to calculate the available phase increments. This feature is detailed further in the Dynamic Phase Adjustment section.

## 14.2.4. Frequency Synthesis

The PLL can be used to multiply up or divide down an input clock.

## 14.2.5. Legacy Mode (Standby)

In addition to the major features, the PLL has a Legacy Mode to reduce power. The Legacy Mode was called PLL standby mode. But due to the new proposed schemed for Nexus PLLs, it is given a different name to differentiate with the new STDBY mode. The Legacy Mode allows the PLL to be placed into a standby state to save power when not needed in the design. Standby mode is very similar to holding the PLL in reset since the VCO is turned off and needs to regain lock when exiting standby. In both cases, reset and standby mode, the PLL retains its programming.

The user MUST hold the PLL in standby for a minimum of 1 ms in order to be sure the PLL analog circuits are fully reset and analog startup is stable.

# 14.3. sysCLOCK PLL Component Definition

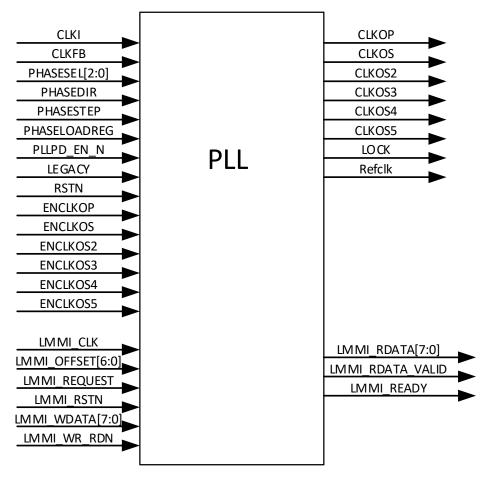

The PLL component can be instantiated in the source code of a design as defined in this section. Figure 14.8 and Table 14.1 show the definitions.

Figure 14.8. PLL Component Instance

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

#### **Table 14.1. PLL Component Port Definition**

| Signal           | I/O | Description                                                                               |  |

|------------------|-----|-------------------------------------------------------------------------------------------|--|

| CLKI             | I   | Input Clock to PLL.                                                                       |  |

| CLKFB            | I   | Feedback Clock.                                                                           |  |

| PHASESEL[2:0]    | I   | Select the output affected by Dynamic Phase adjustment.                                   |  |

| PHASEDIR         | I   | Dynamic Phase adjustment direction.                                                       |  |

| PHASESTEP        | I   | Dynamic Phase adjustment step.                                                            |  |

| PHASELOADREG     | I   | Not used. Tie low                                                                         |  |

| PLLPD_EN_N       | I   | Standby signal to power down the PLL.                                                     |  |

| LEGACY           | I   | Power mode setting to enable legacy mode                                                  |  |

| RST              | I   | Resets the entire PLL.                                                                    |  |

| ENCLKOP          | I   | Enable PLL output CLKOP.                                                                  |  |

| ENCLKOS          | I   | Enable PLL output CLKOS.                                                                  |  |

| ENCLKOS2         | I   | Enable PLL output CLKOS2.                                                                 |  |

| ENCLKOS3         | I   | Enable PLL output CLKOS3.                                                                 |  |

| ENCLKOS4         | I   | Enable PLL output CLKOS4.                                                                 |  |

| ENCLKOS5         | I   | Enable PLL output CLKOS5.                                                                 |  |

| CLKOP            | 0   | PLL main output clock.                                                                    |  |

| CLKOS            | 0   | PLL output clock.                                                                         |  |

| CLKOS2           | 0   | PLL output clock2.                                                                        |  |

| CLKOS3           | 0   | PLL output clock3.                                                                        |  |

| CLKOS4           | 0   | PLL output clock4.                                                                        |  |

| CLKOS5           | 0   | PLL output clock5.                                                                        |  |

| LOCK             | 0   | Indicates PLL is now locked to CLKI, Asynchronous signal. Active high indicates PLL lock. |  |

| Refclk           | 0   | Output of Reference clock.                                                                |  |

| LMMI_CLK         | I   | CIB LMMI interface clock                                                                  |  |

| LMMI_OFFSET[6:0] | I   | CIB LMMI interface address offset (LSB of address bus)                                    |  |

| LMMI_REQUEST     | I   | CIB LMMI interface request signal                                                         |  |

| LMMI_RESETN      | I   | CIB LMMI interface reset, active low                                                      |  |

| LMMI_WDATA[7:0]  | I   | CIB LMMI interface write data                                                             |  |

| LMMI_WR_RDN      | I   | CIB LMMI interface Write/Read control; 1=write, 0=read.                                   |  |

| LMMI_RDATA[7:0]  | 0   | CIB LMMI interface read data                                                              |  |

| LMMI_RDATA_VALID | 0   | CIB LMMI interface read data valid signal                                                 |  |

| LMMI_READY       | 0   | CIB LMMI interface ready signal                                                           |  |

# 14.4. Functional Description

## 14.4.1. Refclk (CLKI) Divider

The CLKI divider is used to control the input clock frequency into the phase detector. The valid PLL input frequency range is specified in the device data sheet.

## 14.4.2. Feedback Loop (CLKFB) Divider

The CLKFB divider is used to divide the feedback signal, effectively multiplying the output clock. The VCO block increases the output frequency until the divided feedback frequency equals the input frequency. The output of the feedback divider must be within the phase detector frequency range specified in the device data sheet. This port is only available to user interface when *user clock* option is selected for feedback clock. Otherwise, this port is connected by the tool to the appropriate signal user selected in the software.

# 14.4.3. Output Clock Dividers (CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, CLKOS5)

The output Clock Dividers allow the VCO frequency to be scaled up to the maximum range to minimize jitter. Each of the output dividers is independent of the other dividers and each uses the VCO as the source by default. Each of the output dividers can be set to a value of 1 to 128.

# 14.4.4. Phase Adjustment (Static Mode)

The CLKOP, CLKOS, CLKOS2, CLKOS3, CLKOS4, and CLKOS5 outputs can be phase adjusted relative to the enabled unshifted output clock. New to the Nexus devices, phase adjustments are now calculated values in the software tools based on VCO clock frequency. This provides a finer phase shift depending on the required frequency. The clock output selected as the feedback cannot use the static phase adjustment feature since it causes the PLL to unlock.

## 14.4.5. Phase Adjustment (Dynamic Mode)

The phase adjustments can also be controlled in a dynamic mode using the PHASESEL, PHASEDIR, and PHASESTEP ports. See the Dynamic Phase Adjustment section for usage details. The clock output selected as the feedback cannot use the dynamic phase adjustment feature since it causes the PLL to unlock.

Similar restrictions apply to other clocks.

# 14.5. PLL Inputs and Outputs

## 14.5.1. CLKI Input

The CLKI signal is the reference clock for the PLL. It must conform to the specifications in the data sheet for the PLL to operate correctly. The CLKI signal can come from a dedicated PLL input pin or from internal routing. The dedicated dual-purpose I/O pin provides a low skew input path and is the recommended source for the PLL. The reference clock can be divided by the input (M) divider to create one input to the phase detector of the PLL. The reference clock must be stable before the RST signal is deasserted.

## 14.5.2. CLKFB Input

The CLKFB signal is the feedback signal to the PLL. The feedback signal is used by the Phase Detector inside the PLL to determine if the output clock needs adjustment to maintain the correct frequency and phase. The CLKFB signal can come from a primary clock net (feedback mode = CLKO[P/S/S2/S3/S4/S5]) to remove the primary clock routing injection delay from an internal PLL connection (feedback mode = INT\_O[P/S/S2/S3/S4/S5]) for simple feedback. The feedback clock signal is divided by the feedback (N) divider to create an input to the phase detector of the PLL. A bypassed PLL output cannot be used as the feedback signal.

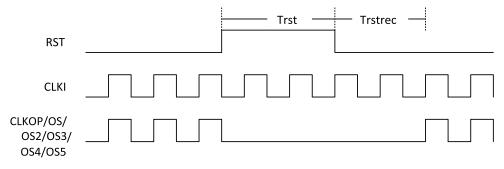

## 14.5.3. RST Input

At power-up, an internal power-up reset signal from the configuration block resets the PLL. Additionally, an active high, asynchronous, user-controlled reset port can be optionally added to the PLL. The RST signal can be driven by an internally generated reset function or by an I/O pin. This RST signal resets the PLL core (VCO, phase detector, and charge pump) and the output dividers which causes the outputs to be logic *O*. In bypass mode, the output does not reset. The reference clock must be stable before the RST signal is deasserted.

After the RST signal is deasserted, the PLL starts the lock-in process and takes tLOCK time, about 16 ms, to complete. Figure 14.9 shows the timing diagram of the RST input. The RST signal is active high. The RST signal is optional. Trst = 1 ms reset pulse width, Trstrec = 1 ns time after a reset before the divider output starts counting again.

© 2024 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Figure 14.9. RST Input Timing Diagram

## 14.5.4. Dynamic Clock Enables

Each PLL output has a user input signal to dynamically enable/disable its output clock glitchlessly. When the clock enable signal is set to logic *0*, the corresponding output clock is held to logic *0*.

| Clock Enable Signal Name | Corresponding PLL Output | IP Catalog Option Name |

|--------------------------|--------------------------|------------------------|

| ENCLKOP                  | CLKOP                    | "Clock Enable OP"      |

| ENCLKOS                  | CLKOS                    | "Clock Enable OS"      |

| ENCLKOS2                 | CLKOS2                   | "Clock Enable OS2"     |

| ENCLKOS3                 | CLKOS3                   | "Clock Enable OS3"     |

| ENCLKOS4                 | CLKOS4                   | "Clock Enable OS4"     |

| ENCLKOS5                 | CLKOS5                   | "Clock Enable OS5"     |

Table 14.2. PLL Clock Output Enable Signal List

The Dynamic Clock Enable function allows the user to save power by stopping the corresponding output clock when not in use. The clock enable signals are optional and are only available if user select the corresponding option in IP Catalog Wizard. If a clock enable signal is not requested, its corresponding output is always active when the PLL is instantiated unless the PLL is placed into standby mode. The user cannot access a PLL output clock enable signal in IP Catalog Wizard when the PLL output is used for external feedback to avoid shutting off the feedback clock.

# 14.5.5. PLLPD\_EN\_N Input

The PLLPD\_EN\_N signal is used to put the PLL into a low power standby mode when it is not required. The PLLPD\_EN\_N signal is optional and is only available if user select the *Enable Powerdown Mode* in the IP Catalog wizard. The PLLPD\_EN\_N signal is active low. When asserted, the PLL outputs are pulled to 0 and the PLL is reset. The user need to stay in the Power Down mode for at least 1 ms to make sure the PLL analog circuits are fully reset and to have a stable analog startup.

# 14.5.6. Dynamic Phase Shift Inputs

The Nexus PLL has five ports to allow for dynamic phase adjustment from FPGA logic. The Dynamic Phase Adjustment section elaborates on how user should drive these ports.

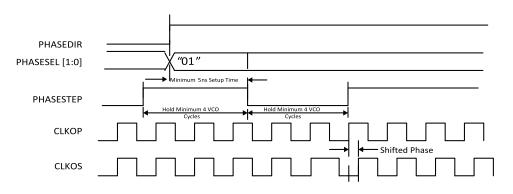

# 14.5.7. PHASESEL Input

The PHASESEL[2:0] inputs are used to specify which PLL output port is affected by the dynamic phase adjustment ports. The settings available are shown in the Dynamic Phase Adjustment section. The PHASESEL signal must be stable for 5 ns before the PHASESTEP is signals are pulsed. The PHASESEL signal is optional and is available if user select the *Enable Dynamic Phase Ports* option in IP Catalog Wizard.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| PHASESEL[2:0] | PLL Output Shifted |

|---------------|--------------------|

| 000           | CLKOP              |

| 001           | CLKOS              |

| 010           | CLKOS2             |

| 011           | CLKOS3             |

| 100           | CLKOS4             |

| 101           | CLKOS5             |

#### Table 14.3. PHASESEL Signal Settings Definition

### 14.5.8. PHASEDIR Input

The PHASEDIR input is used to specify which direction the dynamic phase shift occurs, advanced (leading) or delayed (lagging). When PHASEDIR = 0, then the phase shift is delayed. When PHASEDIR = 1, then the phase shift is advanced. The PHASEDIR signal must be stable for 5 ns before the PHASESTEP is pulsed. The PHASEDIR signal is optional and is available if user select the *Enable Dynamic Phase Ports* option in IP Catalog Wizard.

#### Table 14.4. PHASEDIR Signal Settings Definition

| PHASEDIR | Direction          |

|----------|--------------------|

| 0        | Delayed (lagging)  |

| 1        | Advanced (leading) |

### 14.5.9. PHASESTEP Input

The PHASESTEP signal is used to initiate a VCO dynamic phase shift for the clock output port and in the direction specified by the PHASESEL and PHASEDIR inputs. This phase adjustment is done by changing the phase of the VCO in 45° increments. The VCO phase changes on the negative edge of the PHASESTEP input after four VCO cycles. This is an active low signal and the minimum pulse width (both high and low) of PHASESTEP pulse is four VCO cycles. The PHASESTEP signal is optional and is available if user select the *Enable Dynamic Phase Ports* option in IP Catalog Wizard. The PHASESEL and PHASEDIR are required to have a setup time of 5 ns prior to PHASESTEP falling edge.