# PRODUCT INFORMATION NOTICE

| 1. TITLE                                                           |                                                             | 2. DOCUMENT NUMBER                                                  |                                      |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|--|--|--|

|                                                                    | T, MEMORY,DIGITAL,CMOS, A X<br>ION-HARDENED SRAM MONOLITHIC | SPO-2018-PIN-0003                                                   |                                      |  |  |  |

|                                                                    |                                                             | 3. DATE (Year, Month, Date)<br>2018, Oct, 1                         |                                      |  |  |  |

| CAES                                                               | NAME AND ADDRESS                                            | 5. MANUFACTURER POINT OF CONTACT NAME Peter Nelson                  |                                      |  |  |  |

| 4350 CENTENNIAL BOULEVARD<br>COLORADO SPRINGS, COLORADO 80907-3486 |                                                             | 6. MANUFACTURER POINT OF CONTACT TELEPHONE 719-594-8238             |                                      |  |  |  |

|                                                                    |                                                             | 7. MANUFACTURER POINT OF CONTACT EMAIL Peter.b.nelson@cobhamaes.com |                                      |  |  |  |

| 8. CAGE CODE 9. 65342                                              | . BLANK                                                     | 10. PRODUCT IDENTIFICATION CODE See Below                           | 11. BASE PART<br>See Below           |  |  |  |

| 12. BLANK                                                          |                                                             | 13. SMD NUMBER<br>See Below                                         | 14. DEVICE TYPE DESIGNATOR See Below |  |  |  |

|                                                                    |                                                             | 15. RHA LEVELS D, P, L, R, F                                        | 16. QML LEVEL<br>Q, V                |  |  |  |

|                                                                    |                                                             | 17. NON QML LEVEL<br>N/A                                            | 18. GIDEP NUMBER  GB4-I-19-0001      |  |  |  |

#### 19. DESCRIPTION (FOR NEW PRODUCTS, PROVIDE AVAILABILITY DATE AND LEAD TIME)

Summary: This ADEPT adds two guaranteed by design AC timing specifications to both the datasheet and SMD ( $t_{AVSK}$  and  $t_{AVET2}$ ) which where recommendations of the previously documented application note (AN-MEM-002). Datasheet changes are also noted herein. This change places the data from the app note into the datasheet and SMD to ensure that the user does not miss the timing info.

Additionally, the absolute maximum rating will be increased to 4.5 and 2.4 Volts for Vdd and VIO respectively to match the test conditions during burn-in.

| Product Name:         | Manufacturer<br>Part Number | SMD#       | Device Type |

|-----------------------|-----------------------------|------------|-------------|

| 4M Asynchronous SRAM  | UT8R128K32                  | 5962-03236 | 01 & 02     |

| 4M Asynchronous SRAM  | UT8R512K8                   | 5962-03235 | 01 & 02     |

| 16M Asynchronous SRAM | UT8CR512K32                 | 5962-04227 | 01 & 02     |

| 16M Asynchronous SRAM | UT8ER512K32                 | 5962-06261 | 05 & 06     |

NOTE: THIS DOCUMENT IS PUBLISHED FOR INFORMATION PURPOSES AND MAY PROVIDE FORWARD LOOKING STATEMENTS THAT ARE SUBJECT TO CHANGE. THE USERS SHOULD CONTACT THEIR LOCAL CAES SALES OFFICE FOR ANY ACTIONABLE CONTENT DESCRIBED HEREIN.

| 20. ADEPT REPRESENTATIVE | 21. SIGNATURE | 22. DATE   |

|--------------------------|---------------|------------|

| Tim Meade                | Timothy Moade | 10/01/2018 |

#### **Section 1: SMD changes**

## **TABLE 1A** Electrical performance characteristics.

Add parameters  $t_{AVSK}$  and  $t_{AVET2}$

| Test                                             | Symbol | Test conditions<br>-55°C < Tc < +125°C (Devices 01,03,05)<br>-40°C < Tc < +125°C (Devices 02,04,06)<br>+4.5 V < V <sub>DD</sub> < +5.5 V | Group A<br>subgroups | Device<br>type     | Liı | mits      | Unit |

|--------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-----|-----------|------|

|                                                  |        | unless otherwise specified                                                                                                               |                      |                    | Min | Max       |      |

| Functional test                                  |        | See 4.4.1c, VIH = VDD -0.5V                                                                                                              | 7,8A,8B              | All                |     | <u>1/</u> |      |

| Address valid to address valid skew time XX/     | tavsk  | See figures 4 and 5.                                                                                                                     | 9,10,11              | See above table    |     | 4         | ns   |

|                                                  |        | M,D,P,L                                                                                                                                  | 9                    | All                | 1/  |           |      |

| Address setup time for read (E – controlled) XX/ | tavet2 |                                                                                                                                          | 9,10,11              | See above<br>table | -4  |           | ns   |

|                                                  |        | M,D,P,L                                                                                                                                  | 9                    | All                |     | 1/        |      |

## Add note 12 designation to $t_{AVAV}$ parameter

| Read cycle time 6/, YY/ | t <sub>AVAV</sub> | See figures 4 and 5. |         | 9,10,11 | 01,02  | 25         | ns |

|-------------------------|-------------------|----------------------|---------|---------|--------|------------|----|

|                         |                   |                      |         |         | 03,04, | 20         |    |

|                         |                   |                      |         |         | 05, 06 |            |    |

|                         |                   |                      | M,D,P,L | 9       | All    | <u>1</u> / |    |

#### Add two notes to Table 1A

XX/ Guaranteed by design

$\overline{YY}$  Address changes prior to satisfying  $t_{AVAV}$  minimum is an invalid operation

Changes to absolute maximum ratings Vdd1 change to 2.4V Vdd2 change to 4.5V

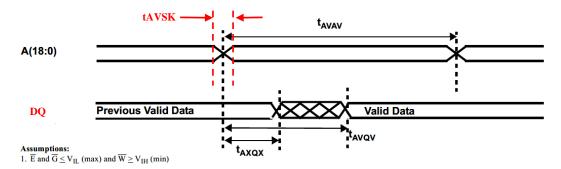

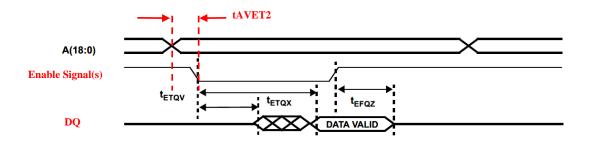

## Add timing parameters to SRAM read cycle 1 and read cycle 2

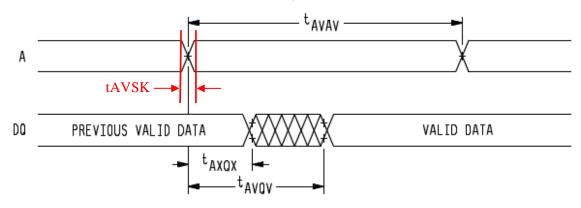

SRAM read cycle 1: address access.

Note: E and  $G \le V_{IL}(max)$  and  $W \ge V_{IH}$  (min).

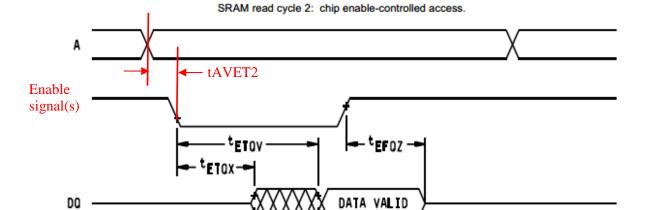

Note:  $G \le V_{IL}(max)$  and  $W \ge V_{IH}$  (min).

FIGURE 5. Timing waveforms - Continued.

#### **Section 2: Datasheet changes**

# Datasheet Add last sentences to the end of both paragraphs

**READ CYCLE**

A combination of  $\overline{W}$  greater than VIH (min) and  $\overline{E}$  less than VIL (max) defines a read cycle. Read access time is measured from the latter of Chip Enable, Output Enable, or valid address to valid data output. Read cycles initiate with the assertion of chip enable or any address input change while chip enable is asserted.

SRAM Read Cycle 1, the Address Access in figure 4a is initiated by a change in address inputs while the chip is enabled with  $\overline{G}$  asserted and  $\overline{W}$  deasserted. Valid data appears on data outputs DQ(7:0) after the specified tAVQV is satisfied. Outputs remain active throughout the entire cycle. As long as chip enable and output enable are active, the address inputs may change at a rate equal to the minimum read cycle time (tAVAV). Changing addresses prior to satisfying tAVAV minimum results in an invalid operation. Invalid read cycles will require reinitialization.

The single die devices will say "read cycles initiate with assertion of chip enable and address changes while chip enable is asserted". The MCM parts with multiple chip enables will say "read cycle initiates with the assertion of any chip enable and also address changes while any chip enable is asserted".

#### **Absolute Maxiumum Ratings Table**

Vdd1 changed to -0.3 to 2.4V Vdd2 changed to -0.3 to 4.5V VI/O changed to -0.3 to 4.5V

# AC Characteristics read cycle table Adding parameters t<sub>AVSK</sub> and t<sub>AVET2</sub> and two additional notes

#### AC CHARACTERISTICS READ CYCLE (Pre/Post-Radiation)\*

-55°C to +125°C for (C) screening and -40°C to +125°C for (W) screening ( $V_{DD} = 5.0V + 10\%$ )

| SYMBOL                 | PARAMETER                                      | MIN | MAX | UNIT |

|------------------------|------------------------------------------------|-----|-----|------|

| tAVAV <sup>1,6</sup>   | Read cycle time                                | 20  |     | ns   |

| tAVSK <sup>5</sup>     | Adress valid to address valid skew time        |     | 4   | ns   |

| tAVQV                  | Read access time                               |     | 20  | ns   |

| tAXQX                  | Output hold time                               | 3   |     | ns   |

| tGLQX                  | G-controlled Output Enable time                | 0   |     | ns   |

| tGLQV                  | G-controlled Output Enable time (Read Cycle 3) |     | 10  | ns   |

| $tGHQZ^2$              | G-controlled output three-state time           |     | 10  | ns   |

| tetQX <sup>3</sup>     | E-controlled Output Enable time                | 3   |     | ns   |

| tAVET2 <sup>5</sup>    | Address setup time for read (E-controlled)     | -4  |     | ns   |

| tETQV <sup>3</sup>     | E-controlled access time                       |     | 20  | ns   |

| tEFQZ <sup>1,2,4</sup> | E-controlled output three-state time           |     | 10  | ns   |

Notes: \* Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019.

- 1. Functional test.

- Three-state is defined as a 500mV change from steady-state output voltage.

The ET (chip enable true) notation refers to the falling edge of En. SEU immunity does not affect the read parameters.

The EF (chip enable false) notation refers to the rising edge of En. SEU immunity does not affect the read parameters.

Guaranteed by design.

Address changes prior to satisfying tavay minimum is an invalid operation.

# SRAM Read cycle 1 and 2 Adding parameters tAVSK and tAVET2 to timing diagrams

Figure 4a. SRAM Read Cycle 1: Address Access

$\begin{array}{l} \textbf{Assumptions:} \\ 1. \ \overline{G} \leq V_{IL} \ (\text{max}) \ \text{and} \ \overline{W} \geq V_{IH} \ (\text{min}) \\ \end{array}$

Figure 4b. SRAM Read Cycle 2: Chip Enable-Controlled Access