## AEROSPACE DATA EXCHANGE PROGRAM TRANSMITTAL

# PROBLEM ADVISORY

| MICROCIRCUIT, DIGITAL, CMOS, RADIATION                                       |                                             | SPO-2013-PA-0002                                          |                                                                                                                                                        |                                                              |  |

|------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| HARDENED, 32-BIT FAULT-TOLERANT V8/LEON<br>3FT PROCESSOR, MONOLITHIC SILICON |                                             |                                                           | 3. DATE (Year, Month, Date)<br>2013, February, 15                                                                                                      |                                                              |  |

| 4. MANUFACTURER NAME AND ADDRESS<br>CAES                                     |                                             |                                                           | 5. MANUFACTURER POINT OF CONTACT NAME<br>James Nagy                                                                                                    |                                                              |  |

| 4350 CENTENNIAL BOULEVARD                                                    |                                             |                                                           | 6. MANUFACTURER POINT OF CONTACT TELEPHONE                                                                                                             |                                                              |  |

| COLORADO SPRINGS, COLORADO 80907-3486                                        |                                             |                                                           | (719) 594-8417                                                                                                                                         |                                                              |  |

|                                                                              |                                             |                                                           | 7. MANUFACTURER POINT OF CONTACT EMAIL                                                                                                                 |                                                              |  |

|                                                                              |                                             |                                                           | Jim.nagy@cobhamaes.com                                                                                                                                 |                                                              |  |

| 8. CAGE CODE                                                                 | 9. LDC START                                | 10. LDC END                                               | 11. PRODUCT IDENTIFICATION CODE                                                                                                                        | 12. BASE PART                                                |  |

| 65342                                                                        | All                                         | All                                                       | WG07A                                                                                                                                                  | UT699                                                        |  |

| 13. BLANK                                                                    |                                             |                                                           | 14. SMD NUMBER                                                                                                                                         | 15. DEVICE TYPE DESIGNATOR                                   |  |

|                                                                              |                                             |                                                           | 5962-08228                                                                                                                                             | 01 & 02                                                      |  |

|                                                                              |                                             |                                                           | 16. RHA LEVELS                                                                                                                                         | 17. QML LEVEL                                                |  |

|                                                                              |                                             |                                                           | R&F                                                                                                                                                    | Q & V                                                        |  |

|                                                                              |                                             |                                                           | 18. NON QML LEVEL                                                                                                                                      | 19. BLANK                                                    |  |

|                                                                              |                                             |                                                           | Proto & HiRel                                                                                                                                          |                                                              |  |

| 20. PROBLEM DES                                                              | SCRIPTION / DISCUSSION /                    | / EFFECT                                                  |                                                                                                                                                        |                                                              |  |

| operations. The reset during p                                               | he PCI core requires<br>power up and master | proper initialization even<br>reset periods, it can lock- | udes a PCI core that can be configured<br>when PCI is not utilized. If the PC<br>-up the internal AMBA bus. When<br>x0 following the de-assertion of R | CI core is not synchronously<br>n the AMBA bus is locked up, |  |

#### 21. ACTION TAKEN / PLANNED

1. TITLE

The requirement to synchronously reset the PCI core is the only guaranteed method to ensure the PCI core is properly initialized and place in an unused idle state. No design change is planned to remove the synchronous reset requirement.

Corrective actions:

Update the UT699 Datasheet with the additional synchronous reset requirements (COMPLETE)

attached Manufacturer's Product Advisory for additional information.

- Refer to Section 4.6 Timing Characteristics for PCI Interface in the UT699 Datasheet for a description of the required startup sequence. Figure 11 shows the proper signal and clock timing relationships in the case where the PCI core is utilized in a system. Once the PCI core is properly initialized, it may be utilized normally as described in Chapter 9.0 PCI Target / Master Unit of the UT699 Functional Manual. Figure 12 in the datasheet shows the same timing relationships in the case where the PCI core is not utilized. Thereafter, each time power is cycled, the system must perform the initialization sequence.

- Produce a Product Advisory to provide additional explanation of the problem and its work around. (See attached) (COMPLETE)

- Update the product SMD (5962-08228) with the equivalent reset parameters as described for the datasheet above. (Plan completion by March 2013)

| 22. DISPOSITIONARY RECOMMENDATION: | CHECK &  USE AS IS | CONTACT  | REMOVE & | CORRECT & 🛛<br>USE AS SPECIFIED |

|------------------------------------|--------------------|----------|----------|---------------------------------|

| 23. ADEPT REPRESENTATIVE           | 24. SIGNATURE      |          |          | 25. DATE                        |

| Timothy L. Meade                   |                    | mothy me | ade_     | 15 February, 2013               |

### **UT699 PCI Reset and Clock Requirements**

| Product Name:                                              | Manufacturer<br>Part Number | SMD #      | Device Type | Internal PIC <sup>*</sup><br>Number: |

|------------------------------------------------------------|-----------------------------|------------|-------------|--------------------------------------|

| UT699 32-bit Fault-Tolerant<br>SPARC V8/LEON 3FT Processor | UT699                       | 5962-08228 | 01, 02      | WG07                                 |

Table 1: Cross Reference of Applicable Products

\* PIC = Product Identification Code

## 1 Overview

The UT699 Leon 3FT microprocessor system-on-chip includes a PCI core that can be configured for 32-bit, 33MHz operations. The PCI core requires proper initialization even when PCI is not utilized. If proper initialization requirements are not met, the PCI core can lock up the internal AMBA bus in some instances causing the entire processor to lock up. This lockup condition is identified by the processor performing a single access to PROM at address 0x0 following the de-assertion of RESET with no subsequent PROM accesses occurring. This advisory explains the requirements for PCI initialization. The initialization sequence is required during the power-up sequence after which time the PCI core may be utilized normally as described in **Chapter 9.0 PCI Target / Master Unit** of the *UT699 Functional Manual*. Thereafter, each time power is cycled, the system must perform the initialization sequence. Timing requirements for PCI clock gating are also discussed.

# 2 PCI Initialization Requirements

#### 2.1 PCI Core Utilized in System

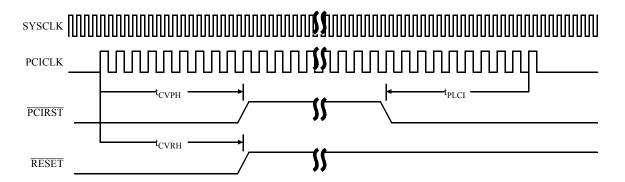

Figure 1 shows the required timing relationship between the PCI clock input and the  $\overline{\text{RESET}}$  and  $\overline{\text{PCIRST}}$  inputs when the PCI core is utilized. It is assumed that the V<sub>DD</sub> and V<sub>DDC</sub> power rails are stable and the SYSCLK input has a valid clock as described in **Section 4.1 Power Sequencing and Reset** of the *UT699 Leon 3FT Data Sheet*. Parameters t<sub>CVPH</sub> and t<sub>CVRH</sub> are specified in PCI clock cycles and must be met in order to ensure that the PCI state machine is initialized to idle state prior to the execution of code. RESET may be deasserted after 10 valid PCI clock cycles. There is no timing requirement for RESET relative to  $\overline{\text{PCIRST}}$ . The PCI core may be held in reset by asserting  $\overline{\text{PCIRST}}$  until core utilization is required.

If clock gating is used to reduce power, the PCI clock can be disabled after delaying  $t_{PLCI}$  following the assertion of the PCIRST. Refer to Table 2 for a summary of the timing parameters.

Figure 1. Timing Relationships of Clock and Reset Inputs for PCI Core Utilization

#### 2.2 Initialization of Unused PCI Core

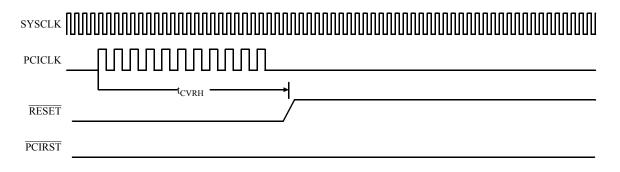

Figure 2 shows the required timing relationship between the PCI clock input and  $\overline{\text{RESET}}$  when the PCI core is not utilized. It is assumed that the V<sub>DD</sub> and V<sub>DDC</sub> power rails are stable, and that the SYSCLK input has a valid system clock per Section 4.1 **Power Sequencing and Reset** of the *UT699 Leon 3FT Data Sheet*. The critical timing parameter is t<sub>CVRH</sub> which must be met in order to ensure that the PCI state machine is initialized to idle state. RESET may be deasserted after 10 valid PCI clock cycles. The PCI clock input may be permanently tied low or high immediately following the rising edge of RESET. Since PCI is not being used, PCIRST is permanently tied to V<sub>SS</sub>.

Refer to Table 2 for a summary of critical and recommended timing parameters.

Figure 2. Timing Relationships of Clock and Reset Inputs for Unused PCI Core

#### 2.3 Timing Summary

The following table summarizes the required and recommended timing parameters to ensure proper PCI core and system operation.

| Symbol            | Description                        | Min | Max | Units      |

|-------------------|------------------------------------|-----|-----|------------|

| t <sub>CVRH</sub> | PCICLK↑ to RESET deassertion       | 10  |     | PCI clocks |

| t <sub>CVPH</sub> | PCICLK↑ to PCIRST deassertion      | 10  |     | PCI clocks |

| t <sub>PLCI</sub> | PCIRST assertion to PCICLK invalid | 10  |     | PCI clocks |

**Table 2: Summary of Timing Parameters**