# UT699E/UT700 LEON 3FT /SPARC<sup>™</sup> V8 Microprocessor

## **Table of Contents**

| Chapter | 1:    | Introduction                             | 11 |

|---------|-------|------------------------------------------|----|

| 1.1     | Scop  | pe                                       | 11 |

| 1.2     | Diffe | erences between UT699, UT699E, and UT700 | 11 |

| 1.3     | Arch  | nitecture                                | 13 |

| 1.4     | Men   | nory Map                                 | 14 |

| 1.5     | Inte  | rrupts                                   | 15 |

| 1.6     | Sign  | nals                                     | 15 |

| 1.7     | Cloc  | king                                     | 18 |

| 1.7.    | 1     | Clock Inputs                             | 18 |

| 1.7.    | 2     | Clock Output                             | 18 |

| Chapter | 2:    | LEON 3FT SPARC V8 32-bit Microprocessor  | 19 |

| Chapte  | er 2: |                                          | 19 |

| 2.1     | Ove   | rview                                    | 19 |

| 2.1.    | 1     | Integer Unit                             | 19 |

| 2.1.    | 2     | Cache Sub-System                         | 19 |

| 2.1.    | 3     | Floating-Point Unit                      | 19 |

| 2.1.    | 4     | Memory Management Unit                   | 20 |

| 2.1.    | 5     | On-Chip Debug Support                    | 20 |

| 2.1.    | 6     | Interrupt Port                           | 20 |

| 2.1.    | 7     | AMBA Interface                           | 20 |

| 2.1.    | 8     | Power-Down Mode                          | 20 |

| 2.2     | LEO   | N 3FT Integer Unit                       | 20 |

| 2.2.    | 1     | Overview                                 | 20 |

| 2.2.    | 2     | Instruction Pipeline                     | 21 |

| 2.2.    | 3     | SPARC Implementer's ID                   | 22 |

| 2.2.    | 4     | Division Instructions                    | 23 |

| 2.2.    | 5     | Multiplication Instructions              | 23 |

| 2.2.    | 6     | Branch Prediction                        | 23 |

| 2.2.    | 7     | Hardware Breakpoints                     | 23 |

| 2.2.    | 8     | Instruction Trace Buffer                 | 24 |

| 2.2.    | 9     | Processor Configuration Register         | 25 |

| 2.2.    | 10    | Exceptions                               | 26 |

Version 1.3.0

| 2.2.12     | Address Space Identifiers (ASI)27          |

|------------|--------------------------------------------|

| 2.2.13     | Power-Down                                 |

| 2.2.14     | Processor Reset Operation                  |

| 2.2.15     | Integer Unit SEU Protection                |

| 2.3 Flo    | pating Point Unit                          |

| 2.3.1      | Floating Point Unit Functional Description |

| 2.3.2      | Floating Point Number Formats              |

| 2.3.3      | Floating Point Operations                  |

| 2.3.4      | Exceptions                                 |

| 2.3.5      | Rounding                                   |

| 2.3.6      | Denormalized numbers                       |

| 2.3.7      | Non-standard Mode                          |

| 2.3.8      | Not-A-Number (NaN)                         |

| 2.4 Flo    | pating Point Unit                          |

| 2.4.1      | Overview                                   |

| 2.4.2      | Instruction Cache                          |

| 2.4.3      | Data Cache                                 |

| 2.4.4      | Write Buffer                               |

| 2.4.5      | Instruction and Data Cache Tags            |

| 2.4.6      | Cache Flushing                             |

| 2.4.7      | Data Cache Snooping                        |

| 2.4.8      | Diagnostic Cache Access                    |

| 2.4.9      | Cache Control Register                     |

| 2.4.10     | Error Protection                           |

| 2.4.11     | Cache Configuration Registers              |

| 2.4.12     | Software Consideration                     |

| 2.5 Me     | emory Management Unit                      |

| 2.5.1      | MMU ASI Usage                              |

| 2.5.2      | Cache Operation                            |

| 2.5.3      | MMU Registers40                            |

| 2.5.4      | Translation Look-Aside Buffer (TLB)43      |

| 2.6 LE     | ON 3FT Storage Allocation43                |

| 2.6.1      | Integer Unit Register File43               |

| 2.6.2      | Floating Point Unit (FPU) Register File43  |

| 2.6.3      | Cache Memories43                           |

| Chapter 3: | Memory Controller with EDAC45              |

| Chapter 3  | 3:                                         |

| 3.1 Ov     | verview                                    |

| 3.2     | PROM   | 1 Access                                       | 46 |

|---------|--------|------------------------------------------------|----|

| 3.3     | Memo   | ory Mapped I/O                                 | 46 |

| 3.4     | SRAM   | 1 Access                                       | 46 |

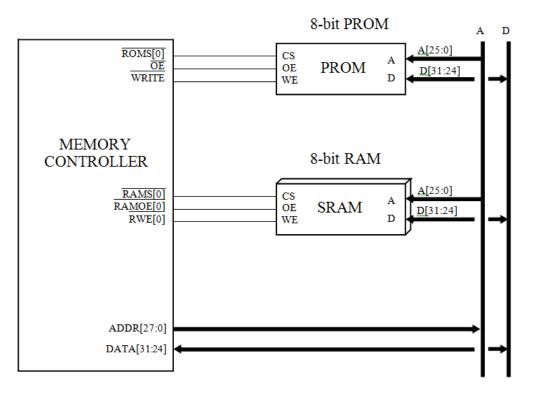

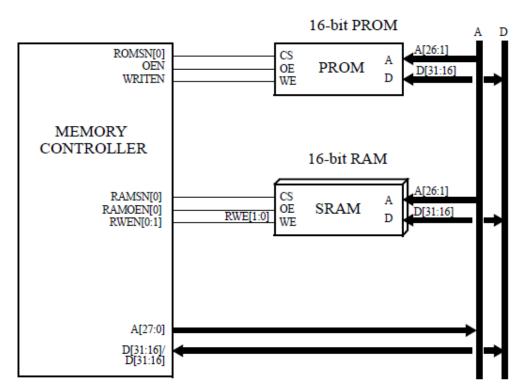

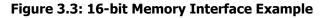

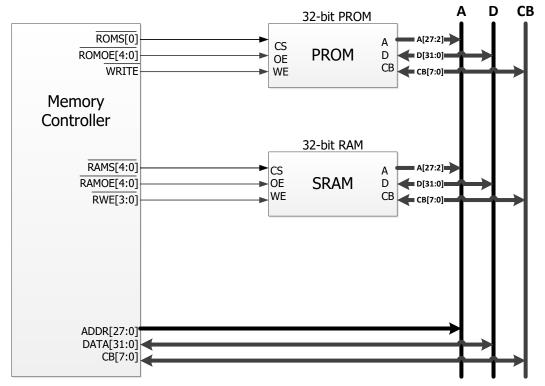

| 3.5     | 8-bit  | and 16-bit PROM and SRAM Access                | 47 |

| 3.6     | 8-bit  | and 16-bit I/O Accesses                        | 49 |

| 3.7     | Burst  | Cycles                                         | 49 |

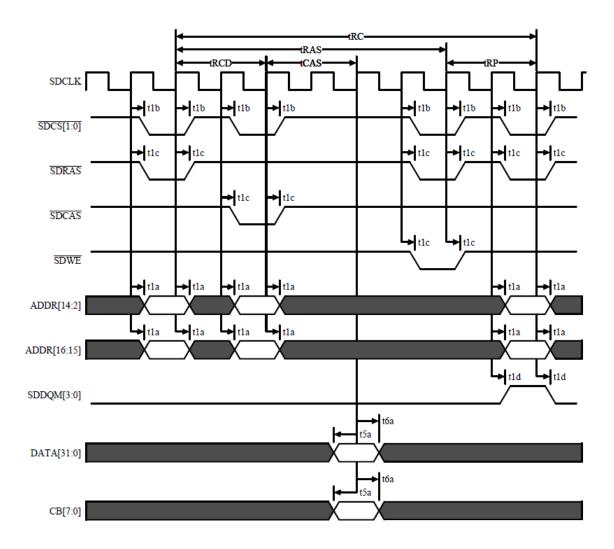

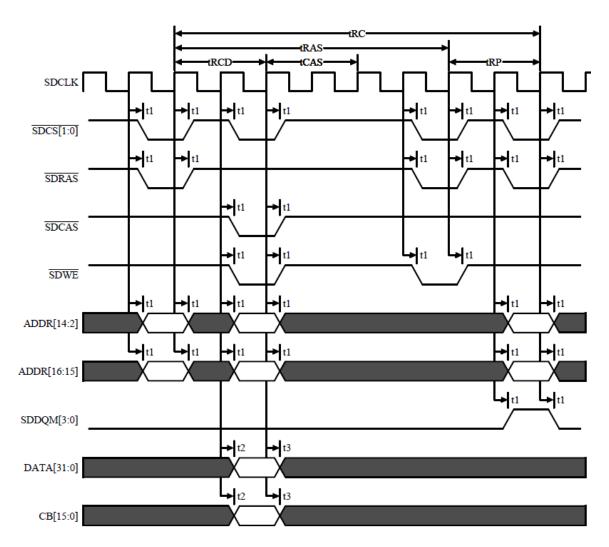

| 3.8     | SDRA   | M Access                                       | 49 |

| 3.8     | .1 (   | General                                        | 49 |

| 3.8     | .2 /   | Address Mapping                                | 49 |

| 3.8     | .3 1   | Initialization                                 | 49 |

| 3.8     | .4 (   | Configurable SDRAM Timing Parameters           | 49 |

| 3.9     | Refre  | sh                                             | 50 |

| 3.9     | .1 9   | SDRAM Commands                                 | 50 |

| 3.9     | .2 I   | Read Cycles                                    | 50 |

| 3.9     | .3 \   | Write Cycles                                   | 50 |

| 3.9     | .4 /   | Address Bus                                    | 51 |

| 3.9     | .5 I   | Data Bus                                       | 51 |

| 3.9     | .6 (   | Clocking                                       | 51 |

| 3.9     | .7 ]   | Initialization                                 | 51 |

| 3.9     | .8 .9  | SDDQM[3:0] Control Signals                     | 51 |

| 3.10    | Memo   | ory EDAC                                       | 51 |

| 3.1     | 0.1    | BCH EDAC                                       | 51 |

| 3.1     | 0.2    | Reed-Solomon EDAC                              | 52 |

| 3.1     | 0.3    | EDAC Error Reporting                           | 53 |

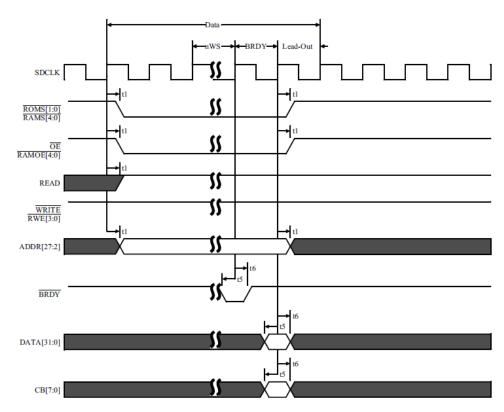

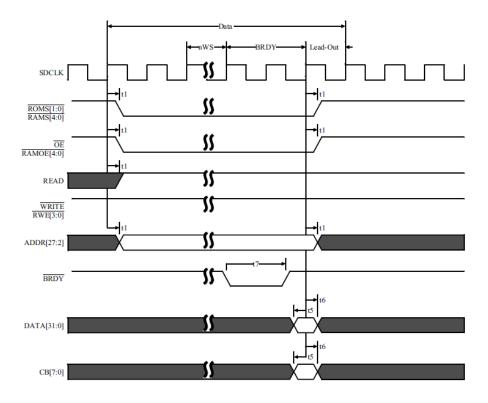

| 3.11    | Using  | BRDY                                           | 53 |

| 3.12    | Acces  | ss Errors                                      | 54 |

| 3.13    | Attac  | hing an External DRAM Controller               | 54 |

| 3.14    | Regis  | ters                                           | 54 |

| 3.1     | 4.1    | Memory Configuration Register 1 (MCFG1)        | 54 |

| 3.1     | 4.2    | Memory Configuration Register 2 (MCFG2)        | 56 |

| 3.1     | 4.3    | Memory Configuration Register 3 (MCFG3)        | 58 |

| 3.1     | 4.4    | Memory Configuration Register 4 (MCFG4)        | 59 |

| 3.15    | Boot   | Strap Configuration                            | 59 |

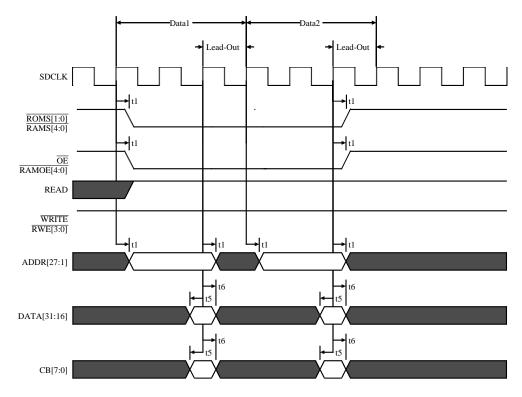

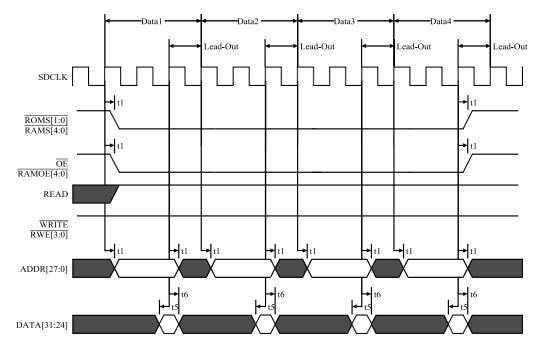

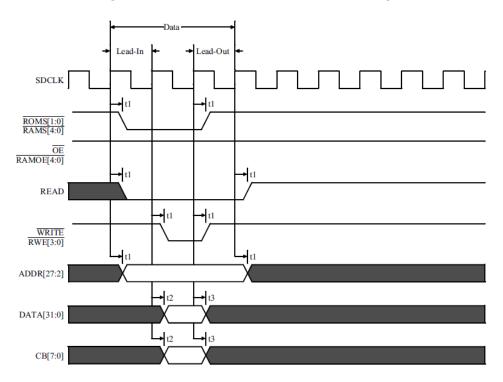

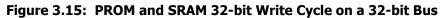

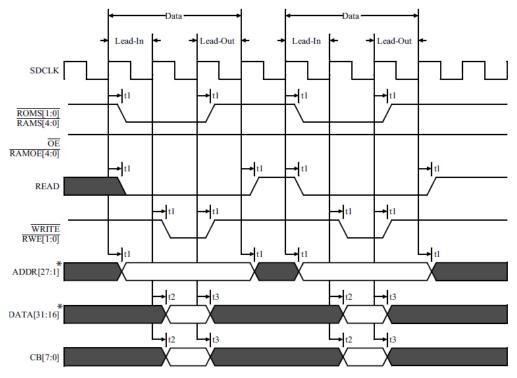

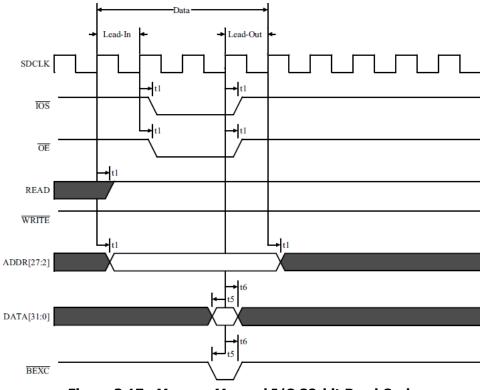

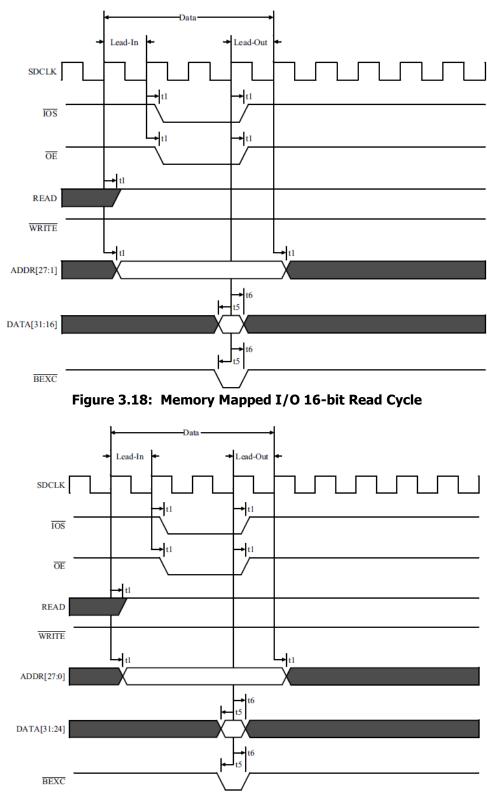

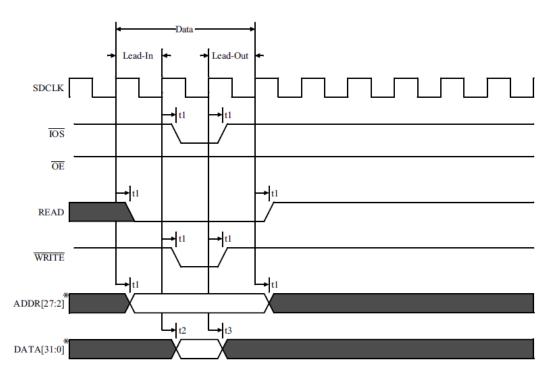

| 3.16    | PROM   | 1, SRAM, and Memory Mapped I/O Timing Diagrams | 60 |

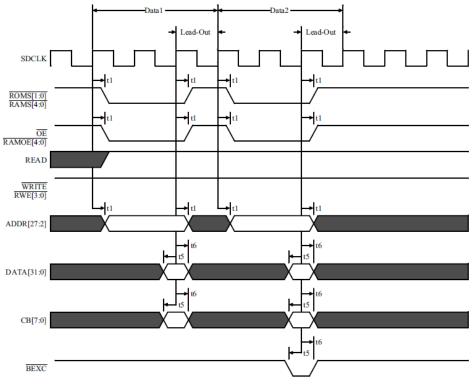

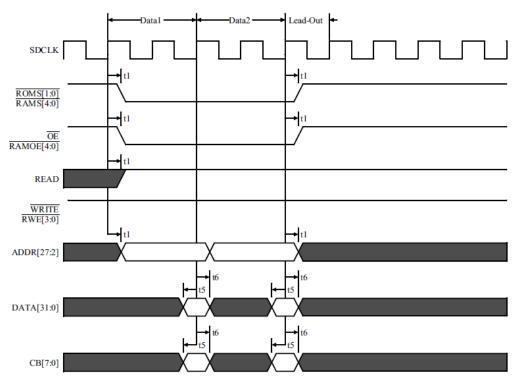

| 3.17    | SDRA   | M Timing Diagram                               | 66 |

| Chapter | 4:     | AHB Status Registers                           | 69 |

| Chapt   | ter 4: |                                                | 69 |

| 4.1     | Over   | view                                           | 69 |

| 4.2     | Opera  | ation                                          | 69 |

| 4.3   | 3    | Corr  | ectable Errors                          | 9 |

|-------|------|-------|-----------------------------------------|---|

| 4.4   | ł    | Inter | rrupts6                                 | 9 |

| 4.5   | 5    | Regi  | sters6                                  | 9 |

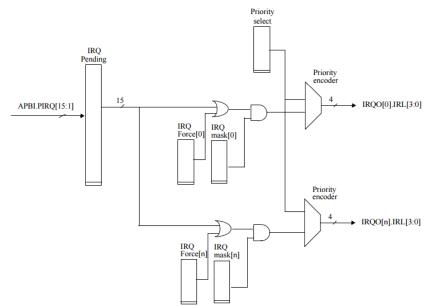

| Chapt | ter  | 5:    | Interrupt Controller7                   | 1 |

| Ch    | apte | er 5: | 7                                       | 1 |

| 5.1   | L    | Over  | rview7                                  | 1 |

| Į     | 5.1. | 1     | Interrupt Prioritization                | 1 |

| Į     | 5.1. | 2     | Interrupt Allocation                    | 1 |

| 5.2   | 2    | Regi  | sters7                                  | 2 |

| Į     | 5.2. | 1     | Interrupt Level Register                | 2 |

| Į     | 5.2. | 2     | Interrupt Pending Register              | 3 |

| ļ     | 5.2. | 3     | Interrupt Force Register                | 3 |

| Į     | 5.2. | 4     | Interrupt Clear Register                | 4 |

| Į     | 5.2. | 5     | Interrupt Status Register               | 4 |

| Į     | 5.2. | 6     | Interrupt Mask Register                 | 5 |

| Į     | 5.2. | 7     | Extended Interrupt Acknowledge Register | 5 |

| Chapt | ter  | 6:    | UART with APB Interface                 | 7 |

| Ch    | apte | er 6: |                                         | 7 |

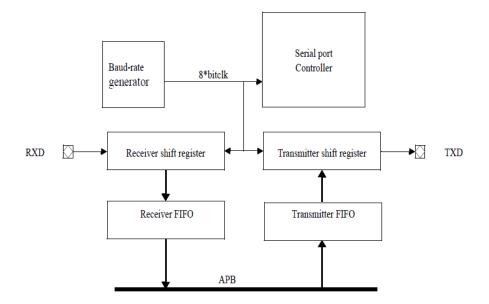

| 6.1   | L    | Over  | rview7                                  | 7 |

| 6.2   | 2    | Oper  | ration7                                 | 7 |

| (     | 6.2. | 1     | Transmitter Operation                   | 7 |

| e     | 6.2. | 2     | Receiver Operation                      | 8 |

| 6.3   | 3    | Bauc  | d Rate Generation                       | 8 |

| 6     | 6.3. | 1     | Loop Back Mode                          | 8 |

| e     | 6.3. | 2     | Interrupt Generation                    | 9 |

| 6.4   | ł    | UAR   | T Registers                             | 9 |

| e     | 6.4. | 1     | UART Data Register                      | 9 |

| 6     | 6.4. | 2     | UART Status Register                    | 0 |

| e     | 6.4. | 3     | UART Control Register                   | 1 |

| (     | 6.4. | 4     | UART Scaler Register                    | 2 |

| Chapt | ter  | 7:    | Timer Unit                              | 4 |

| Ch    | apte | er 7: |                                         | 4 |

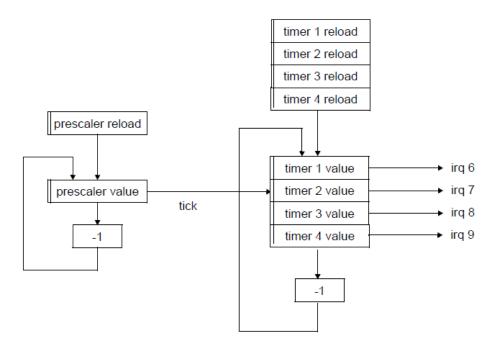

| 7.1   | L    | Over  | rview                                   | 4 |

| 7.2   | 2    | Oper  | ration8                                 | 4 |

| 7.3   | 3    | Regi  | sters8                                  | 5 |

| Chapt | ter  | 8:    | General Purpose I/O Port                | 9 |

| Ch    | apte | er 8: |                                         | 9 |

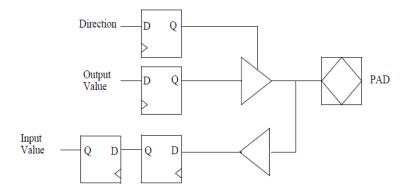

| 8.1   | L    | Over  | rview                                   | 9 |

| 8.2   | 2    | Ope   | ration8                                 | 9 |

| 8.3     | Registe | er                                        | . 89 |

|---------|---------|-------------------------------------------|------|

| 8.3.    | .1 G    | PIO Port Input Value Register             | . 90 |

| 8.3.    | 2 GI    | PIO Port Data Output Register             | . 90 |

| 8.3.    | .3 GI   | PIO Port Data Direction Register          | .91  |

| 8.3.    | 4 GI    | PIO Interrupt Mask Register               | .91  |

| 8.3.    | .5 GI   | PIO Interrupt Priority Register           | .91  |

| 8.3.    | .6 GI   | PIO Interrupt Edge Register               | . 92 |

| Chapter | 9:      | PCI Master/Target Unit                    | 93   |

| Chapt   | er 9:   |                                           | .93  |

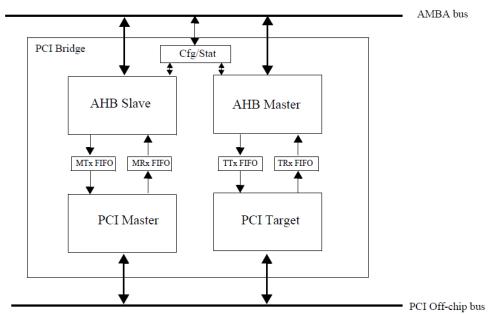

| 9.1     | Overvie | ew                                        | .93  |

| 9.2     | Operat  | tion                                      | . 93 |

| 9.2.    | 1 PC    | CI Target Unit                            | .93  |

| 9.2.    | 2 PC    | CI Master Unit                            | .93  |

| 9.2.    | .3 Bi   | urst Transactions                         | .93  |

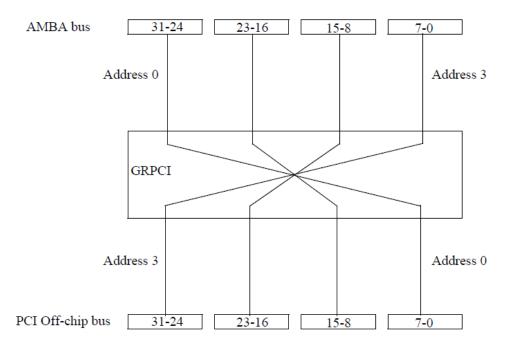

| 9.2.    | 4 By    | yte Twisting                              | .94  |

| 9.3     | PCI Ta  | rget Interface                            | .94  |

| 9.4     | PCI Ta  | rget Configuration Space Header Registers | . 95 |

| 9.5     | PCI Ta  | rget Map Registers                        | 100  |

| 9.5.    | 1 P/    | AGE0 Register                             | 100  |

| 9.5.    | 2 P/    | AGE1 Register                             | 101  |

| 9.6     | PCI Ma  | aster Interface                           | 101  |

| 9.6.    | 1 PC    | CI Configuration Cycles                   | 102  |

| 9.6.    | 2 PC    | CI I/O Cycles                             | 102  |

| 9.6.    | .3 PC   | CI Memory Cycles                          | 102  |

| 9.7     | PCI Ho  | ost Operation                             | 103  |

| 9.8     | Interru | ıpt Support                               | 103  |

| 9.9     | Registe | ers                                       | 104  |

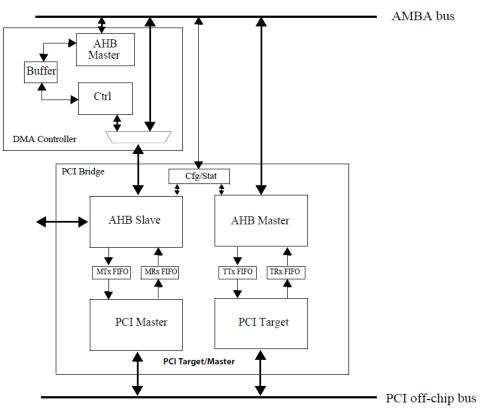

| Chapter | 10:     | DMA Controller for the GRPCI Interface    | 11   |

| Chapt   | er 10:  |                                           | 111  |

| 10.1    | Introdu | uction                                    | 111  |

| 10.2    | Operat  | tion                                      | 111  |

| 10.3    | Registe | ers                                       | 112  |

| Chapter | 11:     | PCI Arbiter, PCIARB                       | 115  |

| Chapt   | er 11:  | · · · · · · · · · · · · · · · · · · ·     | 115  |

| 11.1    | Overvie | ew                                        | 115  |

| 11.2    | Operat  | tion                                      | 115  |

| 11.2    | •       | Scheduling Algorithm                      |      |

| 11.2    | 2.2     | Timeout                                   | 115  |

| 11.2    | 2.3     | Turn-Around                               | 115  |

| 11.2      | 2.4      | Bus Parking                                     | 115 |

|-----------|----------|-------------------------------------------------|-----|

| 11.2      | .5       | Lock                                            | 116 |

| 11.2      | 2.6      | Latency                                         | 116 |

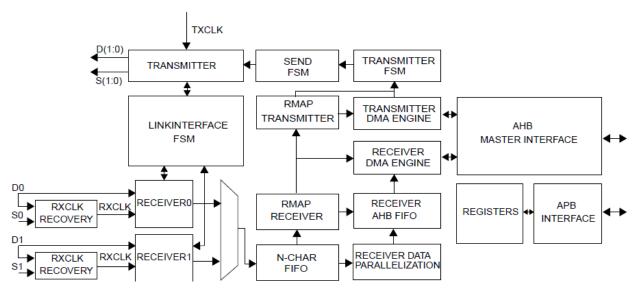

| Chapter : | 12:      | SpaceWire Interface with RMAP support (GRSPW2)  | 117 |

| Chapte    | er 12:   |                                                 | 117 |

| 12.1      | Overvie  | 2W                                              | 117 |

| 12.2      | Operati  | ion                                             | 117 |

| 12.2      | 2.1      | Overview                                        | 117 |

| 12.2      | 2.2      | Protocol Support                                | 118 |

| 12.3      | Link Int | terface                                         | 118 |

| 12.3      | 8.1      | Link Interface FSM                              | 118 |

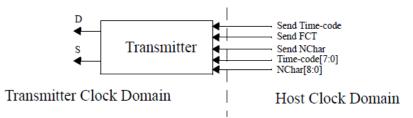

| 12.3      | 8.2      | Transmitter                                     | 119 |

| 12.3      | 3.3      | Receiver                                        | 119 |

| 12.3      | 8.4      | Time Interface                                  | 120 |

| 12.4      | Receive  | er DMA Channels                                 | 121 |

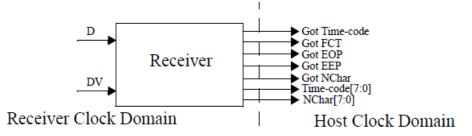

| 12.4      | .1       | Address Comparison and Channel Selection        | 121 |

| 12.4      | .2       | Basic Link Functionally of a Channel            | 122 |

| 12.4      | .3       | Setting up the GRSPW2 for Reception             | 122 |

| 12.4      | .4       | Setting up the Descriptor                       | 123 |

| 12.4      | l.5      | Enabling Descriptors                            | 123 |

| 12.4      | .6       | Setting up the DMA Control Register             | 125 |

| 12.4      | ł.7      | The Effect to the Control Bits during Reception | 125 |

| 12.4      | .8       | Status Bits                                     | 126 |

| 12.4      | l.9      | Error Handling                                  | 126 |

| 12.4      | .10      | Promiscuous Mode                                | 126 |

| 12.5      | Transm   | nitter DMA Channels                             | 127 |

| 12.5      | 5.1      | Basic Functionality of a Channel                | 127 |

| 12.5      | 5.2      | Setting up the GRSPW2 for Transmission          | 127 |

| 12.5      | 5.3      | Enable Descriptors                              | 127 |

| 12.5      | 5.4      | Starting Transmission                           | 128 |

| 12.5      | 5.5      | The Transmission Process                        | 130 |

| 12.5      | 5.6      | The Descriptor Register                         | 130 |

| 12.5      | 5.7      | Error Handling                                  | 130 |

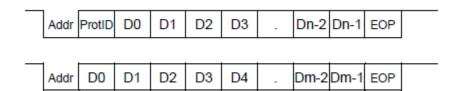

| 12.6      | Remote   | e Memory Access Protocol (RMAP)                 | 131 |

| 12.6      | 5.1      | Fundamentals of the Protocol                    | 131 |

| 12.6      | 5.2      | Implementation                                  | 132 |

| 12.6      | 5.3      | Write Commands                                  | 133 |

| 12.6      | 5.4      | Read Commands                                   | 133 |

| 12.6      | 5.5      | Read-Modify-Write Commands                      | 133 |

| 12.0    | 6.6     | Controls                                                  | . 134 |

|---------|---------|-----------------------------------------------------------|-------|

| 12.7    | AMBA    | Interface                                                 | . 137 |

| 12.7    | 7.1     | APB Slave Interface                                       | . 137 |

| 12.7    | 7.2     | AHB Master Interface                                      | . 137 |

| 12.8    | Space   | Vire Clock Generation                                     | . 137 |

| 12.9    | Registe | er                                                        | . 138 |

| Chapter | 13:     | CAN 2.0 Interface                                         | 148   |

| Chapt   | er 13:  |                                                           | . 148 |

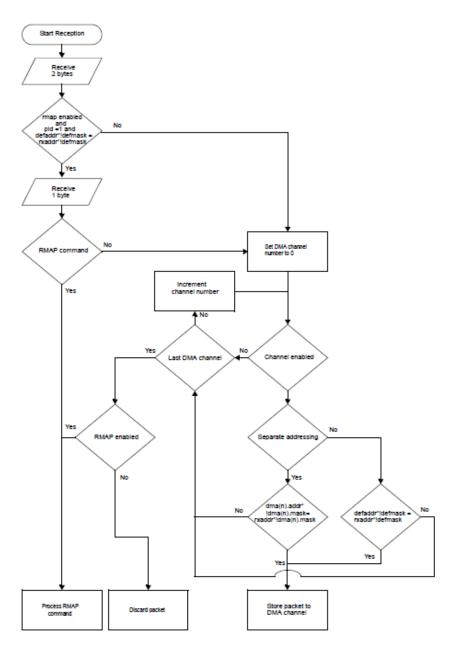

| 13.1    | Overvi  | ew                                                        | . 148 |

| 13.2    | AHB Ir  | iterface                                                  | . 148 |

| 13.3    | BasicC  | AN Mode                                                   | . 148 |

| 13.3    | 3.1     | BasicCAN Register Map (Address 0xFFF20000 and 0xFFF20100) | . 149 |

| 13.3    | 3.2     | Control Register                                          | . 149 |

| 13.3    | 3.3     | Command Register                                          | . 150 |

| 13.3    | 3.4     | Status Register                                           | . 150 |

| 13.3    | 3.5     | Interrupt Register                                        | . 151 |

| 13.3    | 3.6     | Transmit Buffer                                           | . 152 |

| 13.3    | 3.7     | Receive Buffer                                            | . 152 |

| 13.3    | 3.8     | Acceptance Filter                                         | . 152 |

| 13.4    | PeliCA  | N Mode                                                    | . 152 |

| 13.4    | 4.1     | PeliCAN Register Map (Address 0xFFF20000 and 0xFFF20100)  | . 152 |

| 13.4    | 4.2     | Mode Register                                             | . 153 |

| 13.4    | 4.3     | Command Register                                          | . 154 |

| 13.4    | 4.4     | Status Register                                           | . 155 |

| 13.4    | 4.5     | Interrupt Register                                        | . 155 |

| 13.4    | 4.6     | Interrupt Enable Register                                 | . 156 |

| 13.4    | 4.7     | Arbitration Lost Capture Register                         | . 156 |

| 13.4    | 4.8     | Error Code Capture Register                               | . 157 |

| 13.4    | 4.9     | Error Warning Limit Register                              |       |

| 13.4    | 4.10    | RX Error Counter Register, Offset 14                      | . 158 |

| 13.4    | 4.11    | TX Error Counter Register, Offset 15                      | . 158 |

| 13.4    | 4.12    | Transmit Buffer                                           | . 158 |

| 13.4    | 4.13    | Receiver Buffer                                           | . 160 |

| 13.4    | 4.14    | Acceptance Filter                                         | . 162 |

| 13.4    | 4.15    | RX Message Counter                                        | . 163 |

|         |         | on Registers                                              |       |

| 13.     |         | Clock Divider Register                                    |       |

| 13.     | 5.2     | Bus Timing 0                                              |       |

| 13.     | 5.3     | Bus Timing 1                                              | . 164 |

| 13.6 C     | CAN-OC vs SJA1000                                           |     |

|------------|-------------------------------------------------------------|-----|

| Chapter 14 | 4: Ethernet Media Access Controller (MAC) with EDCL Support |     |

| Chapter    | r 14:                                                       |     |

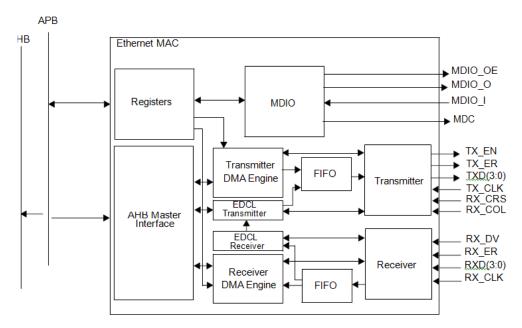

| 14.1 O     | Overview                                                    |     |

| 14.2 O     | Operation                                                   | 166 |

| 14.2.1     | 1 System Overview                                           |     |

| 14.2.2     | 2 Protocol Support                                          |     |

| 14.2.3     | 3 Hardware Requirements                                     |     |

| 14.2.4     | 4 Transmitter DMA Interface                                 |     |

| 14.2.5     | 5 Setting up a Descriptor                                   |     |

| 14.2.6     | 6 Starting Transmissions                                    |     |

| 14.2.7     | 7 Descriptor Handling After Transmission                    |     |

| 14.2.8     | 8 Setting up the Data for Transmission                      |     |

| 14.2.9     | 9 Receiver DMA Interface                                    |     |

| 14.2.1     | 10 Setting up Descriptors                                   |     |

| 14.2.1     | 11 Starting Reception                                       |     |

| 14.2.1     | 12 Descriptor Handling After Reception                      |     |

| 14.2.1     | 13 Reception with AHB Errors                                |     |

| 14.2.1     | 14 MDIO Interface                                           |     |

| 14.2.1     | 15 Ethernet Debug Communication Link (EDCL)                 |     |

| 14.2.1     | 16 Media Independent Interfaces                             |     |

| 14.2.1     | 17 Software Drivers                                         |     |

| 14.3 R     | Registers                                                   |     |

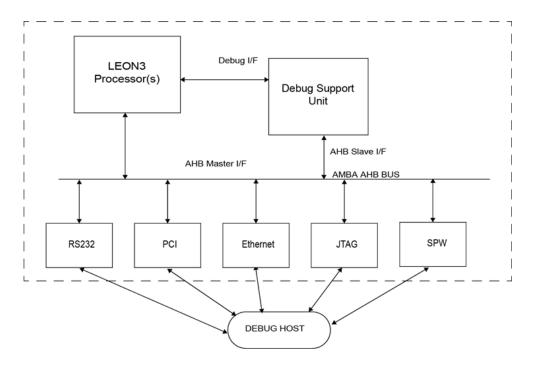

| Chapter 15 | 5: Hardware Debug Support                                   |     |

| Chapter    | r 15:                                                       |     |

| 15.1 O     | Overview                                                    |     |

| 15.2 O     | Operation                                                   |     |

| 15.3 A     | AHB Trace Buffer                                            |     |

| 15.4 Ir    | Instruction Trace Buffer                                    |     |

| 15.5 D     | DSU Memory Map                                              |     |

| 15.6 D     | DSU Registers                                               |     |

| 15.6.1     | 1 DSU Control Register                                      |     |

| 15.6.2     | 2 DSU Break and Single-Step Register                        |     |

| 15.6.3     | 3 DSU Trap Register                                         |     |

| 15.6.4     | 4 DSU Trace Buffer Time Tag Counter Register                |     |

| 15.6.5     | 5 DSU ASI Diagnostic Access Register                        |     |

| 15.6.6     | 6 AHB Trace Buffer Control Register                         |     |

| 15.6.7     | 7 AHB Trace Buffer Index Register                           | 190 |

| 15.6.8     | 8 AHB Trace Buffer Breakpoint Registers                     | 190 |

| 15.6.       | 9        | Instruction Trace Control Registers                                               | . 192 |

|-------------|----------|-----------------------------------------------------------------------------------|-------|

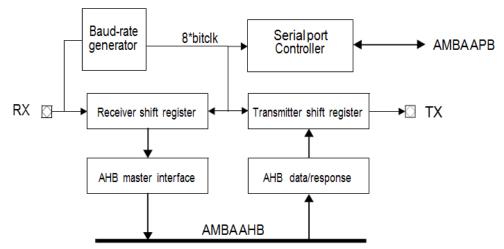

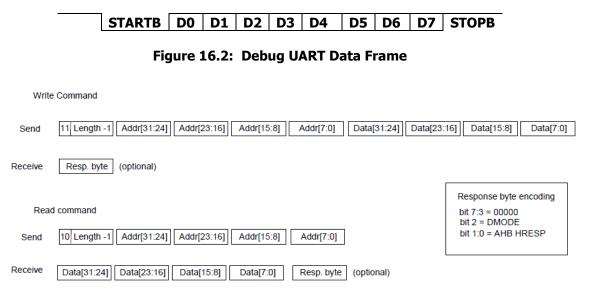

| Chapter 16: |          | Serial Debug Link                                                                 | 193   |

| Chapter     | r 16:    |                                                                                   | . 193 |

| 16.1 (      | Overvie  | 2W                                                                                | . 193 |

| 16.2 0      | Operat   | ion                                                                               | . 193 |

| 16.2.       | 1        | Transmission Protocol                                                             | . 193 |

| 16.2.       | 2        | Baud Rate Generator                                                               | . 194 |

| 16.3 F      | Registe  | ers                                                                               | . 194 |

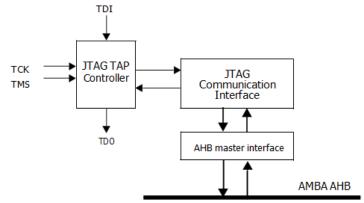

| Chapter 1   | .7:      | JTAG Debug Link                                                                   | 197   |

| Chapter     | r 17:    |                                                                                   | . 197 |

| 17.1 (      | Overvie  | 2W                                                                                | . 197 |

| 17.2 (      | Operat   | ion                                                                               | . 197 |

| 17.2.       | 1        | Transmission Protocol                                                             | . 197 |

| 17.2.       | 2        | Registers                                                                         | . 199 |

| 17.3 E      | Bounda   | ary Scan                                                                          | . 199 |

| Chapter 1   | .8:      | CLKGATE Clock Gating Unit                                                         | 200   |

| Chapter     | r 18:    |                                                                                   | . 200 |

| 18.1 (      | Overvie  | ew                                                                                | . 200 |

| 18.2 (      | Operat   | ion                                                                               | . 200 |

| 18.3 F      | Registe  | ers                                                                               | . 201 |

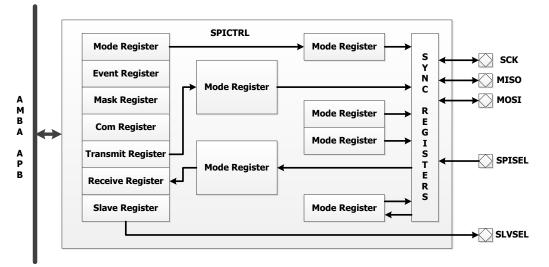

| Chapter 1   | .9:      | SPI Controller (Only applicable to the UT700)                                     | 202   |

| Chapter     | r 19:    |                                                                                   | . 202 |

| 19.1 (      | Overvie  | 2W                                                                                | . 202 |

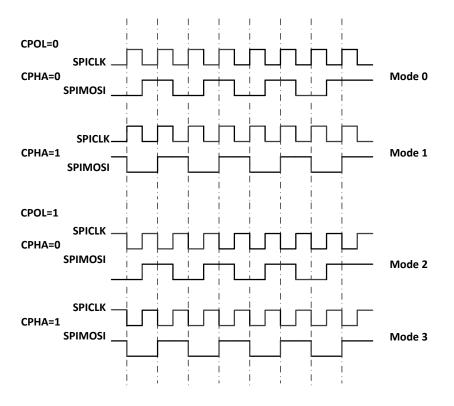

| 19.2 (      | Operat   | ion                                                                               | . 202 |

| 19.2.       | 1        | SPI Transmission Protocol                                                         | . 202 |

| 19.2.       | 2        | Receive and Transmit Queues                                                       | . 203 |

| 19.2.       | 3        | Clock Generation                                                                  | . 203 |

| 19.2.       | 4        | Operation (Master-Only)                                                           | . 204 |

| 19.3 F      | Registe  | ers                                                                               | . 204 |

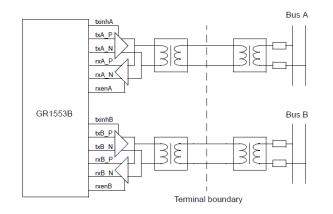

| Chapter 2   | 20:      | Dual Redundant MTL-STD-1553B Interface (GR1553B) (Only applicable to the UT70 212 | 0)    |

| Chapter     | r 20:    |                                                                                   | . 212 |

| 20.1 0      | Overvie  | 2W                                                                                | . 212 |

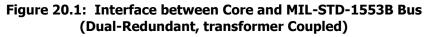

| 20.2 E      | Electric | al Interface                                                                      | . 212 |

| 20.3 (      | Operat   | ion                                                                               | . 213 |

| 20.3.       | 1        | Operation Modes                                                                   | . 213 |

| 20.3.       | 2        | Register Interface                                                                | . 213 |

| 20.3.       | 3        | Interrupting                                                                      | . 213 |

| 20.3.       | 4        | MIL-STD-1553 Codec                                                                | . 213 |

| 20.4 Bus Co    | ontroller Operation                   |     |

|----------------|---------------------------------------|-----|

| 20.4.1         | Overview                              |     |

| 20.4.2         | Timing Control                        |     |

| 20.4.3         | Bus Selection                         |     |

| 20.4.4         | Secondary Transfer List               |     |

| 20.4.5         | Interrupt Generation                  | 215 |

| 20.4.6         | Transfer List Format                  |     |

| 20.5 Remot     | e Terminal Operation                  | 220 |

| 20.5.1         | Overview                              | 220 |

| 20.5.2         | Data Transfer Handling                | 220 |

| 20.5.3         | Mode Codes                            |     |

| 20.5.4         | Event Log                             |     |

| 20.5.5         | Sub Address Table Format              | 223 |

| 20.6 Bus M     | onitor Operation                      | 226 |

| 20.6.1         | Overview                              | 226 |

| 20.6.2         | No-Response Handling                  | 226 |

| 20.6.3         | Log Entry Format                      | 226 |

| 20.7 Clockii   | ng and Reset                          |     |

| 20.8 Regist    | ers                                   |     |

| Appendix A: Re | egister Format                        |     |

| Appendix B: Er | rata                                  |     |

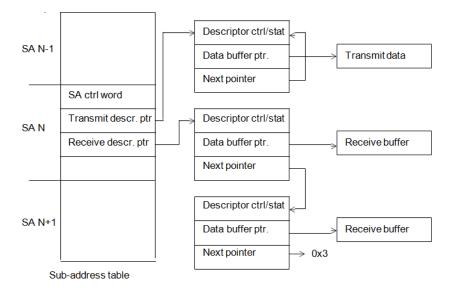

|                | TD-1553 NOISE REJECTION LIMITATIONS   |     |

| Overview/Pro   | blem Statement                        |     |

| Technical Bac  | ckground                              |     |

|                | ription of the Problem                |     |

| •              |                                       |     |

| Workarounds    | · · · · · · · · · · · · · · · · · · · | 250 |

|                |                                       |     |

## Chapter 1: Introduction

## 1.1 Scope

Cobham has combined the UT699E and UT700 LEON Microprocessor Manuals as of February 27, 2017. The two products are very similar and we have noted through the UT699E/UT700 Manual any differences.

This document describes the UT699E/UT700 LEON 3FT microprocessor, a pipelined, monolithic, highperformance, fault-tolerant SPARC<sup>™</sup> V8 compliant processor, designed using a combination of hardened flip-flops and TMR schemes to ensure reliable operations in a typical HiRel environment. The UT699E/UT700 provides a 32-bit/33MHz PCI (Revision 2.1 compatible) master/target interface with DMA and arbitration capabilities. An AMBA (Rev. 2.0) bus interface integrates the LEON 3FT CPU, SpaceWire, Ethernet MAC, memory controller, PCI, Mil-Std-1553, SPI, CAN bus, UART, and programmable general purpose input/output cores.

Industry standard SPARC V8 compilers and kernels support the UT699E/UT700 software development environment. A full software development suite includes a C/C++ cross-compiler based on the GNU Compiler Collection (GCC) and POSIX-compliant Newlib embedded C-library. Contact Cobham Gaisler for C/C++ cross-compiler and C-library support. The Bare C Compiler (BCC), based upon GCC, produces a small run-time kernel with interrupt support and PThreads library. Software development suite runs on either Windows or Linux operating systems. SPARC compliant ports of the RTEMS and VxWorks RTOS support multi-thread applications.

The UT699E LEON 3FT microprocessor is based on IP cores from Cobham Gaisler's GRLIB Intellectual Property (IP) library and uses a plug-and-play system-on-a-chip design approach.

#### **1.2** Differences between UT699, UT699E, and UT700

Table 1.1 below outlines the main differences between UT699, UT699E, and UT700.

| Parameter              | UT699                       | UT699E                   | UT700                   |

|------------------------|-----------------------------|--------------------------|-------------------------|

| 1553 BC, RT, BM        | Not Implement               | Not Implement            | Yes                     |

| AHB trace buffer       | 128 lines                   | 256 lines                | 256 lines               |

| Clocking               | Processor and AHB in        | AHB can be clocked       | AHB can be clocked      |

|                        | same clock domain           | at 1/2 processor clock   | at 1/2 processor clock  |

| Ethernet debug link    | Not Implemented             | Yes                      | Yes                     |

| LEON 3FT cache size    | 2 x 4 kbyte icache, 2 x 4   | 4 x 4 kbyte icache, 4 x  | 4 x 4 kbyte icache, 4 x |

|                        | Kbyte data cache            | 4 Kbyte dcache           | 4 Kbyte dcache          |

| LEON 3FT load delay    | Pipeline load delay is 2    | Pipeline load delay is 1 | Pipeline load delay is  |

|                        |                             |                          | 1                       |

| LEON 3FT data cache    | Data cache fetches only     | Data cache fetches       | Data cache fetches      |

| fetch                  | missed word                 | whole line (16 bytes)    | whole line (16 bytes)   |

| LEON 3FT MMU           | 8 + 8 I/D TLB entries       | 16 + 16 I/D TLB          | 16 + 16 I/D TLB         |

|                        | 2 clocks stall on write hit | entries No stall on      | entries No stall on     |

|                        |                             | write hit                | write hit               |

| LEON 3FT FPU           | GRFPU                       | GRFPU with               | GRFPU with              |

|                        |                             | instruction FIFO and     | instruction FIFO and    |

|                        |                             | correction of UT699      | correction of UT699     |

|                        |                             | FPU errata               | FPU errata              |

| LEON 3FT register file | Protected against SEU       | Protected against SEU    | Protected against SEU   |

#### Table 1.1: UT699, UT699E and UT700 Differences

| Parameter                                  | UT699                             | UT699E                         | UT700                          |

|--------------------------------------------|-----------------------------------|--------------------------------|--------------------------------|

| rarameter                                  | using 7-bit                       | using TMR                      | using TMR                      |

|                                            | BCH (SEC/DED)                     | -                              | -                              |

| LEON 3FT Multiplier                        | 16-bit multiplier                 | 32-bit multiplier              | 32-bit multiplier              |

|                                            | requiring 5 clocks per            | requiring 1 clock per          | requiring 1 clock per          |

|                                            | MUL instruction                   | MUL instruction                | MUL instruction                |

| LEON 3FT instruction<br>trace              | 128 lines                         | 256 lines                      | 256 lines                      |

| LEON 3FT cache freeze                      | Cache freeze is available         | Only instruction cache         | Only instruction cache         |

|                                            | for data and instruction<br>cache | freeze is available            | freeze is available            |

| LEON 3FT IU                                | Pipeline restarts on              | Correction without             | Correction without             |

|                                            | correction                        | pipeline restart               | pipeline restart               |

| Memory controller                          | BCH EDAC only                     | BCH and Reed-                  | BCH and Reed-                  |

| ,                                          | ,                                 | Solomon protection of<br>SDRAM | Solomon protection of<br>SDRAM |

| PCI                                        | Parity checking errata            | Correction of parity           | Correction of parity           |

| -                                          | ,                                 | checking errata                | checking errata                |

| AMBA and memory                            | AMBA and memory                   | AMBA and memory                | AMBA and memory                |

| bus                                        | bus                               | bus                            | bus with support for           |

|                                            |                                   |                                | clock division by 2            |

|                                            |                                   |                                | (NODIV)                        |

| SpaceWire write                            | Supported                         | No longer required             | No longer required             |

| synchronization error                      |                                   |                                |                                |

| bit                                        |                                   |                                |                                |

| SpaceWire                                  | GRSPW (with 2 RMAP)               | GRSPW2 (with 4<br>RMAP)        | GRSPW2 (with 4<br>RMAP)        |

| SpaceWire RMAP error                       | No support for RMAP               | RMAP invalid                   | RMAP invalid                   |

| code                                       | invalid destination               | destination address            | destination address            |

|                                            | address error code                | error code is supported        | error code is supported        |

| SpaceWire timer and<br>disconnect register | Supported                         | No longer required             | No longer required             |

| SpaceWire CLK to                           | SPW_CLK $\leq 4 \text{ x}$        | SPW CLK $\leq 8 \text{ x}$     | SPW_CLK $\leq 8 \times$        |

| system clock                               | SYS_CLK                           | SYS CLK                        | SYS_CLK                        |

| relationship                               | _                                 | _                              | _                              |

| SpaceWire receive                          | $RxCLK \le 2 \times SYS_CLK$      | No longer tied to              | No longer tied to              |

| clock to                                   | _                                 | SYS_CLK, relationship          | SYS_CLK, relationship          |

| system clock                               |                                   | is now related to the          | is now related to the          |

| relationship                               |                                   | SPW_CLK                        | SPW_CLK                        |

|                                            |                                   | SPW_CLK $\geq$ 3/4             | SPW_CLK $\geq$ 3/4             |

|                                            |                                   | receive data rate              | receive data rate              |

|                                            |                                   | (max)                          | (max)                          |

| SpaceWire Loopback                         | Not Supported                     | Supports internal              | Supports internal              |

|                                            |                                   | loopback                       | loopback                       |

| Interrupt Controller                       | Not Supported                     | Supported                      | Supported                      |

| status                                     |                                   |                                |                                |

| register with extended                     |                                   |                                |                                |

| interrupts and CPU                         |                                   |                                |                                |

| power-down status                          |                                   |                                |                                |

| SPI Controller                             | Not Implement                     | Not Implement                  | Supported                      |

The UT699E is similar to the UT700; however, both SPI and 1553 are unavailable in the UT699E. The UT699 cache coherency is handled by software while the UT699E/UT700 cache coherency are supported by hardware through bus snooping.

## 1.3 Architecture

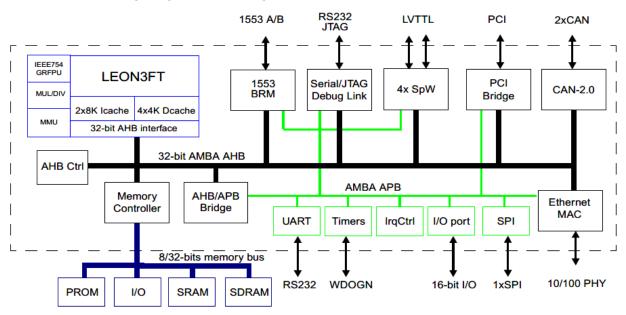

The UT699E/UT700 consists of the following components:

- LEON 3FT microprocessor core

- 8/16/32-bit memory controller

- Four SpaceWire links

- Two CAN-2.0 interfaces

- UART

- One timer unit with 4 timers

- One Extended Interrupt Controller

- One 16-bit I/O port

- Serial/JTAG debug links

- 10/100 Mbit/s Ethernet MAC

- MIL-STD-1553B controller (BC, RT, BM) (only applicable to UT700)

- One SPI Controller (only applicable to UT700)

- One 32-bit PCI Bridge

The following image is a block diagram of the UT699E/UT700 architecture.

#### Figure 1.1: UT699E/UT700 Functional Block Diagram

The design is based on the following IP cores from the GRLIB IP library:

Table 1.2: GLIB IP Cores used in UT699E/UT700

| CORE     | FUNCTION                             | VENDOR ID | DEVICE ID | REV |

|----------|--------------------------------------|-----------|-----------|-----|

| LEON 3FT | SPARC V8 32-bit processor            | 0x01      | 0x053     | 0x0 |

| DSU3     | Debug support unit                   | 0x01      | 0x004     | 0x1 |

| IRQMP    | Interrupt controller                 | 0x01      | 0x00D     | 0x3 |

| APBCTRL  | AHB/APB Bridge                       | 0x01      | 0x006     | 0x0 |

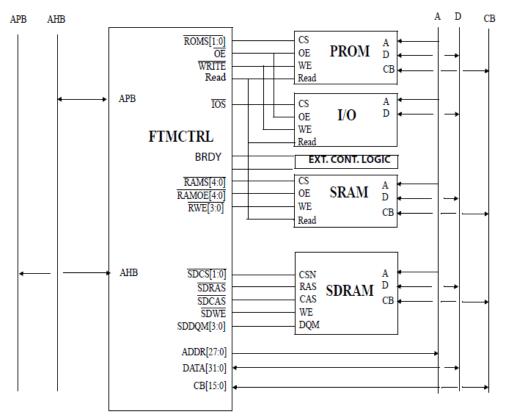

| FTMCTRL  | 8/32-bit memory controller with EDAC | 0x01      | 0x054     | 0x1 |

| AHBSTAT  | AHB failing address register         | 0x01      | 0x052     | 0x0 |

| AHBUART  | Serial/AHB debug interface           | 0x01      | 0x007     | 0x0 |

| AHBJTAG  | JTAG/AHB debug interface             | 0x01      | 0x01C     | 0x1 |

| GRSPW2   | SpaceWire link with RMAP             | 0x01      | 0x029     | 0x0 |

| CORE    | FUNCTION                          | VENDOR ID | <b>DEVICE ID</b> | REV |

|---------|-----------------------------------|-----------|------------------|-----|

| GRPCI   | 32-bit PCI bridge                 | 0x01      | 0x014            | 0x0 |

| PCIDMA  | DMA controller for PCI bridge     | 0x01      | 0x016            | 0x0 |

| CANMC   | Dual CAN-2.0 interface            | 0x01      | 0x019            | 0x1 |

| GRETH   | 10/100 Ethernet MAC with EDCL     | 0x01      | 0x01D            | 0x0 |

| APBUART | 8-bit UART with FIFO              | 0x01      | 0x00C            | 0x1 |

| GPTIMER | Modular timer unit                | 0x01      | 0x011            | 0x0 |

| GPIO    | General purpose I/O port          | 0x01      | 0x01A            | 0x1 |

| CLKGATE | Clock gating module               | 0x01      | 0x02C            | 0x0 |

| PCIARB  | PCI Arbiter                       | 0x04      | 0x10             | 0x0 |

| GR1553B | Advanced MIL-STD-1553B BC, RT, BM | 0x01      | 0x04D            | 0x0 |

| SPICTRL | SPI controller (master)           | 0x01      | 0x02D            | 0x5 |

| GRGPREG | General purpose register          | 0x01      | 0x087            | 0x0 |

## 1.4 Memory Map

**Table 1.3** is a memory map of the internal AHB/APB buses:

## Table 1.3: Internal Memory Map

| CORE              | ADDRESS RANGE                                         | BUS | Link       |

|-------------------|-------------------------------------------------------|-----|------------|

| FTMCTRL           | 0x00000000 - 0x1FFFFFFF : PROM area                   | AHB | Chapter 3: |

|                   | 0x20000000 - 0x3FFFFFFF : I/O area                    |     |            |

|                   | 0x40000000 - 0x7FFFFFFF : SRAM/SDRAM area             |     |            |

| APBCTRL1          | 0x80000000 - 0x800FFFFF : APB bridge                  | AHB |            |

| FTMCTRL           | 0x80000000 - 0x800000FF : Registers                   | APB | Chapter 3: |

| APBUART           | 0x80000100 - 0x800001FF : Registers                   | APB | Chapter 6: |

| IRQMP             | 0x80000200 - 0x800002FF : Registers                   | APB | Chapter 5: |

| GPTIMER           | 0x80000300 - 0x800003FF : Registers                   | APB | Chapter 7: |

| PCI               | 0x80000400 - 0x800004FF : PCI DMA control registers   | APB | Chapter 9: |

| PCI DMA CTRL      | 0x80000500 - 0x800005FF : Registers                   | APB | Chapter    |

|                   |                                                       |     | 10:        |

| CLKGATE           | 0x80000600 - 0x800006FF : Registers                   | APB | Chapter    |

|                   |                                                       |     | 18:        |

| AHBUART           | 0x80000700 - 0x800007FF : Registers                   | APB | Chapter 6: |

| PCIARB            | 0x80000800 - 0x800008FF : Registers                   | APB | Chapter    |

|                   |                                                       |     | 11:        |

| GPIO              | 0x80000900 - 0x800009AA : Registers                   | APB | Chapter 8: |

| SPW1              | 0x80000A00 - 0x80000AFF : Registers                   | APB | Chapter    |

|                   |                                                       |     | 12:        |

| SPW2              | 0x80000B00 - 0x80000BFF : Registers                   | APB | Chapter    |

|                   |                                                       |     | 12:        |

| SPW3              | 0x80000C00 - 0x80000CFF : Registers                   | APB | Chapter    |

| 56002             | 0x80000C00 - 0x80000CFF . Registers                   | APD | 12:        |

| SPW4              | 0x80000D00 - 0x80000DFF : Registers                   | APB | Chapter    |

| JEAN              | 0x00000000 - 0x00000011 . Registers                   | AFD | 12:        |

| ETH               | 0x80000E00 - 0x80000EFF : Registers                   | APB | Chapter    |

| L ! ! !           |                                                       | AFD | 14:        |

| AHBSTAT           | 0x80000F00 - 0x80000FFF : Registers                   | APB |            |

| Reserved          | 0x80001000 - 0x800FEFFF : Unused                      | APB |            |

| APB plug-and-play | 0x800FF000 - 0x800FFFFF : Plug-and-play configuration | APB |            |

| APBCTRL2          | 0x80100000 - 0x801FFFFF : APB bridge                  | AHB |            |

| 1553B             | 0x80100000 - 0x801000FF : Registers                   | APB | Chapter    |

| CORE              | CORE ADDRESS RANGE                                                           |     | Link           |

|-------------------|------------------------------------------------------------------------------|-----|----------------|

|                   |                                                                              |     | 20:            |

| SPICTRL           | 0x80100100 - 0x801001FF : Registers                                          | APB | Chapter<br>19: |

| GPREG             | 0x80100200 - 0x801002FF : Registers                                          | APB | Chapter 4:     |

| APB plug-and-play | 0x801FF000 - 0x801FFFFF : Plug-and-play configuration                        | APB |                |

| Reserved          | 0x80200000 - 0x8FFFFFFF : Unused                                             | APB |                |

| DSU3              | 0x9000000 - 0x9FFFFFF : Registers                                            | AHB | Chapter<br>15: |

| Reserved          | 0xA0000000 - 0xBFFFFFFF : Unused                                             | APB |                |

| PCI               | 0xC0000000 - 0xFFEFFFFF : PCI Bus<br>0xFFF00000 - 0xFFF1FFFF : PCI I/O space | AHB | Chapter 9:     |

| CANOC1            | 0xFFF20000 - 0xFFF200FF : Registers                                          | AHB | Chapter<br>13: |

| CANOC2            | 0xFFF20100 - 0xFFF201FF : Registers                                          | AHB | Chapter<br>13: |

| Reserved          | 0xFFF20200 - 0xFFFFEFFF : Unused                                             | AHB |                |

| AHB plug-and-play | 0xFFFFF000 - 0xFFFFFFFF : Plug-and-play configuration                        | AHB |                |

Access to addresses outside the ranges described above will return an AHB error response. Only 32bit (word) accesses are supported for APB areas.

#### 1.5 Interrupts

The interrupts are routed to the IRQMP interrupt controller and forwarded to the LEON 3FT processor. **Table 1.4** indicates the interrupt assignments:

| CORE    | INTERRUPT # | FUNCTION                   |

|---------|-------------|----------------------------|

| AHBSTAT | 1           | AHB bus error              |

| APBUART | 2           | UART RX/RX interrupt       |

| PCI     | 3           | PCI DMA interrupt          |

| CAN1    | 4           | CAN1 interrupt             |

| CAN2    | 5           | CAN2 interrupt             |

| GPTIMER | 6, 7, 8, 9  | Timer underflow interrupts |

| IRQMP   | 9           | Extended interrupt vector  |

| SPW1    | 10          | SpaceWire1 interrupt       |

| SPW2    | 11          | SpaceWire2 interrupt       |

| SPW3    | 12          | SpaceWire3 interrupt       |

| SPW4    | 13          | SpaceWire4 interrupt       |

| ETH     | 14          | Ethernet interrupt         |

| 1553B   | 17          | MIL-STD-1553 BC, RT, BM    |

| 12220   | 17          | interrupt                  |

| SPICTRL | 18          | SPI controller interrupt   |

| GPIO    | 1 - 15      | External I/O interrupt     |

#### Table 1.4: Interrupt Assignments

#### 1.6 Signals

The device has the following external signals, **Table 1.5**. The reset value for any signal is undefined if not otherwise indicated.

#### Table 1.5: Signal Assignments

| PIN NAME                                                         | FUNCTION              | <b>RESET VALUE</b> | DESCRIPTION                                                                                                                                                       |

|------------------------------------------------------------------|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSCLK                                                           | I                     |                    | Main system clock                                                                                                                                                 |

| NODIV                                                            | I                     |                    | Clock divider input. Set to '1' for 1x memory clock, '0' for 1/2x memory clock, relative to SYSCLK (UT700)                                                        |

| RESET                                                            | IS                    |                    | System reset                                                                                                                                                      |

| ERROR1                                                           | OD                    |                    | Processor error mode indicator. This is an active low output.                                                                                                     |

| WDOG1                                                            | OD                    |                    | Watchdog indicator. This is an active low output.                                                                                                                 |

| ADDR[27:0]                                                       | 0                     | [000]              | Address bus                                                                                                                                                       |

| DATA[31:0]                                                       | I/O                   | High-z             | Data bus                                                                                                                                                          |

| CB[15:0]                                                         | I/O                   | High-z             | EDAC checkbits                                                                                                                                                    |

| WRITE                                                            | 0                     | 1                  | Write strobe for PROM and I/O                                                                                                                                     |

| OEN                                                              | 0                     | 1                  | Output enable for PROM and I/O                                                                                                                                    |

| IOS                                                              | 0                     | 1                  | I/O area chip select                                                                                                                                              |

| ROMS[1:0]                                                        | 0                     | 1                  | PROM chip select                                                                                                                                                  |

| RWE[3:0]                                                         | 0                     | 1                  | SRAM write enable strobe                                                                                                                                          |

| RAMOE[4:0]                                                       | 0                     | 1                  | SRAM output enable                                                                                                                                                |

| RAMS[4:0]                                                        | 0                     | 1                  | SRAM chip select                                                                                                                                                  |

| READ                                                             | 0                     | 1                  | SRAM, PROM, and I/O read indicator                                                                                                                                |

| BEXC                                                             | I                     |                    | Bus exception                                                                                                                                                     |

| BRDY                                                             | I                     |                    | Bus ready                                                                                                                                                         |

| SDCLK                                                            | 0                     | 1                  | SDRAM clock                                                                                                                                                       |

| SDRAS                                                            | 0                     | 1                  | SDRAM row address strobe                                                                                                                                          |

| SDCAS                                                            | 0                     | 1                  | SDRAM column address strobe                                                                                                                                       |

| SDWEN                                                            | 0                     | 1                  | SDRAM write enable                                                                                                                                                |

| SDCS[1:0]                                                        | 0                     | 1                  | SDRAM chip select                                                                                                                                                 |

| SDDQM[3:0]                                                       | 0                     | 1                  | SDRAM data mask                                                                                                                                                   |

| CAN_RXD[1:0]                                                     | I                     |                    | CAN receive data                                                                                                                                                  |

| CAN_TXD[1:0]                                                     | 0                     | 1                  | CAN transmit data                                                                                                                                                 |

| DSUACT                                                           | 0                     | 0                  | DSU mode indicator                                                                                                                                                |

| DSUEN                                                            | I                     |                    | DSU enable                                                                                                                                                        |

| DSURX                                                            | I                     |                    | DSU UART receive data                                                                                                                                             |

| DSUTX<br>TRST                                                    | 0<br>I                | 1                  | DSU UART transmit data<br>JTAG reset                                                                                                                              |

| TMS                                                              | I<br>T                |                    | JTAG test mode select                                                                                                                                             |

| ТСК                                                              | I<br>T                |                    | JTAG clock                                                                                                                                                        |

| TDI                                                              | I                     |                    | JTAG test data input                                                                                                                                              |

| TDO                                                              | 0                     |                    | JTAG test data output                                                                                                                                             |

| EMDC                                                             | 0                     | 0                  | Ethernet media interface clock                                                                                                                                    |

| ERX_CLK                                                          | I                     |                    | Ethernet RX clock                                                                                                                                                 |

| EMDIO                                                            | I/O                   | High-z             | Ethernet media interface data                                                                                                                                     |

| ERX_COL                                                          | I                     |                    | Ethernet collision error                                                                                                                                          |

| ERX_CRS                                                          | I                     |                    | Ethernet carrier sense detect                                                                                                                                     |

|                                                                  |                       |                    |                                                                                                                                                                   |

| —                                                                |                       |                    | •                                                                                                                                                                 |

|                                                                  |                       |                    |                                                                                                                                                                   |

|                                                                  |                       |                    |                                                                                                                                                                   |

| ERX_CRS<br>ERX_DV<br>ERX_ER<br>ERXD[3:0]<br>ETXD[3:0]<br>ETX_CLK | I<br>I<br>I<br>O<br>I |                    | Ethernet carrier sense detect<br>Ethernet receiver data valid<br>Ethernet reception error<br>Ethernet receive data<br>Ethernet transmit data<br>Ethernet TX clock |

| PIN NAME           | FUNCTION         | <b>RESET VALUE</b> | DESCRIPTION                                  |

|--------------------|------------------|--------------------|----------------------------------------------|

| ETX_EN             | 0                | 0                  | Ethernet transmit enable                     |

| ETX_ER             | 0                | 0                  | Ethernet transmit error                      |

| EMDINT             | Ι                |                    | Ethernet management interface data interrupt |

| EDCLDIS            | Ι                |                    | Ethernet debug link disable                  |

| GPIO[15:0]         | I/O              | High-z             | General Purpose I/O                          |

| SPW_CLK            | I                |                    | SpaceWire clock                              |

| SPW_RXS[3:0]       | I                |                    | SpaceWire receive strobe                     |

| SPW_RXD[3:0]       | I                |                    | SpaceWire receive data                       |

| SPW_TXS[3:0]       | 0                | 0                  | SpaceWire transmit strobe                    |

| SPW_TXD[3:0]       | 0                | 0                  | SpaceWire transmit data                      |

| RXD<br>TXD         | I<br>O           | 1                  | UART receive data UART transmit data         |

| PCI_AD[31:0]       | PCI-I/O          | High-z             | Bit 0 of PCI address and data bus            |

|                    | PCI-I/O<br>PCI-I |                    | PCI reset input                              |

| PCI_RST<br>PCI_CLK | PCI-I<br>PCI-I   |                    | PCI clock input                              |

|                    |                  |                    | •                                            |

| PCI_CBE[3:0]       | PCI-I/O          | High-z             | PCI bus command and byte enable              |

| PCI_PAR            | PCI-I/O          | High-z             | PCI parity checkbit                          |

| PCI_FRAME1         | PCI-3            | High-z             | PCI cycle frame indicator                    |

| PCI_IRDY1          | PCI-3            | High-z             | PCI initiator ready indicator                |

| PCI_TRDY1          | PCI-3            | High-z             | PCI target ready indicator                   |

| PCI_STOP1          | PCI-3            | High-z             | PCI target stop request                      |

| PCI_DEVSEL1        | PCI-3            | High-z             | PCI device select                            |

| PCI IDSEL          | PCI-I            |                    | PCI initializer device select                |

| —                  |                  | lliah -            | PCI request to arbiter in point-to-point     |

| PCI_REQ            | PCI-O            | High-z             | configuration                                |

| PCI_GNT            | PCI-I            |                    | PCI bus access indicator in point-to-point   |

|                    |                  |                    | configuration                                |

| PCI_HOST           | PCI-I            |                    | PCI host enable input                        |

| PCI_ARB_REQ[7:0]   | PCI-I            |                    | PCI arbiter bus request                      |

| PCI_ARB_GNT[7:0]   | PCI-O            | High-z             | PCI arbiter bus grant                        |

| PCI_PERR1          | PCI-3            | High-z             | PCI parity error indicator                   |

| 1553CLK            | I                |                    | MIL-STD-1553B Clock                          |

| 1553TXINA          | 0                | High-z             | MIL-STD-1553B Transmit Inhibit A             |

| 1553RXA            | I                |                    | MIL-STD-1553B Receive Positive A             |

| 1553RXA            | Ι                |                    | MIL-STD-1553B Receive Negative A             |

| 1553TXA            | 0                | High-z             | MIL-STD-1553B Transmit Positive A            |

| 1553TXA            | 0                | High-z             | MIL-STD-1553B Transmit Negative A            |

| 1553RXENA          | 0                | High-z             | MIL-STD-1553B Receive Enable A               |

| 1553TXINB          | 0                | High-z             | MIL-STD-1553B Transmit Inhibit B             |

| 1553RXB            | I                |                    | MIL-STD-1553B Receive Positive B             |

| 1553RXB            | I                |                    | MIL-STD-1553B Receive Negative B             |

| 1553TXB            | 0                | High-z             | MIL-STD-1553B Transmit Positive B            |

| 1553TXB            | 0                | High-z             | MIL-STD-1553B Transmit Negative B            |

| 1553RXENB          | 0                | High-z             | MIL-STD-1553B Receive Enable B               |

| SPI_SCK            | 0                |                    | SPI Clock                                    |

| SPIMOSI            | 0                |                    | SPI Master Out Slave In                      |

| SPIMISO            | I                |                    | SPI Master In Slave Out                      |

| SPISLVSEL          | 0                | High               | SPI Select                                   |

#### Notes:

- 1. These pins require a pull-up resistor tied to V<sub>DD</sub>. Specified resistor values are based on design requirements or as specified in the PCI Local Bus Specification Revision 2.1, Section **4.3.3**.

- 2. CB[15:8] is reset to a high logic level.

## 1.7 Clocking

## 1.7.1 Clock Inputs

Table 1.6 shows the clock inputs to the UT699E/UT700:

#### Table 1.6:Clock Inputs

| SIGNAL   | DESCRIPTION                                                               |

|----------|---------------------------------------------------------------------------|

| SYSCLK   | Main system clock. The processor and AHB bus is clocked directly by CLK.  |

| PCI_CLK  | 0-33 MHz PCI clock. Drives the PCI clock domain in the PCI interface.     |

| SPW_CLK  | 10-200 MHz SpaceWire clock. Provides a clock to all four SpaceWire links. |

| ETX_CLK  | Ethernet transmitter clock, 2.5 or 25 MHz generated by external PHY.      |

| ERX_CLK  | Ethernet receiver clock. 2.5 or 25 MHz generated by external PHY.         |

| 1553_CLK | MIL-STD-1553B BC, RT, BM 20 MHz clock.                                    |

## 1.7.2 Clock Output

Table 1.7 shows the clock inputs to the UT699E/UT700:

#### Table 1.7: Clock Output

| SIGNAL | DESCRIPTION                                                          |  |  |  |  |

|--------|----------------------------------------------------------------------|--|--|--|--|

|        | Main clock that drives the SDRAM device.                             |  |  |  |  |

|        | NOTE: If the AMBA frequency ("NODIV") is half the CPU frequency, the |  |  |  |  |

| SDCLK  | SDCLK is constant low during reset.                                  |  |  |  |  |

|        | If the AMBA frequency ("NODIV") is equal the CPU frequency, the      |  |  |  |  |

|        | SDCLK is toggling during reset.                                      |  |  |  |  |

## Chapter 2: LEON 3FT SPARC V8 32-bit Microprocessor

## 2.1 Overview

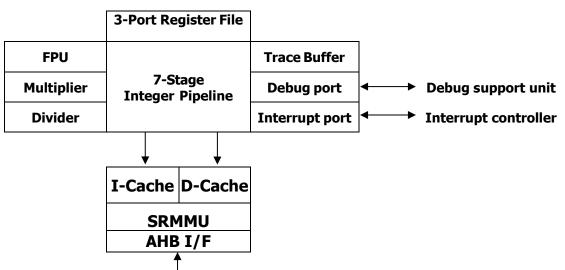

The LEON 3FT is a 32-bit processor core conforming to the IEEE-1754 (SPARC V8) architecture. It is designed for embedded applications while combining high performance with low complexity and low power consumption. The processor core storage elements and on-chip memory are hardened against SEU errors utilizing various fault-tolerance techniques.

The LEON 3FT has the following main features: 7-stage pipeline with Harvard architecture, separate instruction and data caches, memory management unit, hardware multiplier and divider, on-chip debug support and a floating-point unit.

A block diagram of the LEON 3FT core follows:

Figure 2.1: LEON 3FT Microprocessor Core Block Diagram

## 2.1.1 Integer Unit

The LEON 3FT integer unit supports the full SPARC V8 instruction set, including hardware multiplication and division instructions. The integer unit has eight register windows consisting of a total of one hundred and thirty-six (136) 32-bit general-purpose registers (*r* registers). These registers conform to the SPARC model for the general-purpose operand registers accessible through instructions, and implemented with RAM blocks. The instruction pipeline uses a Harvard architecture consisting of seven stages interfaced to a separate instruction and data cache.

#### 2.1.2 Cache Sub-System

The processor is configured with 16 Kbyte instruction and 16 Kbyte data caches. The instruction cache is configured as four-way set-associative with 4 Kbyte per way and 32 bytes per line, while the data cache has four ways of 4 Kbyte with 16 bytes per line. Sub-blocking is implemented with one valid bit per 32-bit word for the instruction cache and one valid bit per line for data cache. The instruction cache uses streaming during line-refill to minimize refill latency. The data cache uses write-through policy and implements a double-word write-buffer. The data cache can perform bussnooping on the AHB bus, if enabled. Bus-snooping on the AHB bus is used to maintain cache coherency for the data cache.

## 2.1.3 Floating-Point Unit

The LEON 3FT processor is configured with the Cobham's Gaisler floating-point unit (GRFPU). The GRFPU executes in parallel with the integer unit and does not block the processor operation unless a data or resource dependency exists.

#### 2.1.4 Memory Management Unit

The LEON 3FT processor is configured with the SPARC V8 Reference Memory Management Unit (SRMMU). The SPARC V8 compliant SRMMU provides mapping between multiple 32-bit virtual address spaces and physical memory. A three-level hardware table-walk is implemented and the MMU has 16 Translation Look-Aside Buffer (TLB) entries for instructions and 16 TLB entries for data.

## 2.1.5 On-Chip Debug Support

The LEON 3FT pipeline provides support for non-intrusive debugging. Full access to all processor registers and cache memory are provided through the debug support unit (DSU). To aid software debugging, two hardware watchpoint registers are implemented. Each register can cause a breakpoint trap on an arbitrary instruction or data address range. When the DSU is enabled, the watchpoints can be used to enter debug mode. The DSU also allows single stepping, instruction tracing and hardware breakpoint/watchpoint control. An internal trace buffer monitors and stores executed instructions which can later be read out over the debug interface.

#### 2.1.6 Interrupt Port

LEON 3FT supports the SPARC V8 interrupt model with a total of 15 asynchronous interrupts. The interrupts to the interrupt port are triggered through the Interrupt Controller.

#### 2.1.7 AMBA Interface

The cache system implements an AMBA AHB master to load and store data to/from the caches. The interface is compliant with the AMBA-2.0 standard. During line refill, incremental bursts are generated to optimize the data transfer.

#### 2.1.8 Power-Down Mode

The LEON 3FT processor core implements a power-down mode which halts the pipeline and caches until the next interrupt. This is an efficient way to minimize power-consumption when the application is idle. The processor supports clock gating during the power down period that provides the means to check for wake-up conditions and maintain cache coherency.

#### 2.2 LEON 3FT Integer Unit

#### 2.2.1 Overview

The LEON 3FT integer unit implements the integer part of the SPARC V8 instruction set. The implementation is focused on high performance and low complexity. The LEON 3FT integer unit has the following main features:

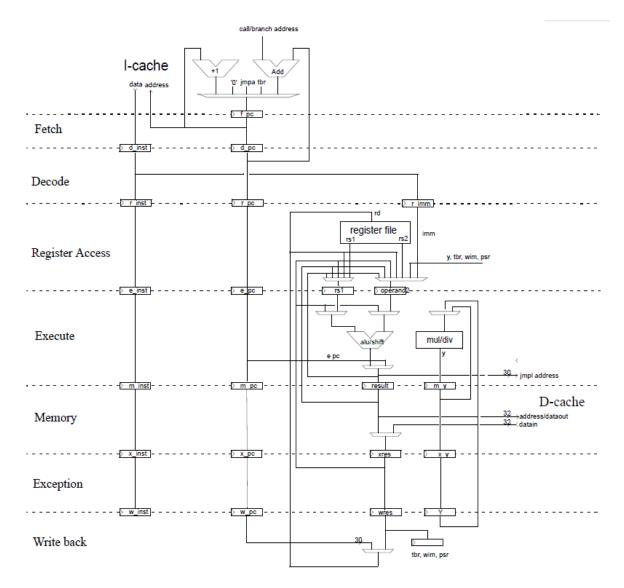

- 7-stage instruction pipeline

- Separate instruction and data cache interfaces

- Eight register windows to access the 136 registers

- Hardware multiplier with 2 clocks latency