# Functional Manual UT699 LEON 3FT /SPARC<sup>TM</sup> V8 Microprocessor

# **Table of Contents**

| Table of Co | ntents1                                   |

|-------------|-------------------------------------------|

| Chapter 1:  | Introduction9                             |

| 1.1 S       | cope9                                     |

| 1.2 A       | rchitecture9                              |

| 1.3 M       | 1emory Map10                              |

| 1.4 I       | nterrupts                                 |

|             | ignals12                                  |

| 1.6 C       | locking14                                 |

| 1.6.1       | Clock Inputs                              |

| 1.6.2       | Clock Output14                            |

| 1.6.3       | Clock Gating                              |

| 1.7 R       | eset Operation15                          |

| Chapter 2:  | LEON 3FT SPARC V8 32-bit Microprocessor16 |

| 2.1 C       | Overview16                                |

| 2.1.1       | Integer Unit                              |

| 2.1.2       | Cache Sub-System16                        |

| 2.1.3       | Floating-Point Unit                       |

| 2.1.4       | Memory Management Unit17                  |

| 2.1.5       | On-Chip Debug Support17                   |

| 2.1.6       | Interrupts                                |

| 2.1.7       | AMBA Interface                            |

| 2.1.8       | Power-down Mode17                         |

| 2.2 L       | EON 3FT Integer Unit                      |

| 2.2.1       | Overview17                                |

| 2.2.2       | Instruction Pipeline                      |

| 2.2.3       | SPARC Implementer's ID                    |

| 2.2.4       | Division Instructions                     |

| 2.2.5       | Multiplication Instructions               |

| 2.2.6       | Hardware Breakpoints                      |

| 2.2.7       | Instruction Trace Buffer21                |

| 2.2.8       | Processor Configuration Register21        |

| 2.2.9       | Exceptions                                |

| 2.2.10      | Single Vector Interrupt (SVT)             |

| 2.2.1       | Address Space Identifiers (ASI)           |

| 2.2.12      | 2 Power-Down                              |

| 2.2       | .13   | Processor Reset Operation               |

|-----------|-------|-----------------------------------------|

| 2.2       | .14   | Integer Unit SEU Protection             |

| 2.2       | .15   | Data Scrubbing                          |

| 2.3       | Floa  | ting Point Unit                         |

| 2.4       | Cach  | ne Sub-System                           |

| 2.4       | .1    | Overview                                |

| 2.4       | .2    | Instruction Cache                       |

| 2.4       | .3    | Data Cache                              |

| 2.4       | .4    | Write Buffer                            |

| 2.4       | .5    | Instruction and Data Cache Tags         |

| 2.4       | .6    | Cache Flushing                          |

| 2.4       | .7    | Diagnostic Cache Access                 |

| 2.4       | .8    | Cache Control Register                  |

| 2.4       | .9    | Error Protection                        |

| 2.4       | .10   | Cache Configuration Registers           |

| 2.4       | .11   | Software Consideration                  |

| 2.5       | Men   | nory Management Unit                    |

| 2.5       | .1    | MMU ASI Usage                           |

| 2.5       | .2    | Cache Operation                         |

| 2.5       | .3    | MMU Registers                           |

| 2.5       | .4    | Translation Look-Aside Buffer (TLB)     |

| 2.6       | RAM   | I Usage                                 |

| 2.6       | .1    | Integer Unit Register File              |

| 2.6       | .2    | Floating Point Unit (FPU) Register File |

| 2.6       | .3    | Cache Memories                          |

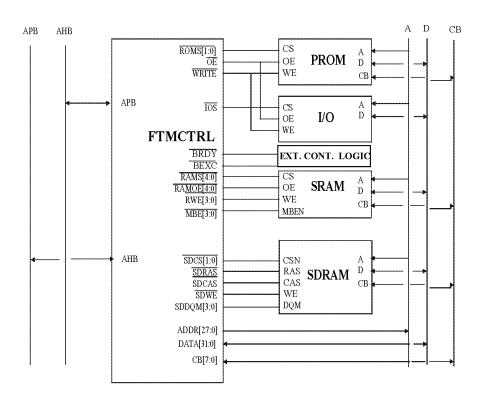

| Chapter 3 | 3:    | Memory Controller with EDAC             |

| 3.1       | Ove   | rview                                   |

| 3.2       | Men   | nory Mapped I/O                         |

| 3.3       | SRA   | M Access                                |

| 3.4       | 8-bit | and 16-bit PROM and SRAM Access         |

| 3.5       | 8-bit | t and 16-bit I/O Accesses41             |

| 3.6       | Burs  | t Cycles41                              |

| 3.7       | SDR   | AM Access41                             |

| 3.8       | .1    | General41                               |

| 3.8       | .2    | Address Mapping                         |

| 3.8       | .3    | Initialization                          |

| 3.8       | .4    | Configurable SDRAM Timing Parameters42  |

| 3.9       | Refr  | esh42                                   |

| 3.9.      | 1    | SDRAM Commands43                                 |

|-----------|------|--------------------------------------------------|

| 3.9.      | 2    | Read Cycles43                                    |

| 3.9.      | 3    | Write Cycles43                                   |

| 3.9.      | 4    | Address Bus43                                    |

| 3.9.      | 5    | Data Bus43                                       |

| 3.9.      | 6    | Clocking43                                       |

| 3.9.      | 7    | Initialization                                   |

| 3.10      | Mem  | 13 nory EDAC                                     |

| 3.11      | Usin | g BRDY44                                         |

| 3.12      | Acce | ess Errors                                       |

| 3.13      | Atta | ching an External DRAM Controller45              |

| 3.14      | Regi | sters45                                          |

| 3.14      | 4.1  | Memory Configuration Register 1 (MCFG1)45        |

| 3.14      | 4.2  | Memory Configuration Register 2 (MCFG2)          |

| 3.14      | 4.3  | Memory Configuration Register 3 (MCFG3)          |

| 3.15      | Vend | dor and Device Identifiers                       |

| 3.16      | Boot | Strap Configuration                              |

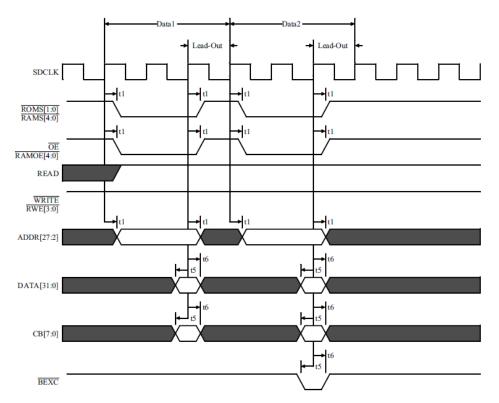

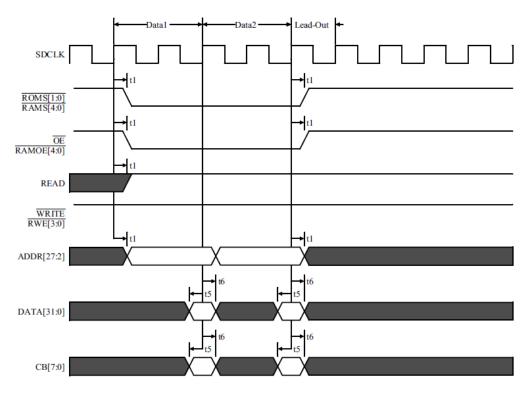

| 3.17      | PRO  | M, SRAM, and Memory Mapped I/O Timing Diagrams51 |

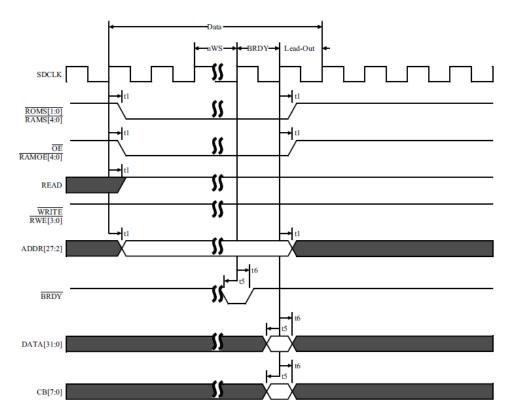

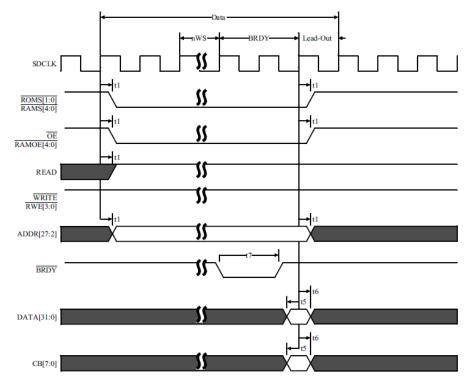

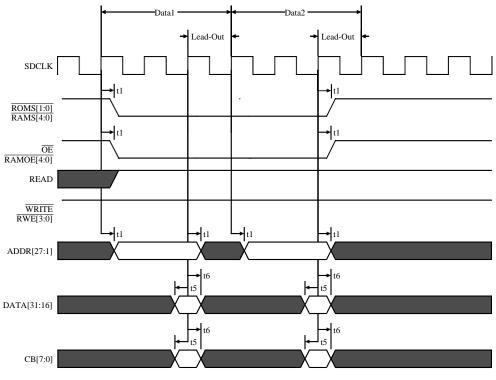

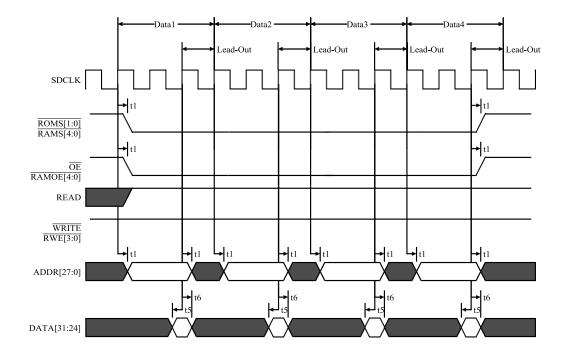

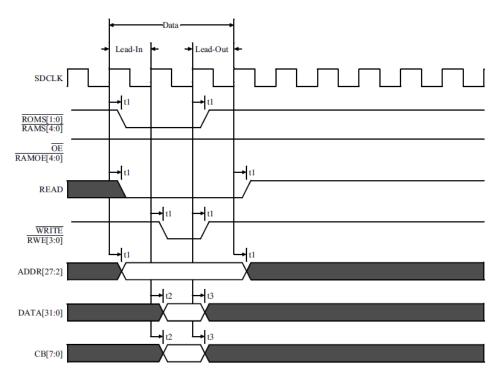

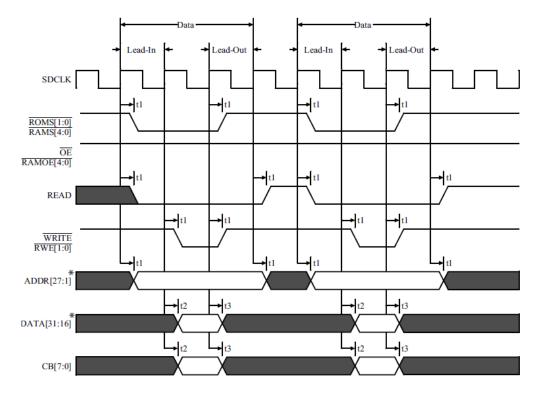

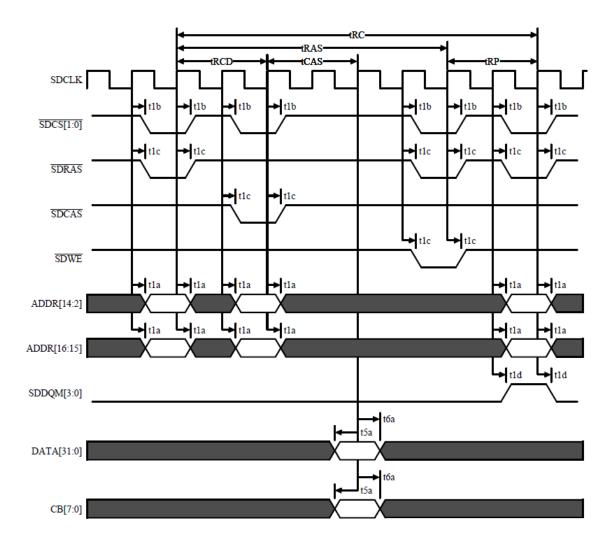

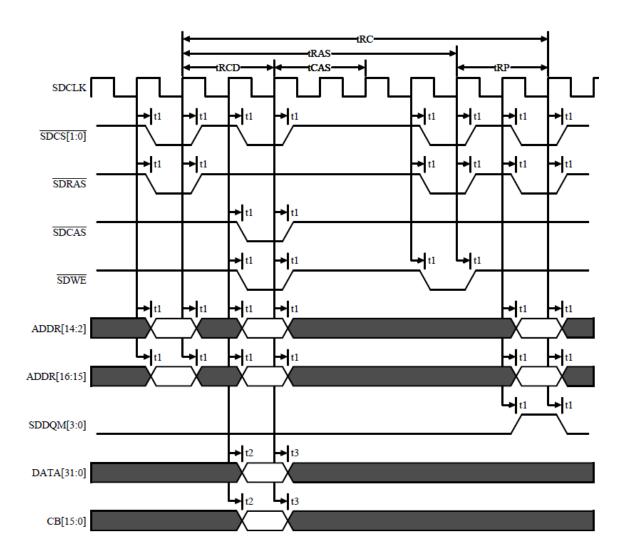

| 3.18      | SDR  | AM Timing Diagram57                              |

| Chapter 4 | 4:   | AHB Status Registers                             |

| 4.1       | Over | view60                                           |

| 4.2       | Ope  | ration60                                         |

| 4.3       | Regi | sters60                                          |

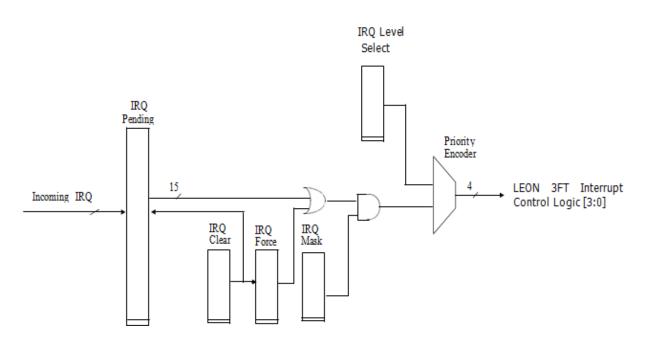

| Chapter ! | 5:   | Interrupt Controller                             |

| 5.1       | Over | view62                                           |

| 5.2       | Ope  | ration62                                         |

| 5.2.      | 1    | Interrupt Prioritization                         |

| 5.2.      | 2    | Interrupt Allocation                             |

| 5.3       | Regi | sters63                                          |

| 5.3.      | 1    | Interrupt Level Register                         |

| 5.3.      | 2    | Interrupt Pending Register                       |

| 5.3.      | 3    | Interrupt Force Register                         |

| 5.3.      | 4    | Interrupt Clear Register                         |

| 5.3.      | 5    | Interrupt Status Register                        |

| 5.3.      | 6    | Interrupt Mask Register                          |

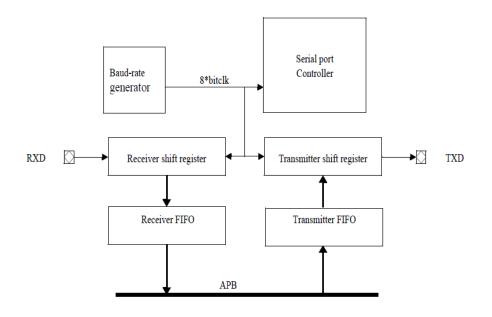

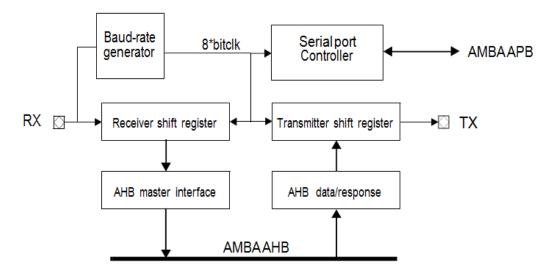

| Chapter 6 | 5:   | UART with APB Interface                          |

|           |      |                                                  |

| 6.1       | Over | view68                                           |

| 6.2     | .1  | Transmitter Operation                       | 68 |

|---------|-----|---------------------------------------------|----|

| 6.2     | .2  | Receiver Operation                          | 69 |

| 6.3     | Bau | d Rate Generation                           | 69 |

| 6.3     | .1  | Loop Back Mode                              | 70 |

| 6.3     | .2  | Interrupt Generation                        | 70 |

| 6.4     | UAR | T Registers                                 | 70 |

| 6.4     | .1  | UART Data Register                          | 70 |

| 6.4     | .2  | UART Status Register                        | 71 |

| 6.4     | .3  | UART Control Register                       | 72 |

| 6.4     | .4  | UART Scaler Register                        | 73 |

| Chapter | 7:  | Timer Unit                                  | 74 |

| 7.1     | Ove | rview                                       | 74 |

| 7.2     | Ope | ration                                      | 74 |

| 7.3     | Reg | isters                                      | 75 |

| Chapter | 8:  | General Purpose I/O Port                    | 79 |

| 8.1     | Ove | rview                                       | 79 |

| 8.2     | Ope | ration                                      | 79 |

| 8.3     | Reg | isters                                      | 79 |

| 8.3     | .1  | GPIO Port Input Value Register              | 80 |

| 8.3     | .2  | GPIO Port Data Output Register              | 80 |

| 8.3     | .3  | GPIO Port Data Direction Register           | 81 |

| 8.3     | .4  | GPIO Interrupt Mask Register                | 81 |

| 8.3     | .5  | GPIO Interrupt Priority Register            | 82 |

| 8.3     | .6  | GPIO Interrupt Edge Register                | 83 |

| Chapter | 9:  | PCI Master/Target Unit                      | 84 |

| 9.1     | Ove | rview                                       | 84 |

| 9.2     | Ope | ration                                      | 84 |

| 9.2     | .1  | PCI Target Unit                             | 84 |

| 9.2     | .2  | PCI Master Unit                             | 84 |

| 9.2     | .3  | Burst Transactions                          | 85 |

| 9.2     | .4  | Byte Twisting                               | 85 |

| 9.3     | PCI | Target Interface                            | 85 |

| 9.4     | PCI | Target Configuration Space Header Registers | 86 |

| 9.5     | PCI | Target Map Registers                        | 91 |

| 9.5     | .1  | PAGE0 Register                              | 91 |

| 9.5     | .2  | PAGE1 Register                              | 92 |

| 9.6     | PCI | Master Interface                            | 93 |

| 9.6     | .1  | PCI Configuration Cycles                    | 93 |

| 9.6     | .2  | PCI I/O Cycles                              | 94 |

| 9.6     | .3    | PCI Memory Cycles                               | 94  |

|---------|-------|-------------------------------------------------|-----|

| 9.7     | PCI   | Host Operation                                  | 95  |

| 9.8     | Inte  | errupt Support                                  | 95  |

| 9.9     | Regi  | listers                                         | 95  |

| 9.10    | Ven   | dor and Device Identifiers                      |     |

| Chapter | 10:   | DMA Controller for the GRPCI Interface          |     |

| 10.1    | Intro | oduction                                        |     |

| 10.2    | Ope   | eration                                         |     |

| 10.3    | Regi  | listers                                         |     |

| 10.4    | Ven   | dor and Device Identifiers                      |     |

| Chapter | 11:   | SpaceWire Interface                             |     |

| 11.1    | Ove   | erview                                          |     |

| 11.2    | Ope   | eration                                         |     |

| 11.     | 2.1   | Overview                                        | 107 |

| 11.     | 2.2   | Protocol Support                                |     |

| 11.3    | Link  | < Interface                                     |     |

| 11.     | 3.1   | Link Interface FSM                              |     |

| 11.     | 3.2   | Transmitter                                     |     |

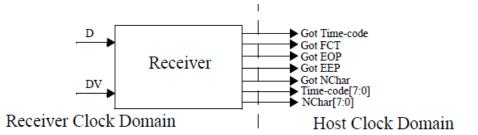

| 11.     | 3.3   | Receiver                                        |     |

| 11.     | 3.4   | Time Interface                                  |     |

| 11.     | 3.5   | Clock Divider                                   | 110 |

| 11.4    | Rece  | eiver DMA Channels                              |     |

| 11.4    | 4.1   | Basic Functionality                             |     |

| 11.4    | 4.2   | Setting up the GRSPW for reception              |     |

| 11.4    | 4.3   | Setting up the Descriptor Table Address         |     |

| 11.4    | 4.4   | Enable Descriptors                              |     |

| 11.4    | 4.5   | Setting up the DMA Control Register             |     |

| 11.4    | 4.6   | The Effect to the Control Bits during Reception |     |

| 11.4    | 4.7   | Address Recognition and Packet Handling         |     |

| 11.4    | 4.8   | Status Bits                                     |     |

| 11.4    | 4.9   | Error Handling                                  |     |

| 11.4    | 4.10  | Open Packet Mode                                | 115 |

| 11.5    | Trar  | nsmitter DMA Engine                             |     |

| 11.     | 5.1   | Basic Functionality                             | 115 |

| 11.     | 5.2   | Setting up the GRSPW2 for Transmission          |     |

| 11.     | 5.3   | Enable Descriptors                              | 115 |

| 11.     | 5.4   | Starting Transmission                           |     |

| 11.     | 5.5   | The Transmission Process                        | 119 |

| 11.5.6      | The Descriptor Register                                   | 119 |

|-------------|-----------------------------------------------------------|-----|

| 11.5.7      | ' Error Handling                                          | 119 |

| 11.6 Re     | emote Memory Access Protocol (RMAP)                       | 119 |

| 11.6.1      | Fundamentals of the Protocol                              | 119 |

| 11.6.2      | 2 Implementation                                          | 120 |

| 11.6.3      | 8 Write Commands                                          | 122 |

| 11.6.4      | Read Commands                                             | 122 |

| 11.6.5      | Read-Modify-Write Commands                                | 122 |

| 11.6.6      | o Controls                                                | 122 |

| 11.7 AN     | MBA Interface                                             | 125 |

| 11.7.1      | APB Slave Interface                                       | 125 |

| 11.7.2      | AHB Master Interface                                      | 125 |

| 11.8 Re     | egisters                                                  | 126 |

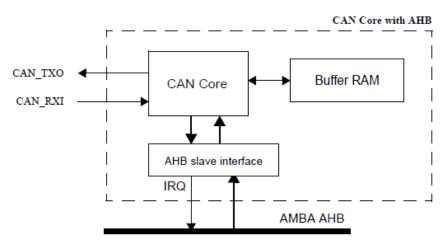

| Chapter 12: | CAN 2.0 Interface                                         | 138 |

| 12.1 Ov     | verview                                                   | 138 |

| 12.2 AH     | HB Interface                                              | 138 |

| 12.3 Ba     | asicCAN Mode                                              | 139 |

| 12.3.1      | BasicCAN Register Map (Address 0xFFF20000 and 0xFFF20100) | 139 |

| 12.3.2      | 2 Control Register                                        | 140 |

| 12.3.3      | Command Register                                          | 140 |

| 12.3.4      | Status Register                                           | 140 |

| 12.3.5      | 5 Interrupt Register                                      | 141 |

| 12.3.6      | Transmit Buffer                                           | 142 |

| 12.3.7      | ' Receive Buffer                                          | 142 |

| 12.3.8      | Acceptance Filter                                         | 142 |

| 12.4 Pe     | eliCAN Mode                                               | 142 |

| 12.4.1      | PeliCAN Register Map (Address 0xFFF20000 and 0xFFF20100)  | 142 |

| 12.4.2      | 2 Mode Register                                           | 144 |

| 12.4.3      | Command Register                                          | 144 |

| 12.4.4      | Status Register                                           | 145 |

| 12.4.5      | interrupt Register                                        | 145 |

| 12.4.6      | 5 Interrupt Enable Register                               | 146 |

| 12.4.7      | ' Arbitration Lost Capture Register                       | 146 |

| 12.4.8      | B Error Code Capture Register                             | 147 |

| 12.4.9      | Error Warning Limit Register                              | 148 |

| 12.4.1      | 0 RX Error Counter Register, Offset 14                    | 148 |

| 12.4.1      | 1 TX Error Counter Register, Offset 15                    | 148 |

| 12.4.12     | 2 Transmit Buffer                                         | 148 |

| 12.4.1      | 3 Receiver Buffer                                         | 150 |

| 12.4      | .14   | Acceptance Filter                                        | 152 |

|-----------|-------|----------------------------------------------------------|-----|

| 12.4      | .15   | RX Message Counter                                       | 154 |

| 12.5      | Com   | nmon Registers                                           | 154 |

| 12.5      | .1    | Clock Divider Register                                   | 154 |

| 12.5      | .2    | Bus Timing 0                                             | 154 |

| 12.5      | .3    | Bus Timing 1                                             | 155 |

| 12.6      | CAN   | I-OC vs SJA1000                                          | 155 |

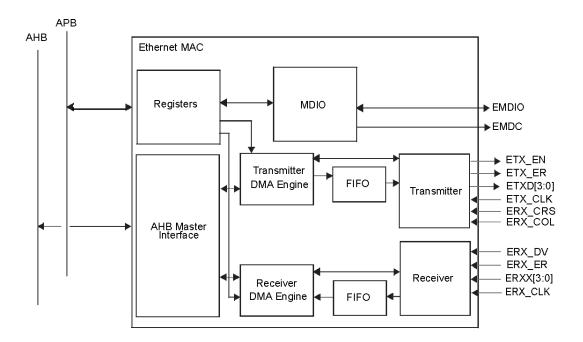

| Chapter 1 | 3:    | Ethernet Media Access Controller (MAC) with EDCL Support | 157 |

| 13.1      | Over  | rview                                                    | 157 |

| 13.2      | Ope   | ration                                                   | 157 |

| 13.2      | .1    | System Overview                                          | 157 |

| 13.2      | .2    | Protocol Support                                         | 158 |

| 13.2      | .3    | Hardware Requirements                                    | 158 |

| 13.2      | .4    | Transmitter DMA Interface                                | 158 |

| 13.2      | .5    | Setting up a Descriptor                                  | 158 |

| 13.2      | .6    | Starting Transmissions                                   | 160 |

| 13.2      | .7    | Descriptor Handling After Transmission                   | 160 |

| 13.2      | .8    | Setting up the Data for Transmission                     | 160 |

| 13.2      | .9    | Receiver DMA Interface                                   | 161 |

| 13.2      | .10   | Setting up Descriptors                                   | 161 |

| 13.2      | .11   | Starting Reception                                       | 162 |

| 13.2      | .12   | Descriptor Handling After Reception                      | 163 |

| 13.2      | .13   | Reception with AHB Errors                                | 163 |

| 13.2      | .14   | MDIO Interface                                           | 163 |

| 13.2      | .15   | Media Independent Interfaces                             | 163 |

| 13.2      | .16   | Software Drivers                                         | 164 |

| 13.3      | Regi  | isters                                                   | 164 |

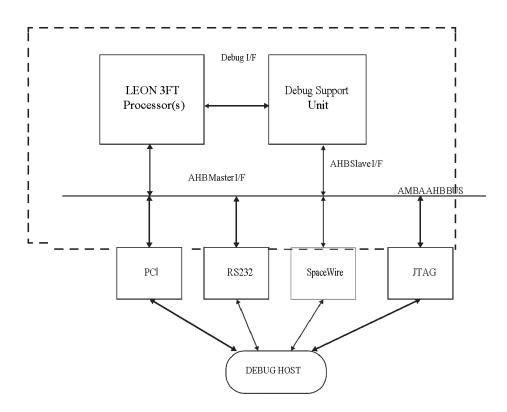

| Chapter 1 | 4:    | Hardware Debug Support                                   | 170 |

| 14.1      | Over  | rview                                                    | 170 |

| 14.2      | Ope   | ration                                                   | 170 |

| 14.3      | AHB   | 3 Trace Buffer                                           | 171 |

| 14.4      | Instr | ruction Trace Buffer                                     | 172 |

| 14.5      | DSU   | J Memory Map                                             | 172 |

| 14.6      | DSU   | J Registers                                              |     |

| 14.6      | .1    | DSU Control Register                                     | 174 |

| 14.6      | .2    | DSU Break and Single-Step Register                       | 175 |

| 14.6      | .3    | DSU Trap Register                                        | 176 |

| 14.6      | .4    | DSU Trace Buffer Time Tag Counter Register               | 176 |

| 14.      | 6.5    | DSU ASI Diagnostic Access Register 177    |

|----------|--------|-------------------------------------------|

| 14.      | 6.6    | AHB Trace Buffer Control Register 177     |

| 14.      | 6.7    | AHB Trace Buffer Index Register           |

| 14.      | 6.8    | AHB Trace Buffer Breakpoint Registers 179 |

| 14.      | 6.9    | Instruction Trace Control Registers       |

| Chapter  | 15:    | Serial Debug Link                         |

| 15.1     | Ove    | rview                                     |

| 15.2     | Ope    | ration                                    |

| 15.      | 2.1    | Transmission Protocol                     |

| 15.      | 2.2    | Baud Rate Generator                       |

| 15.3     | Reg    | isters                                    |

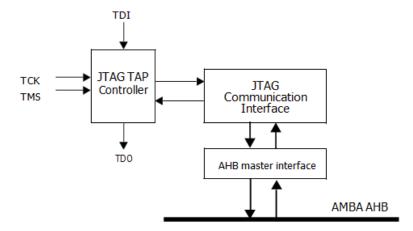

| Chapter  | 16:    | JTAG Debug Link                           |

| 16.1     | Ove    | rview                                     |

| 16.2     | Ope    | ration                                    |

| 16.      | 2.1    | Transmission Protocol                     |

| 16.3     | Reg    | ister                                     |

| 16.4     | Ven    | dor and Devices Identifiers               |

| Chapter  | 17:    | CLKGATE Clock Gating Unit                 |

| 17.1     | Ove    | rview                                     |

| 17.2     | Ope    | eration                                   |

| 17.3     | Reg    | isters                                    |

| Appendix | ( A: R | Register Format                           |

# Chapter 1: Introduction

# 1.1 Scope

This document describes the UT699 LEON 3FT microprocessor. The UT699 is a pipelined, monolithic, high-performance, fault-tolerant SPARCTM V8 Processor. It has been designed for reliable operation in HiRel environments; the architecture includes functionality to detect and correct (SEU) errors in all on-chip RAM memories.

The UT699 provides a 32-bit/33MHz PCI (Revision 2.1 compatible) master/target interface with DMA and host capabilities, including a 16-bit user I/O interface for off-chip peripherals. An AMBA (Rev. 2.0) bus interface integrates the on-chip LEON 3FT core, SpaceWire, Ethernet, memory controller, PCI, CAN bus, and programmable interrupt peripherals.

The UT699 is SPARC V8 compliant. Therefore, industry standard compilers and kernels for the SPARC V8 can be used for software development. A full software development suite, including a C/C++ cross-compiler system based on the Gnu C Compiler (GCC) and the Newlib embedded C-library is available from Cobham Gaisler. The Bare C Compiler (BCC), based upon GCC, includes a small run-time kernel with interrupt support and Pthreads library.

The development suite runs on either Windows or Linux operating systems. For multi-threaded applications, a SPARC compliant port of the eCos real-time kernel, RTEMS 4.6.5 and VxWorks 6.x is supported.

The UT699 LEON 3FT microprocessor is based on IP cores from Cobham Gaisler AB's GRLIB Intellectual Property (IP) library and uses a plug-and-play configuration.

## **1.2 Architecture**

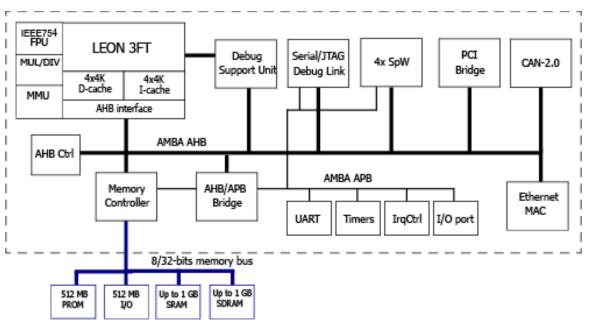

The UT699 consists of one LEON 3FT processor core, an 8/32-bit memory controller, a PCI controller, four SpaceWire links, two CAN-2.0 interfaces, one UART, four timers, one interrupt controller, a 16-bit I/O port, a serial/JTAG debug link and a 10/100 Ethernet MAC. The block diagram follows.

Figure 1.1: UT699 Functional Block Diagram

The design is based on the following IP cores from the GRLIB IP library:

| CORE     | FUNCTION                             | VENDOR ID | DEVICE ID | VER |

|----------|--------------------------------------|-----------|-----------|-----|

| LEON 3FT | SPARC V8 32-bit processor            | 0x01      | 0x053     | 0x0 |

| DSU3     | Debug support unit                   | 0x01      | 0x004     | 0x1 |

| IRQMP    | Interrupt controller                 | 0x01      | 0x00D     | 0x3 |

| APBCTRL  | AHB/APB bridge                       | 0x01      | 0x006     | 0x0 |

| FTMCTRL  | 8/32-bit memory controller with EDAC | 0x01      | 0x054     | 0x1 |

| AHBSTAT  | AHB status register                  | 0x01      | 0x052     | 0x0 |

| AHBUART  | Serial/AHB debug interface           | 0x01      | 0x007     | 0x0 |

| AHBJTAG  | JTAG/AHB debug interface             | 0x01      | 0x01C     | 0x1 |

| GRSPW    | SpaceWire link with DMA              | 0x01      | 0x01F     | 0x0 |

| GRPCI    | 32-bit PCI bridge                    | 0x01      | 0x014     | 0x0 |

| PCIDMA   | DMA controller for PCI bridge        | 0x01      | 0x016     | 0x0 |

| CAN_OC   | Dual CAN-2.0 interface               | 0x01      | 0x019     | 0x1 |

| GRETH    | 10/100 Ethernet MAC                  | 0x01      | 0x01D     | 0x0 |

| APBUART  | 8-bit UART with FIFO                 | 0x01      | 0x00C     | 0x1 |

| GPTIMER  | Modular timer unit                   | 0x01      | 0x011     | 0x0 |

| GPIO     | General purpose I/O port             | 0x01      | 0x01A     | 0x1 |

| CLKGATE  | Clock gating module                  | 0x01      | 0x02C     | 0x0 |

| PCIARB   | PCI arbiter                          | 0x04      | 0x10      | 0x0 |

| LEON 3FT | SPARC V8 32-bit processor            | 0x01      | 0x053     | 0x0 |

#### Table 1.1: GLIB IP Cores used in UT699

# **1.3 Memory Map**

**Table 1.2** is a memory map of the internal AHB/APB buses:

|          | , , ,                                      |     |      |

|----------|--------------------------------------------|-----|------|

| CORE     | ADDRESS RANGE                              | BUS | Link |

| FTMCTRL  | 0x0000_0000 - 0x1FFF_FFFF : PROM area      | AHB |      |

|          | 0x2000_0000 - 0x3FFF_FFFF: I/O area        |     |      |

|          | 0x4000_0000 - 0x7FFF_FFFF: SRAM/SDRAM area |     |      |

| APBCTRL  | 0x8000_0000 - 0x800F_FFFF: APB bridge      | AHB |      |

| Reserved | 0x8100_0000 - 0x8FFF_FFFF: Unused          | APB |      |

| DSU3     | 0x9000_0000 - 0x9FFF_FFFF: Registers       | APB |      |

| Reserved | 0xA000_0000 - 0xBFFF_FFFF: Unused          | APB |      |

| PCI      | 0xC000_0000 - 0xFFEF_FFFF: PCI Bus         | APB |      |

|          | 0xFFF0_0000 - 0xFFF1_FFFF: PCI I/O space   |     |      |

| CANOC1   | 0xFFF2_0000 - 0xFFF2_00FF: Registers       | APB |      |

| CANOC2   | 0xFFF2_0100 - 0xFFF2_01FF: Registers       | APB |      |

#### Table 1.2: Internal Memory Map

| CORE                  | ADDRESS RANGE                                             | BUS | Link |

|-----------------------|-----------------------------------------------------------|-----|------|

| Reserved              | 0xFFF2_2000 - 0xFFFF_EFFF: Unused                         | AHB |      |

| AHB plug-<br>and-play | 0xFFF_FF000 - 0xFFFF_FFFF: Plug-and-play<br>configuration | AHB |      |

| FTMCTRL               | 0x8000_0000 - 0x8000_00FF: Registers                      | AHB |      |

| APBUART               | 0x8000_0100 - 0x8000_01FF: Registers                      | AHB |      |

| IRQMP                 | 0x8000_0200 - 0x8000_02FF: Registers                      | APB |      |

| GPTIMER               | 0x8000_0300 - 0x8000_03FF: Registers                      | AHB |      |

| PCI                   | 0x8000_0400 - 0x800_004FF: PCI DMA control<br>registers   | AHB |      |

| PCI DMA<br>CTRL       | 0x8000_0500 - 0x8000_05FF: Registers                      | AHB |      |

| CLKGATE               | 0x8000_0600 - 0x8000_06FF: Registers                      | AHB |      |

| AHBUART               | 0x8000_0700 - 0x8000_07FF: Registers                      | AHB |      |

| PCIARB                | 0x8000_0800 - 0x8000_08FF: Registers                      | APB |      |

| GPIO                  | 0x8000_0900 - 0x8000_09AA: Registers                      | APB |      |

| SPW1                  | 0x8000_0A00 - 0x8000_0AFF: Registers                      | APB |      |

| SPW2                  | 0x8000_0B00 - 0x8000_0BFF: Registers                      | APB |      |

| SPW3                  | 0x8000_0C00 - 0x8000_0CFF: Registers                      | APB |      |

| SPW4                  | 0x8000_0D00 - 0x8000_0DFF: Registers                      | APB |      |

| ETH                   | 0x8000_0E00 - 0x8000_0EFF: Registers                      | APB |      |

| AHBSTAT               | 0x8000_0F00 - 0x8000_0FFF: Registers                      | APB |      |

| Reserved              | 0x8000_1000 - 0x800F_EFFF: Unused                         | APB |      |

| APB plug-<br>and-play | 0x800F_F000 - 0x800F_FFFF: Plug-and-play<br>configuration | APB |      |

| Reserved              | 0x8010_0000 - 0xFFFF_EFFF: Unused                         | APB |      |

Access to addresses outside the ranges described above will return an AHB error response. Only 32-bit (word) accesses are supported for APB areas.

# **1.4 Interrupts**

The interrupts are routed to the IRQMP interrupt controller and forwarded to the LEON 3FT processor. **Table 1.3** indicates the interrupt assignments:

| CORE    | INTERRUPT # | FUNCTION                   |

|---------|-------------|----------------------------|

| AHBSTAT | 1           | AHB bus error              |

| APBUART | 2           | UART RX/RX interrupt       |

| PCI     | 3           | PCI DMA interrupt          |

| CAN1    | 4           | CAN1                       |

| CAN2    | 5           | CAN2                       |

| GPTIMER | 6, 7, 8, 9  | Timer underflow interrupts |

#### Table 1.3: Interrupt Assignments

| CORE | INTERRUPT # | FUNCTION                           |

|------|-------------|------------------------------------|

| SPW1 | 10          | SpaceWire1 RX/TX data<br>interrupt |

| SPW2 | 11          | SpaceWire2 RX/TX data<br>interrupt |

| SPW3 | 12          | SpaceWire3 RX/TX data<br>interrupt |

| SPW4 | 13          | SpaceWire4 RX/TX data<br>interrupt |

| ETH  | 14          | Ethernet RX/TX interrupt           |

| GPIO | 1 - 15      | External I/O interrupt             |

# 1.5 Signals

The device has the following external signals, **Table 1.4**. The reset value for any signal is undefined if not otherwise indicated.

Table 1.4:Signal Assignments

| PIN NAME    | FUNCTION | RESET<br>VALUE | DESCRIPTION                                                                                              |

|-------------|----------|----------------|----------------------------------------------------------------------------------------------------------|

| SYSCLK      | I        |                | Main system clock                                                                                        |

| NODIV       | I*       |                | Clock divider input. Set to '1' for 1x<br>memory clock, '0' for 1/2x memory clock,<br>relative to SYSCLK |

| RESET       | IS       |                | System reset                                                                                             |

| ERROR1      | OD       |                | Processor error mode indicator. This is an active low output.                                            |

| WDOG1       | OD       |                | Watchdog indicator. This is an active low output.                                                        |

| ADDR[27:0]  | 0        | [000]          | Address bus                                                                                              |

| DATA[31:0]  | I/O      | High-z         | Data bus                                                                                                 |

| CB[7:0]     | I/O      | High-z         | EDAC checkbits                                                                                           |

| WRITE       | 0        | 1              | Write strobe for PROM and I/O                                                                            |

| OEN         | 0        | 1              | Output enables for PROM and I/O                                                                          |

| IOS         | 0        | 1              | I/O area chip select                                                                                     |

| ROMS[1:0]   | 0        | 1              | PROM chip select                                                                                         |

| RWEN[3:0]   | 0        | 1              | SRAM write enable strobe                                                                                 |

| RAMOEN[4:0] | 0        | 1              | SRAM output enable                                                                                       |

| RAMS[4:0]   | 0        | 1              | SRAM chip select                                                                                         |

| READ        | 0        | 1              | SRAM, PROM, and I/O read indicator                                                                       |

| BEXC        | I        |                | Bus exception                                                                                            |

| BRDY        | I        |                | Bus ready                                                                                                |

| SDCLK       | 0        | 1              | SDRAM clock                                                                                              |

| SDRAS       | 0        | 1              | SDRAM row address strobe                                                                                 |

| PIN NAME     | FUNCTION | RESET<br>VALUE | DESCRIPTION                                  |

|--------------|----------|----------------|----------------------------------------------|

| SDCAS        | 0        | 1              | SDRAM column address strobe                  |

| SDWEN        | 0        | 1              | SDRAM write enable                           |

| SDCS[1:0]    | 0        | 1              | SDRAM chip select                            |

| SDDQM[3:0]   | 0        | 1              | SDRAM data mask                              |

| CAN_RXD[1:0] | I        |                | CAN receive data                             |

| CAN_TXD[1:0] | 0        | 1              | CAN transmit data                            |

| DSUACT       | 0        | 0              | DSU mode indicator                           |

| DSUBRE       | Ι        |                | DSU break                                    |

| DSUEN        | I        |                | DSU enable                                   |

| DSURX        | I        |                | DSU UART receive data                        |

| DSUTX        | 0        | 1              | DSU UART transmit data                       |

| TRST         | I        |                | JTAG reset                                   |

| TMS          | I        |                | JTAG test mode select                        |

| ТСК          | I        |                | JTAG clock                                   |

| TDI          | I        |                | JTAG test data input                         |

| TDO          | 0        |                | JTAG test data output                        |

| EMDC         | 0        | 0              | Ethernet media interface clock               |

| ERX_CLK      | I        |                | Ethernet RX clock                            |

| EMDIO        | I/O      | High-z         | Ethernet media interface data                |

| ERX_COL      | I        |                | Ethernet collision error                     |

| ERX_CRS      | Ι        |                | Ethernet carrier sense detect                |

| ERX_DV       | Ι        |                | Ethernet receiver data valid                 |

| ERX_ER       | Ι        |                | Ethernet reception error                     |

| ERXD[3:0]    | I        |                | Ethernet receive data                        |

| ETXD[3:0]    | 0        | [1010]         | Ethernet transmit data                       |

| ETX_CLK      | I        |                | Ethernet TX clock                            |

| ETX_EN       | 0        | 0              | Ethernet transmit enable                     |

| ETX_ER       | 0        | 0              | Ethernet transmit error                      |

| EMDINT**     | I        |                | Ethernet management interface data interrupt |

| EDCLDIS**    | I        |                | Ethernet debug link disable                  |

| GPIO[15:0]   | I/O      | High-z         | General Purpose I/O                          |

| SPW_CLK      | I        |                | SpaceWire clock                              |

| SPW_RXS[3:0] | I        |                | SpaceWire receive strobe                     |

| SPW_RXD[3:0] | I        |                | SpaceWire receive data                       |

| SPW_TXS[3:0] | 0        | 0              | SpaceWire transmit strobe                    |

| SPW_TXD[3:0] | 0        | 0              | SpaceWire transmit data                      |

| SPW_RXD[3:0] | I        |                | SpaceWire receive data                       |

| RXD          | I        |                | UART receive data                            |

| TXD          | 0        | 1              | UART transmit data                           |

| PCI_AD[31:0] | PCI-I/O  | High-z         | Bit 0 of PCI address and data bus            |

| PIN NAME         | FUNCTION | RESET<br>VALUE | DESCRIPTION                                              |

|------------------|----------|----------------|----------------------------------------------------------|

| PCI_RST          | PCI-I    |                | PCI reset input                                          |

| PCI_CLK          | PCI-I    |                | PCI clock input                                          |

| PCI_CBE[3:0]     | PCI-I/O  | High-z         | PCI bus command and byte enable                          |

| PCI_PAR          | PCI-I/O  | High-z         | PCI parity checkbit                                      |

| PCI_FRAME1       | PCI-3    | High-z         | PCI cycle frame indicator                                |

| PCI_IRDY1        | PCI-3    | High-z         | PCI initiator ready indicator                            |

| PCI_TRDY1        | PCI-3    | High-z         | PCI target ready indicator                               |

| PCI_STOP1        | PCI-3    | High-z         | PCI target stop request                                  |

| PCI_DEVSEL1      | PCI-3    | High-z         | PCI device select                                        |

| PCI_IDSEL        | PCI-I    |                | PCI initializer device select                            |

| PCI_REQ          | PCI-O    | High-z         | PCI request to arbiter in point-to-point configuration   |

| PCI_GNT          | PCI-I    |                | PCI bus access indicator in point-to-point configuration |

| PCI_HOST         | PCI-I    |                | PCI host enable input                                    |

| PCI_ARB_REQ[7:0] | PCI-I    |                | PCI arbiter bus request                                  |

| PCI_ARB_GNT[7:0] | PCI-O    | High-z         | PCI arbiter bus grant                                    |

| PCI_PERR1        | PCI-3    | High-z         | PCI parity error indicator                               |

#### Notes:

- 1. These pins require a pull-up resistor tied to VDD. Specified resistor values are based on design requirements or as specified in the PCI Local Bus Specification Revision 2.1, Section **4.3.3**.

- 2. CB[15:8] is reset to a high logic level.

# **1.6 Clocking**

#### 1.1.1 Clock Inputs

Table 1.5 shows the clock inputs to the UT699:

#### Table 1.5: Clock Inputs

| SIGNAL  | DESCRIPTION                                                               |

|---------|---------------------------------------------------------------------------|

| SYSCLK  | Main system clock. The processor and AHB bus is clocked directly by CLK.  |

| PCI_CLK | 0-33 MHz PCI clock. Drives the PCI clock domain in the PCI interface.     |

| SPW_CLK | 10-200 MHz SpaceWire clock. Provides a clock to all four SpaceWire links. |

| ETX_CLK | Ethernet transmitter clock, 2.5 or 25 MHz generated by external PHY.      |

| ERX_CLK | Ethernet receiver clock. 2.5 or 25 MHz generated by external PHY.         |

#### 1.1.2 Clock Output

Table 1.6 shows the clock inputs to the UT699:

#### Table 1.6: Clock Output

| SIGNAL | DESCRIPTION                                                                                                                                                                                                                                                   |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SDCLK  | Main clock that drives the SDRAM device.<br>NOTE: If the AMBA frequency ("NODIV") is half the CPU frequency, the<br>SDCLK is constant low during reset.<br>If the AMBA frequency ("NODIV") is equal the CPU frequency, the<br>SDCLK is toggling during reset. |  |  |

#### 1.1.3 Clock Gating

To save power, the AHB clock can be internally disabled from unused functional blocks. This is done through software by setting the appropriate bits in the clock gating unit. See Section 17.0 for more details.

# **1.7 Reset Operation**

When  $\overline{\text{RESET}}$  is asserted, the following signals are asynchronously driven to their inactive states: ROMS,  $\overline{\text{RAMS}}$ ,  $\overline{\text{IOS}}$ ,  $\overline{\text{OEN}}$   $\overline{\text{RAMOEN}}$ . In addition, DATA [31:0] and CB [7:0] are driven to a high-z state.

When the PCI reset input (PCI\_RST) is asserted, all PCI tri-state signals are asynchronously driven to their high-z state as required by the PCI specification.

# Chapter 2: LEON 3FT SPARC V8 32-bit Microprocessor

# **1.8 Overview**

The LEON 3FT is a 32-bit processor core conforming to the IEEE-1754 (SPARC V8) architecture. It is designed for embedded applications while combining high performance with low complexity and low power consumption. The processor core storage elements and on-chip memory are hardened against SEU errors utilizing various fault-tolerance techniques.

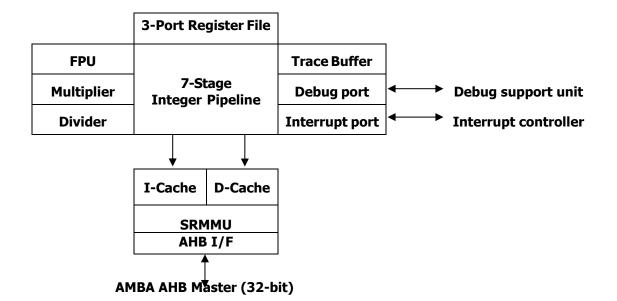

The LEON 3FT has the following main features: 7-stage pipeline with Harvard architecture, separate instruction and data caches, memory management unit, hardware multiplier and divider, on-chip debug support and a floating-point unit.

A block diagram of the LEON 3FT core follows:

Figure 2.1: LEON 3FT Microprocessor Core Block Diagram

#### 2.1.1 Integer Unit

The LEON 3FT integer unit supports the full SPARC V8 instruction set, including hardware multiplication and division instructions. The integer unit has eight register windows consisting of a total of one hundred and thirty-six (136) 32-bit general-purpose registers (*r* registers). These registers conform to the SPARC model for the general-purpose operand registers accessible through instructions, and implemented with RAM blocks. The instruction pipeline uses a Harvard architecture consisting of seven stages interfaced to a separate instruction and data cache.

#### 2.1.2 Cache Sub-System

The processor is configured with 8kB instruction and 8kB data caches, both configured as two-way set-associative with 4kB per way and 32 bytes per line for instruction cache and 16 bytes per line for data cache. Sub-blocking is implemented with one valid bit per 32-bit word. The instruction

cache uses streaming during line-refill to minimize refill latency. The data cache uses write-through policy and implements a double-word write buffer.

#### 2.1.3 Floating-Point Unit

The LEON 3FT processor is configured with the Cobham's Gaisler floating-point unit (GRFPU). The GRFPU executes in parallel with the integer unit and does not block the processor operation unless a data or resource dependency exists.

#### 2.1.4 Memory Management Unit

The LEON 3FT processor is configured with the SPARC V8 Reference Memory Management Unit (SRMMU). The SPARC V8 compliant SRMMU provides mapping between multiple 32bit virtual address spaces and physical memory. A three-level hardware table-walk is implemented and the MMU has 16 Translation Look-Aside Buffer (TLB) entries for instructions and 16 TLB entries for data.

#### 2.1.5 On-Chip Debug Support

The LEON 3FT pipeline provides support for non-intrusive debugging. Full access to all processor registers and cache memory are provided through the debug support unit (DSU). To aid software debugging, two hardware watchpoint registers are implemented. Each register can cause a breakpoint trap on an arbitrary instruction or data address range. When the DSU is enabled, the watchpoints can be used to enter debug mode. The DSU also allows single stepping, instruction tracing and hardware breakpoint/watchpoint control. An internal trace buffer monitors and stores executed instructions which can later be read out over the debug interface.

#### 2.1.6 Interrupts

LEON 3FT supports the SPARC V8 trap model with a total of 15 asynchronous interrupts. The interrupt interface provides functionality to both generate and acknowledge interrupts.

#### 2.1.7 AMBA Interface

The cache system implements an AMBA AHB master to load and store data to/from the caches. The interface is compliant with the AMBA-2.0 standard. During line refill, incremental bursts are generated to optimize the data transfer.

#### 2.1.8 Power-down Mode

The LEON 3FT processor core implements a power-down mode which halts the pipeline and caches until the next interrupt. This is an efficient way to minimize power-consumption when the application is idle. The processor supports clock gating during the power down period that provides the means to check for wake-up conditions and maintain cache coherency.

# 1.9 LEON 3FT Integer Unit

#### 2.1.9 Overview

The LEON 3FT integer unit implements the integer part of the SPARC V8 instruction set. The implementation is focused on high performance and low complexity. The LEON 3FT integer unit has the following main features:

- 7-stage instruction pipeline

- Separate instruction and data cache interfaces

- Eight register windows to access the 136 registers

- Hardware multiplier with 2 clocks latency

- Radix-2 divider (non-restoring)

- Single-vector trapping for reduced code size

- Static branch prediction

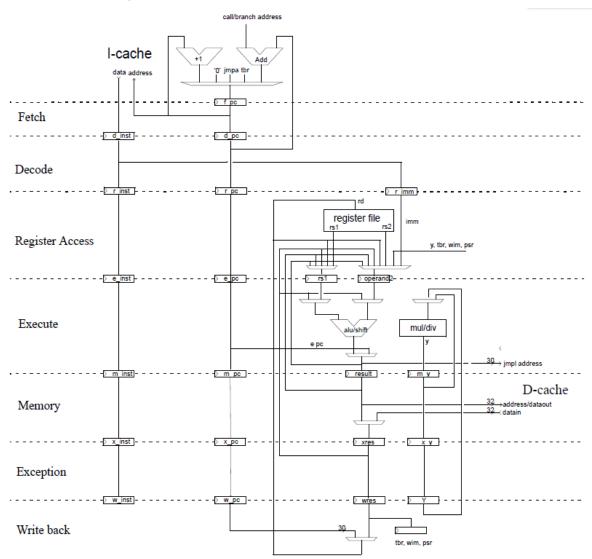

Figure 2.2: LEON 3FT Integer Unit Datapath Diagram

#### 2.1.10 Instruction Pipeline

The LEON 3FT integer unit uses a single instruction issue pipeline with seven stages:

- 2. FE (Instruction Fetch): If the instruction cache is enabled and a cache hit occurs, the instruction is fetched from the instruction cache. Otherwise, the fetch is forwarded to the memory controller. The instruction is valid at the end of this stage and is latched inside the IU.

- 3. DE (Decode): The instruction is decoded and the CALL or branch target address is generated.

- 4. RA (Register Access): Operands are read from the register file or from internal data bypasses.

- 5. EX (Execute): ALU, logical, and shift operations are performed. For memory operations (e.g., LD/ST) and JMPL/RETT instructions, the address is generated.

- 6. ME (Memory): Data cache is accessed. If a data cache miss occurs, data is accessed from system memory and the cache is updated. Store data read out in the execution stage is written to the data cache at this time.

- 7. XC (Exception) Traps and interrupts are resolved. For cache reads, the data is aligned as appropriate.

- 8. WR (Write): The result of any ALU, logical, shift, or cache operations are written back to the register file.

**Table 2.1** lists the cycles per instruction (assuming cache hit, and no integer condition codes or load interlock exist):

| INSTRUCTION            | CYCLES         |

|------------------------|----------------|

| JMPL                   | 31             |

| JMPL, RETT pair        | 4              |

| Double load            | 2              |

| Single store           | 2 <sup>3</sup> |

| Double store           | 3 <sup>3</sup> |

| SMUL/UMUL              | 12             |

| SDIV/UDIV              | 35             |

| Taken Trap             | 5 <sup>3</sup> |

| Atomic load/store      | 3              |

| All other instructions | 1              |

#### Table 2.1: Instruction Timing

#### 2.1.11 SPARC Implementer's ID

Cobham's Gaisler is assigned number 15 (0x0F) as SPARC implementer's identification. This value is hard-coded into bits 31:28 in the processor state register (%PSR:impl). The version number for LEON 3FT is 3, which is hard-coded in to bits 27:24 of the PSR (%PSR:ver).

#### 2.1.12 Division Instructions

Full support for SPARC V8 division instructions is provided via instruction SDIV, UDIV, SDIVCC and UDIVCC. The division instructions perform a 64-by-32 bit divide and produce a 32-bit result. Rounding and overflow detection is performed as defined in the SPARC V8 standard.

#### 2.1.13 Multiplication Instructions

The LEON 3FT processor supports the SPARC integer multiply instructions UMUL, SMUL UMULCC and SMULCC. These instructions perform 32x32-bit integer multiplication producing a 64-bit result. SMUL and SMULCC perform signed multiplication while UMUL and UMULCC perform unsigned multiplication. UMULCC and SMULCC also set the condition codes of the PSR to reflect the result

of the operation. The multiply instructions are performed using a 16x16 signed hardware multiplier, which is iterated four times. To improve timing, the 16x16 multiplier is implemented with a pipeline register stage.

#### 2.1.14 Hardware Breakpoints

The integer unit is configured with two hardware breakpoints. Each breakpoint consists of a pair of Ancillary State Registers (%asr24/25 and%asr26/27); one with the break address and one with a mask.

#### WPR1, WPR2

#### %asr24, %asr26

| Bit#  | 31 2        | 1 | 0  |

|-------|-------------|---|----|

| R     | W/ADD[21.2] |   | TE |

| W     | WADDR[31:2] |   | IL |

| Reset | []          |   | 0  |

#### Figure 2.3: Watchpoint Address Registers

#### Table 2.2: Description of Watchpoint Address Register

| BIT<br>NUMBER(S) | BIT NAME | RESET<br>STATE | DESCRIPTION                                                                                                         |

|------------------|----------|----------------|---------------------------------------------------------------------------------------------------------------------|

| 31-2             | WADDR    | -              | Watch Address<br>Defines the range of watch addresses used to<br>generate a breakpoint.                             |

| 1                | RESERVED |                |                                                                                                                     |

| 0                | IF       | 0              | Instruction Fetch Break Enable<br>0: Break on instruction fetch disabled.<br>1: Break on instruction fetch enabled. |

#### WPMR1, WPMR2

#### %asr25, %asr27

| Bit#  | 31 2        | 1  | 0  |

|-------|-------------|----|----|

| R     | MMACK[21·2] | DL |    |

| W     | WMASK[31:2] | DL | 05 |

| Reset | []          | 0  | 0  |

#### Figure 2.4: Watchpoint Mask Registers

#### Table 2.3: Description of Watchpoint Mask Register

| BIT<br>NUMBER(S) | BIT NAME    | RESET<br>STATE | DESCRIPTION                                                                                                              |

|------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------|

| 31-2             | WMASK[31:2] |                | Watch Mask<br>These bits mask or unmask the corresponding bits in the<br>WADDR.<br>0: Address bit not used by the WADDR. |

| BIT<br>NUMBER(S) | BIT NAME | RESET<br>STATE | DESCRIPTION                                                                          |

|------------------|----------|----------------|--------------------------------------------------------------------------------------|

|                  |          |                | 1: Address bit used by the WADDR.                                                    |

| 1                | DL       | 0              | Data Load Break Enable<br>0: Break on data load disabled<br>1: Break on data load    |

| 0                | DS       | 0              | Data Store Break Enable<br>0: Break on data store disabled<br>1: Break on data store |

Any binary aligned address range can be watched. The range is defined by the WADDR field and masked by the WMASK field (WMASK[n] = 1 enables comparison). On a breakpoint hit, trap 0x0B is generated. By setting the IF, DL and DS bits, a hit can be generated on instruction fetch, data load or data store. Clearing these three bits effectively disables the breakpoint function.

#### 2.1.15 Instruction Trace Buffer

The instruction trace buffer consists of a circular buffer that stores executed instructions. The trace buffer operation is controlled through the debug support interface and does not affect processor operation. The size of the trace buffer is 256 lines deep and 128 bits wide. The buffer stores the following information:

- Instruction address and opcode

- Instruction result

- Load/store data and address

- Trap information

- 30-bit time tag

The operation and control of the trace buffer is further described in **Chapter 14:**.

#### 2.1.16 Processor Configuration Register

The application specific register 17 (%asr17) provides information on configuration of the LEON 3FT core. This can be used to enhance the performance of software. The register can be accessed through the RDASR instruction and has the following layout:

| PCR |

|-----|

|-----|

#### %asr17

| Bit#  | 31 | 30 | 29 | 28 | 27  | 26   | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|-------|----|----|----|----|-----|------|----|----|----|----|----|----|----|----|----|----|

| R     |    | P  | ΡI |    | DET |      |    |    |    |    |    |    |    |    |    |    |

| W     |    |    |    |    |     | KF I |    |    |    |    |    |    |    |    |    |    |

| Reset |    | 00 | 00 |    |     | 00   | 00 |    |    |    |    | [  | ]  |    |    |    |

| Bit#  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7   | 6   | 5        | 4 | 3 | 2     | 1 | 0 |

|-------|----|----|----|----|----|----|----|----|-----|-----|----------|---|---|-------|---|---|

| R     |    |    | CV | LD | FF | บ  | м  | V8 | NWP |     | NWP NWIN |   |   |       |   |   |

| W     |    | DW | SV |    |    |    | IM |    |     |     |          |   |   |       |   |   |

| Reset |    | 0  | 0  | 0  | 0  | 1  | 0  | 1  |     | 010 |          |   |   | 00111 |   |   |

Figure 2.5: Processor Configuration Register

#### Table 2.4: Description of Processor Configuration Register

| BIT<br>NUMBER(S) | BIT NAME | RESET<br>STATE | DESCRIPTION                                                                                                                                                                                                      |

|------------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-28            | PI       | [000]          | Processor Index<br>In multi-processor systems, each LEON 3FT core gets a<br>unique index to support enumeration.<br>Read=0; Write=don't care.                                                                    |

| 27-24            | RFT      | [000]          | Register File RAM Timing Adjust Read=0000b; Must write 0000b.                                                                                                                                                    |

| 23-15            | RESERVED | []             |                                                                                                                                                                                                                  |

| 14               | DW       | 0              | Disable Write Error Trap<br>0: Write error trap ( <i>tt</i> =0x2b) ignored.<br>1: Write error trap ( <i>tt</i> =0x2b) allowed.                                                                                   |

| 13               | SV       | 0              | Single-Vector Trapping Enable<br>0: Single-vector trapping disabled.<br>1: Single-vector trapping enabled.                                                                                                       |

| 12               | LD       | 0              | Load Delay<br>0: One-cycle load delay is used.<br>1: Two-cycle load delay is used.<br>Read=0; Write=don't care.                                                                                                  |

| 11-10            | FPU      | 01             | Floating Point Implementation 00: No FPU<br>01: GRFPU (Hard Coded)<br>10: Meiko FPU<br>11: GRFPU-Lite<br>Read=01; Write=don't care.                                                                              |

| 9                | Μ        | 0              | MAC Implementation<br>0: Optional multiply-accumulate (MAC) instruction not<br>available.<br>1: Optional multiply-accumulate (MAC) instruction is<br>available.<br>Read=0; Write=don't care.                     |

| 8                | V8       | 1              | Multiply and Divide Implementation<br>0: SPARC V8 multiplication and division instructions not<br>available.<br>1: SPARC V8 multiplication and division instructions are<br>available. Read=1; Write=don't care. |

| 7-5              | NWP      | 010            | Watchpoint Implementation<br>Number of implemented watchpoints.<br>Read=010b; Write=don't care.                                                                                                                  |

| 4-0              | NWIN     | 00111          | Register Window Implementation<br>Number of implemented registers windows corresponds<br>to NWIN+1.<br>Read=00111b; Write=don't care.                                                                            |

#### 2.1.17 Exceptions

LEON 3FT adheres to the general SPARC trap model. The **Table 2.5** below shows the implemented traps and their individual priority. When a trap occurs while Processor Status Register (PSR) bit ET=0, the processor halts execution and enters an error mode. The external processor error signal will be asserted (Active Low).

## Table 2.5: Trap Allocation and Priority

| TRAP                     | π           | PRI | DESCRIPTION                                         | Class        |  |

|--------------------------|-------------|-----|-----------------------------------------------------|--------------|--|

| reset                    | 0x00        | 1   | Power-on reset                                      | Interrupting |  |

| write error              | 0x2B        | 2   | Write buffer error                                  | Interrupting |  |

| instruction_access_error | 0x01        | 3   | Error during instruction fetch                      | Precise      |  |

| Illegal_instruction      | 0x02        | 5   | UNIMP or other un-implemented instruction           | Precise      |  |

| privileged_instruction   | 0x03        | 4   | Execution of privileged instruction in<br>user mode | Precise      |  |

| fp_disabled              | 0x04        | 6   | FP instruction while FPU disabled                   | Precise      |  |

| cp_disabled              | 0x24        | 6   | CP instruction while co-processor<br>disabled       | Precise      |  |

| watchpoint_detected      | 0x0B        | 7   | Hardware breakpoint match                           | Precise      |  |

| window_overflow          | 0x05        | 8   | SAVE into invalid window                            | Precise      |  |

| window_underflow         | 0x06        | 8   | RESTORE into invalid window                         | Precise      |  |

| register_hardware_error  | 0x20        | 9   | Uncorrectable register file SEU error               | Interrupting |  |

| mem_address_not_aligned  | 0x07        | 10  | Memory access to un-aligned address                 | Precise      |  |

| fp_exception             | 0x08        | 11  | FPU exception                                       | Deferred     |  |

| cp_exception             | 0x28        | 11  | Co-processor exception                              | Deferred     |  |

| data_access_exception    | 0x09        | 13  | Access error during load or store<br>instruction    | Precise      |  |

| tag_overflow             | 0x0A        | 14  | Tagged arithmetic overflow                          | Precise      |  |

| divide_exception         | 0x2A        | 15  | Divide by zero                                      | Precise      |  |

| trap_instruction         | 0x80 - 0xFF | 16  | Software trap instruction (TA)                      | Precise      |  |

| interrupt_level_15       | 0x1F        | 17  | GPIO 15                                             | Interrupting |  |

| interrupt_level_14       | 0x1E        | 18  | GPIO 14 / ETH                                       | Interrupting |  |

| interrupt_level_13       | 0x1D        | 19  | GPIO 13 / SPW4                                      | Interrupting |  |

| interrupt_level_12       | 0x1C        | 20  | GPIO 12 / SPW3                                      | Interrupting |  |

| interrupt_level_11       | 0x1B        | 21  | GPIO 11 / SPW2                                      | Interrupting |  |

| interrupt_level_10       | 0x1A        | 22  | GPIO 10 / SPW1                                      | Interrupting |  |

| interrupt_level_9        | 0x19        | 23  | GPIO 9 / GPTIMER 4 / GR1553B/ SPI                   | Interrupting |  |

| interrupt_level_8        | 0x18        | 24  | GPIO 8 / GPTIMER 3                                  | Interrupting |  |

| interrupt_level_7        | 0x17        | 25  | GPIO 7 / GPTIMER 2                                  | Interrupting |  |

| interrupt_level_6        | 0x16        | 26  | GPIO 6 / GPTIMER 1                                  | Interrupting |  |

| interrupt_level_5        | 0x15        | 27  | GPIO 5 / CAN2                                       | Interrupting |  |

| interrupt_level_4        | 0x14        | 28  | GPIO 4 / CAN1                                       | Interrupting |  |

| interrupt_level_3        | 0x13        | 29  | GPIO 3                                              | Interrupting |  |

| interrupt_level_2        | 0x12        | 30  | GPIO 2 / APBUART                                    | Interrupting |  |

| interrupt_level_1        | 0x11        | 31  | GPIO 1 / AHBSTAT                                    | Interrupting |  |

## 2.1.18 Single Vector Interrupt (SVT)

The LEON 3FT supports Single-Vector Trapping (SVT) to reduce code size for embedded applications. When enabled, any taken trap always jumps to the reset trap handler whose address is defined by Trap Base Address Register (TBR) bits TBR.*tba*, or TBR[31:19], with the lower 12 bits don't care. The trap type will be indicated in TBR.*tt*, or TBR[11:4], and must be decoded by

the shared trap handler. SVT is enabled by setting bit 13 in the PCR (%asr17).

#### 2.1.19 Address Space Identifiers (ASI)

In addition to the address, the SPARC processor also generates an 8-bit Address Space Identifier (ASI) providing up to 256 separate, 32-bit address spaces. During normal operation, the LEON 3FT processor accesses instructions and data using ASI 0x08 - 0x0B as defined in the SPARC standard. The LDA/STA instructions are used to access the alternative address spaces. **Table 2.6** shows the ASI usage for LEON 3FT.

| ASI  | USAGE                            |  |  |  |  |  |

|------|----------------------------------|--|--|--|--|--|

| 0x01 | Forced cache miss                |  |  |  |  |  |

| 0x02 | System (cache control) registers |  |  |  |  |  |

| 0x08 | User instruction                 |  |  |  |  |  |

| 0x09 | Supervisor instruction           |  |  |  |  |  |

| 0x0A | User data                        |  |  |  |  |  |

| 0x0B | Supervisor data                  |  |  |  |  |  |

| 0x0C | Instruction cache tags           |  |  |  |  |  |

| 0x0D | Instruction cache data           |  |  |  |  |  |

| 0x0E | Data cache tags                  |  |  |  |  |  |

| 0x0F | Data cache data                  |  |  |  |  |  |

| 0x10 | Flush entire instruction cache   |  |  |  |  |  |

| 0x11 | Flush entire data cache          |  |  |  |  |  |

Table 2.6: ASI Usage

#### 2.1.20 Power-Down

The processor supports a power-down feature to minimize power consumption during idle periods. The power-down mode is entered by performing a WRASR instruction to %asr19:

#### wr %g0, %asr19 // write 0x0 to%asr19

During power-down, the pipeline is halted until the next interrupt occurs; therefore, this instruction should not be executed with interrupts disabled or the processor never wake up. Signals inside the processor pipeline and caches are then static, reducing power consumption from dynamic switching.

#### 2.1.21 Processor Reset Operation

The processor is reset by asserting the  $\overline{\text{RESET}}$  input for at least four clock cycles. **Table 2.7** indicates the reset values of the registers that are affected by the reset. All other registers either maintain their value or are undefined.

| REGISTER                        | RESET VALUE |

|---------------------------------|-------------|

| PC (Program Counter)            | 0x00000000  |

| nPC (Next Program Counter)      | 0x0000004   |

| PSR (Processor Status Register) | ET=0, S=1   |

#### Table 2.7: Processor Reset Value

Code execution starts at address 0 following a reset.

#### 2.1.22 Integer Unit SEU Protection

SEU protection for the integer unit register file (RF) is implemented with a Bose-Chaudhuri-Hocquenghem (BCH) algorithm utilizing 7 check bits. The protection logic can correct up to 1 error per 32-bit word in the register file and detect two errors. The correction is done transparently to the software and does not affect the instruction timing. If a detected SEU error cannot be corrected, trap 0x20 is generated.

ASR register 16 (%asr16) is used to control the IU register file SEU protection. It is possible to disable the SEU protection by setting the IDI bit and to inject errors using the TE bits. Corrected errors in the register file are counted and available in ICNT fields. The counter saturates at its maximum value (7) and should be reset by software after read-out.

| RPCR  |                    |    |    |      |    |    |    |    |    |    |    |    |    |    | %a | asr17 |

|-------|--------------------|----|----|------|----|----|----|----|----|----|----|----|----|----|----|-------|

| Bit#  | 31                 | 30 | 29 | 28   | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16    |

| R     |                    |    |    |      |    |    |    |    |    |    |    |    |    |    |    | IUFT  |

| W     |                    |    |    |      |    |    |    |    |    |    |    |    |    |    |    | 101.1 |

| Reset |                    |    |    |      |    |    |    | [] |    |    |    |    |    |    |    | 0     |

|       |                    |    |    |      |    |    |    |    |    |    |    |    |    |    |    |       |

| Bit#  | 15                 | 14 | 13 | 12   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0     |

| R     | т                  | ст |    | ICNT |    |    |    |    | г  | D  |    |    |    | DP | TE | RP    |

| W     | IUFT ICNT TB DP TE |    |    |      |    |    |    |    | ΚP |    |    |    |    |    |    |       |

| Reset | 10 [] []           |    |    |      |    |    |    | -  |    |    |    |    |    |    |    |       |

|       |                    |    |    | -    |    | •  |    |    |    |    |    |    |    |    |    | -     |

Figure 2.6: Register Protection Control Register

| Table 2.8: | Description of | of Register F | Protection | Control Register |

|------------|----------------|---------------|------------|------------------|

|------------|----------------|---------------|------------|------------------|

| BIT<br>NUMBER(S) | BIT NAME | RESET<br>STATE | DESCRIPTION                                                                                                                                                                  |

|------------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-17            | RESERVED | []             |                                                                                                                                                                              |

| 16-14            | IUFT     | 010            | Integer Unit Fault-Tolerant Identification<br>Read=010b<br>Write=don't care.                                                                                                 |

| 13-11            | ICNT     | []             | Integer Unit Register File Error Counter<br>Number of detected parity errors in the IU register file.<br>000: 0 errors<br>001: 1 error<br>010: 2 errors<br><br>111: 7 errors |

| BIT<br>NUMBER(S) | BIT NAME | RESET<br>STATE | DESCRIPTION                                                                                                                                                       |

|------------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-3             | ТВ       | []             | Register File Test Bits<br>In test mode, these bits are XORed with correct parity<br>bits and then written back to the register file.                             |

| 2                | DP       | -              | Diagnostic Parity RAM Select<br>Selects to insert errors in the main or redundant register<br>file memory. See the table below for a description of<br>operation. |

| 1                | TE       | -              | Integer Unit Register File Test Enable Disables or<br>enables register file test mode.<br>See the table below for a description of operation.                     |

| 0                | RP       | -              | Integer Unit Register File Protection Disable<br>0: Enable IU RF parity protection.<br>1: Disable IU RF parity protection.                                        |

#### 2.1.23 Data Scrubbing

When a data word in the register file is corrected, the corrected value is used during the execution of the current instruction, but not automatically written back to the register file. There is generally no need to perform data scrubbing (read-write operation) on the IU register file. During normal operation, the active part of the IU register files will be flushed to memory on each task switch. This causes all saved registers to be checked and corrected if necessary. Since most real-time operating systems perform several task switches per second, the data in the register file will be frequently refreshed.

# 8.1 Floating Point Unit

The UT699 SPARC V8 architecture is configured with the GRFPU from Cobham's Gaisler.

The high-performance GRFPU operates on single- and double-precision operands and implements all SPARC V8 FPU instructions except quad precision instructions. The FPU is interfaced to the LEON 3FT pipeline using a LEON 3FT-specific FPU controller (GRFPC) that allows FPU instructions to be executed simultaneously with integer instructions. Only in case of a data or resource dependency is the integer pipeline held. The GRFPU is fully pipelined and allows the start of one instruction each clock cycle, with the exception of FDIV and FSQRT, which can only be executed one at a time. The FDIV and FSQRT instructions are executed in a separate divide unit and do not block the GRFPU from performing other operations in parallel.

All instructions except FDIV and FSQRT have a latency of four clock cycles at instruction level. **Table 2.9** below shows the GRFPU instruction timing when used together with GRFPC.

| INSTRUCTION                                                                                                                    | THROUGHPUT | LATENCY |

|--------------------------------------------------------------------------------------------------------------------------------|------------|---------|

| FADDS, FADDD, FSUBS, FSUBD, FMULS, FMULD,<br>FSMULD, FITOS, FITOD, FSTOI, FDTOI, FSTOD,<br>FDTOS, FCMPS, FCMPD, FCMPES, FCMPED | 1          | 4       |

| FDIVS                                                                                                                          | 14         | 16      |

| FDIVD                                                                                                                          | 15         | 17      |

| FSQRTS                                                                                                                         | 22         | 24      |

#### Table 2.9: GRFPU Worst-Case Instruction Timing with GRFPC

| INSTRUCTION | THROUGHPUT | LATENCY |

|-------------|------------|---------|

| FSQRTD      | 23         | 25      |

The GRFPU controller uses the SPARC deferred traps and the GRFPU deferred trap queue (FQ) can contain up to eight queued instructions when a GRFPU exception is taken. The register file for the GRFPU consists of thirty-two, 32-bit registers. In the UT699, the register file has been implemented with SEU-hardened flip-flops and does not need SEU error detection or correction.

# 8.2 Cache Sub-System

The processor's L1 cache will cache addresses that are marked as cacheable. The cacheable address ranges are:

- PROM area : 0x0000\_0000 0x1FFF\_FFFF

- SRAM/SDRAM area : 0x4000\_0000 0x7FFF\_FFFF

When the processor has a memory location in cache and the same memory location is updated by another bus master (PCI controller, Ethernet controller, SpaceWire controllers) then the cache will not be automatically updated and the L1 cache will contain stale data. To maintain coherency between external memory and the L1 cache all memory areas that may be updated by other AMBA masters need to be accessed using forced cache misses (load alternate instruction to ASI 0x01). Coherency can also be attained by performing a cache flush before accessing shared memory areas.

Cache coherency is maintained using bus snooping. When the processor has a memory location in cache and the same memory location is updated by another bus master (PCI controller, Ethernet controller, SpaceWire controllers) then the corresponding cache line will be automatically invalidated by the processor. Cache coherency using snooping is only available for the data cache. If instructions that may be in the instruction cache are modified in external memory, then the L1 instruction cache needs to be flushed.

Compatibility note: The UT699 does not support bus snooping and does not automatically maintain cache coherency. Therefore, software written for the UT699 may force cache misses (using load alternate with ASI 0x01) when accessing shared memory areas. The UT700/UT699E always fetches a full cache line on a cache miss. Code that makes use of ASI 0x01 for each load operation may cause an unnecessary large number of misses and this leads to performance degradation.

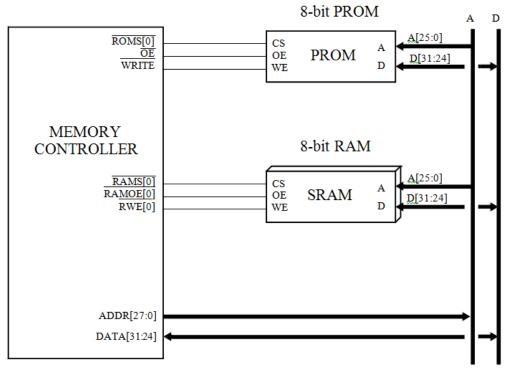

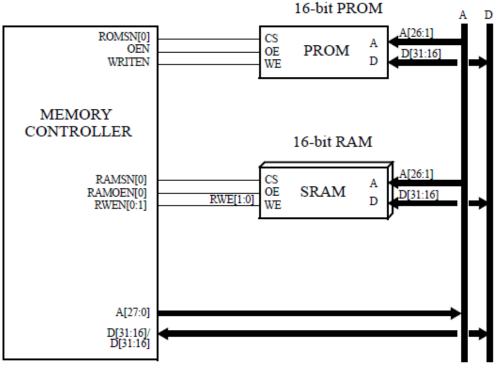

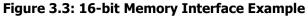

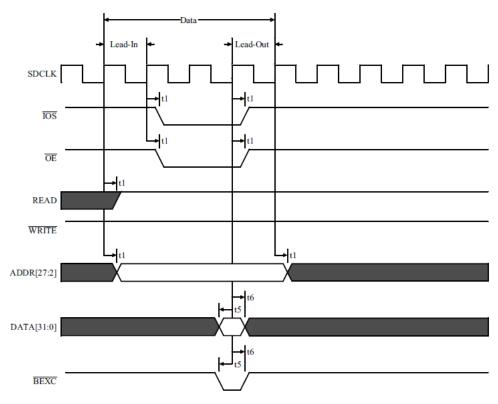

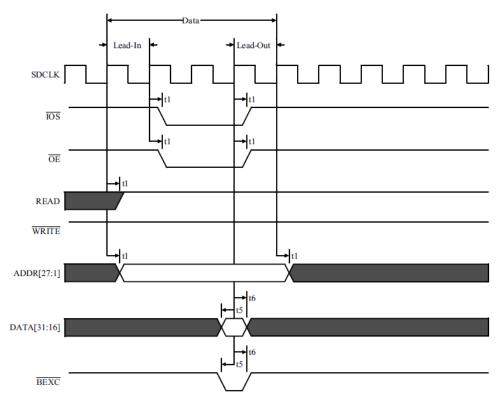

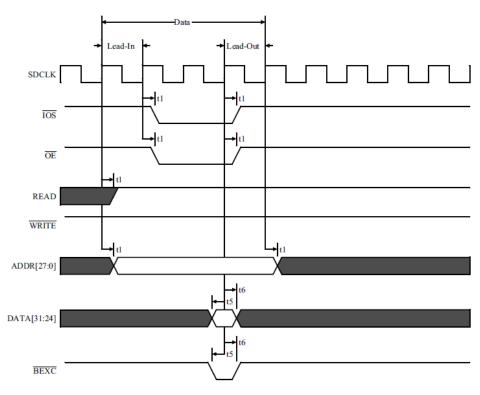

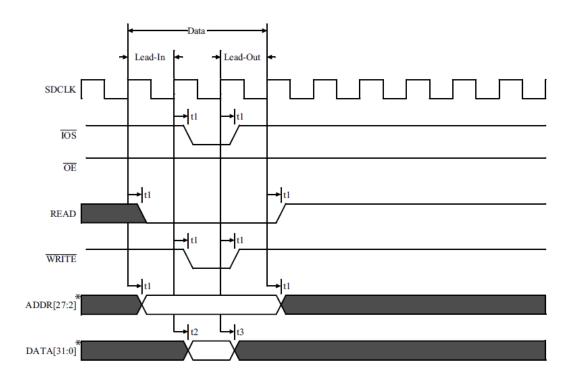

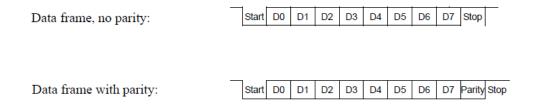

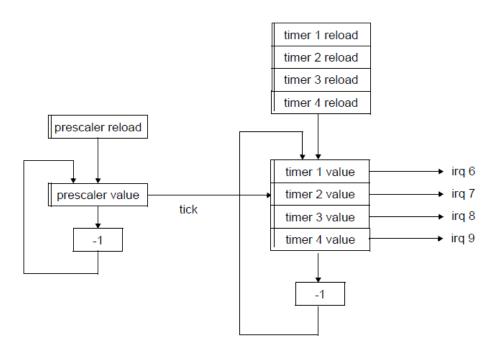

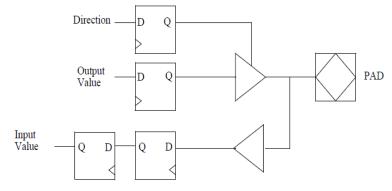

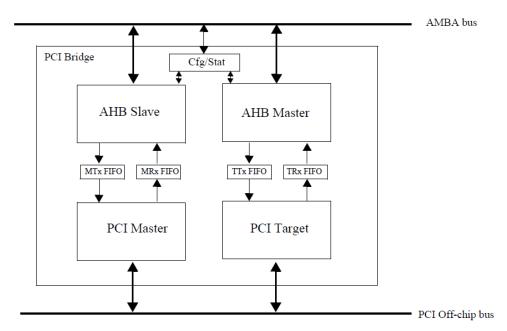

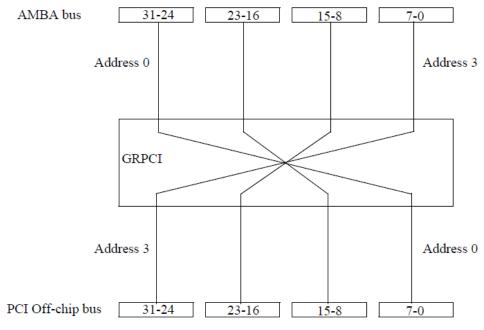

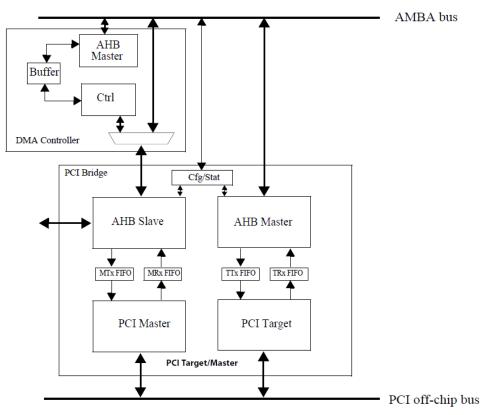

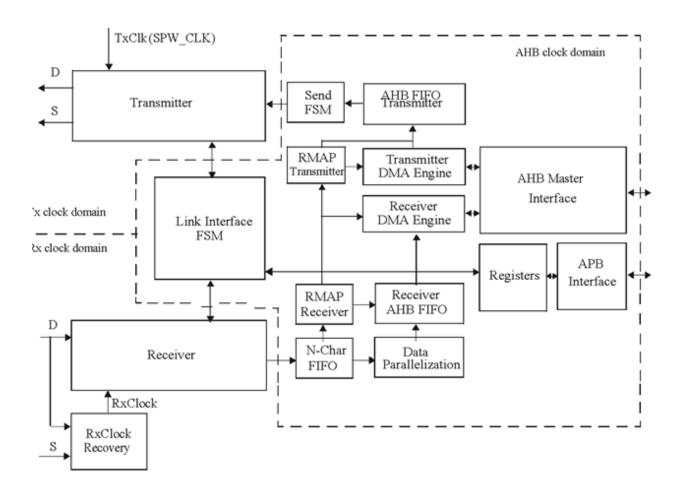

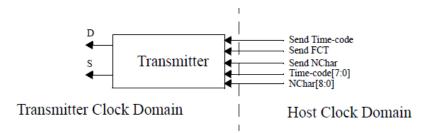

#### 2.1.24 Overview