# UT32M0R500 Functional Manual

32-Bit Arm® Cortex®-M0+ Microcontroller

### **Contents**

| 1  | Intro | oduction                             | 14 |

|----|-------|--------------------------------------|----|

| 1. | .1    | Scope                                | 14 |

| 1. | .2    | Related Resources                    | 14 |

| 1. | .3    | Architecture                         | 14 |

| 1. | .4    | Features                             | 15 |

| 1. | .5    | Generic Register Format              | 16 |

| 2  | ARM   | I Cortex M0+ Processor               | 17 |

| 2. | .1    | Overview                             | 17 |

| 2. | .2    | Processor Core                       | 18 |

| 2. | .3    | 2-stage Pipeline                     | 18 |

| 2. | .4    | NVIC                                 | 18 |

| 2. | .5    | WIC                                  | 18 |

| 2. | .6    | Bus Interface                        | 18 |

| 2. | .7    | Debug System                         | 18 |

| 2. | .8    | Cortex M0+ Registers                 | 18 |

| 2. | .9    | Memory Protection Unit (MPU)         | 19 |

| 2. | .10   | Clocking System                      | 19 |

| 3  | ARM   | I Cortex M0+ Registers               | 21 |

| 3. | .1    | Overview                             | 21 |

| 3. | .2    | Cortex M0+ General-Purpose Registers | 21 |

| 3. | .3    | Stack Pointer (SP)                   | 22 |

| 3. | .4    | Link Register (LR)                   | 22 |

| 3. | .5    | Program Counter (PC)                 | 22 |

| 3. | .6    | Program Status Registers (PSR)       | 22 |

| 3. | .7    | Interrupt Mask Register (PRIMASK)    | 22 |

| 3. | .8    | Control Register (CONTROL)           | 22 |

| 4  | ARM   | Cortex M0+ Instruction Set           | 23 |

| 4. | .1    | Overview                             | 23 |

| 4. | .2    | Memory Access: LOAD                  | 25 |

| 4. | .3    | Memory Access: STORE                 | 25 |

| 4. | .4    | Multiple Data Access                 | 25 |

| 4. | .5    | Stack Access: PUSH and POP           | 26 |

| 4. | .6    | Arithmetic ADD                       | 26 |

| 4. | .7    | Arithmetic SUB, MUL                  | 26 |

| 4. | .8    | Arithmetic CMP                       | 27 |

|   | 4.9   | Logic Operations                       | . 27 |

|---|-------|----------------------------------------|------|

|   | 4.10  | Arithmetic Shift Operation             | . 27 |

|   | 4.11  | Logic Shift Operation                  | . 27 |

|   | 4.12  | Rotate Operation                       | . 28 |

|   | 4.13  | Reverse Ordering Operation             | . 28 |

|   | 4.14  | Extended Operation                     | . 28 |

|   | 4.15  | Program Flow Control                   | . 28 |

| 5 | Arm   | Cortex M0+ Memory Map                  | 29   |

|   | 5.1   | Overview                               | . 29 |

|   | 5.2   | Boot ROM                               | 31   |

|   | 5.3   | Embedded SRAM                          | 32   |

| 6 | Nest  | ted Vector Interrupt Controller (NVIC) | 33   |

|   | 6.1   | Overview                               | . 33 |

|   | 6.2   | Interrupts                             | . 34 |

|   | 6.3   | Reset Vector                           | . 35 |

|   | 6.4   | Non Maskable Interrupt (NMI)           | . 35 |

|   | 6.5   | HardFault                              | . 35 |

|   | 6.6   | SVCall (SuperVisor Call)               | . 35 |

|   | 6.7   | PendSV (Pendable Service Call)         | . 35 |

|   | 6.8   | SysTick                                | . 35 |

|   | 6.9   | External Interrupts                    | . 35 |

|   | 6.9.1 | Level and Edge-Triggered Interrupts    | . 35 |

|   | 6.10  | Interrupt Priorities                   | . 36 |

|   | 6.11  | CMSIS functions for NVIC registers     | 36   |

|   | 6.12  | Wake-up Interrupt Controller           | . 36 |

| 7 | Pow   | er Management                          | 37   |

|   | 7.1   | Overview                               | . 37 |

|   | 7.2   | Wakeup Interrupt Controller            | . 37 |

|   | 7.3   | Sleep-On-Exit                          | . 37 |

|   | 7.4   | System Control Register                | . 37 |

|   | 7.5   | CMSIS functions for SCR register       | . 38 |

| 8 | Syst  | em Controller (SYSCON)                 | 39   |

|   | 8.1   | Overview                               | . 39 |

|   | 8.2   | "Keep Alive" Functionality             | . 39 |

|   | 8.3   | System Controller Register Details     | 40   |

|   | 8.3.1 | Boot Done Register (BOOT DONE)         | 40   |

|    | 8.3.2   | Power Management Unit Control Register (PMU_CTRL)      | 41 |

|----|---------|--------------------------------------------------------|----|

|    | 8.3.3   | Reset Control Register (RST_CTRL)                      | 42 |

|    | 8.3.4   | Boot Configuration Value Register (BOOTCFG_VALUE)      | 43 |

|    | 8.3.5   | Reset Information Register (RESET_INFO)                | 44 |

|    | 8.3.6   | Reset Count Register (RESET_COUNT)                     | 45 |

|    | 8.3.7   | Clock Divider Register (CLK_DIVIDE)                    | 46 |

|    | 8.3.8   | Clock Control Register (OSC_SHUTDOWN)                  | 47 |

|    | 8.3.9   | Analog Circuitry Shutdown Register (ANALOG_SHUTDOWNS)  | 48 |

|    | 8.3.10  | General Purpose Register 0 (GPREG0)                    | 49 |

|    | 8.3.11  | General Purpose Register 1 (GPREG1)                    | 50 |

|    | 8.3.12  | General Purpose Register 2 (GPREG2)                    | 51 |

| 9  | SRAM C  | Controller with EDAC and Scrubbing                     | 52 |

| 9. | 1 Ove   | erview                                                 | 52 |

| 9. | 2 AH    | B-to-SRAM Interface Register Details                   | 52 |

|    | 9.2.1   | Control Register (CONTROL)                             | 53 |

|    | 9.2.2   | Timer Count Register (TIMER_COUNT)                     | 53 |

|    | 9.2.3   | Timer Reload Value Register (TIMER_RELOAD)             | 54 |

|    | 9.2.4   | MBEA Interrupt Status Register (INT_STATUS)            | 54 |

|    | 9.2.5   | Scrub Max Address Register (MAX_ADDRESS)               | 55 |

|    | 9.2.6   | Single Bit Error Port A Register (SBE_COUNT_A)         | 55 |

|    | 9.2.7   | Single Bit Error Port B Register (SBE_COUNT_B)         | 56 |

|    | 9.2.8   | Multiple Bit Error Port A Register (SCRUB.MBE_COUNT_A) | 56 |

|    | 9.2.9   | Multiple Bit Error Port B Register (MBE_COUNT_B)       | 57 |

|    | 9.2.10  | Address of the Last MBE Event Register (LAST_ADDRESS)  | 57 |

| 10 | NOR     | Flash Controller (NFC)                                 | 58 |

| 10 | 0.1 Ove | erview                                                 | 58 |

| 10 | 0.2 NF  | C Register Details                                     | 59 |

|    | 10.2.1  | Control Register (CONTROL)                             | 60 |

|    | 10.2.2  | Status Register (STATUS)                               | 61 |

|    | 10.2.3  | Sector Address Register (SECTOR_ADDR)                  | 62 |

|    | 10.2.4  | Peripheral ID0 Register (PERIPH_ID0)                   | 63 |

|    | 10.2.5  | Peripheral ID1 Register (PERIPH_ID1)                   | 63 |

|    | 10.2.6  | Peripheral ID2 Register (PERIPH_ID2)                   | 64 |

|    | 10.2.7  | Peripheral ID3 Register (PERIPH_ID3)                   | 64 |

|    | 10.2.8  | Peripheral ID4 Register (PERIPH_ID4)                   | 65 |

|    | 10.2.9  | Peripheral ID5 Register (PERIPH ID5)                   | 65 |

|   | 10.2  | 2.10  | Peripheral ID6 Register (PERIPH_ID6)         | 66 |

|---|-------|-------|----------------------------------------------|----|

|   | 10.2  | 2.11  | Peripheral ID7 Register (PERIPH_ID7)         | 66 |

|   | 10.2  | .12   | Peripheral ID8 Register (PERIPH_ID8)         | 67 |

|   | 10.2  | .13   | Peripheral ID9 Register (PERIPH_ID9)         | 67 |

|   | 10.2  | 2.14  | Peripheral ID10 Register (PERIPH_ID10)       | 68 |

|   | 10.2  | .15   | Peripheral ID11 Register (PERIPH_ID11)       | 68 |

|   | 10.2  | 2.16  | Peripheral ID12 Register (PERIPH_ID12)       | 69 |

|   | 10.2  | 2.17  | Peripheral ID13 Register (PERIPH_ID13)       | 69 |

|   | 10.2  | .18   | Peripheral ID14 Register (PERIPH_ID14)       | 70 |

|   | 10.2  | 2.19  | Peripheral ID15 Register (PERIPH_ID15)       | 70 |

| 1 | .1 A  | RM K  | eil uVsion Tools                             | 71 |

|   | 11.1  | Over  | view                                         | 71 |

|   | 11.2  | MDK   | Tools                                        | 72 |

|   | 11.3  | Softw | vare Packs                                   | 72 |

|   | 11.4  | MDK   | Editions                                     | 72 |

| 1 | .2 B  |       | onfiguration                                 |    |

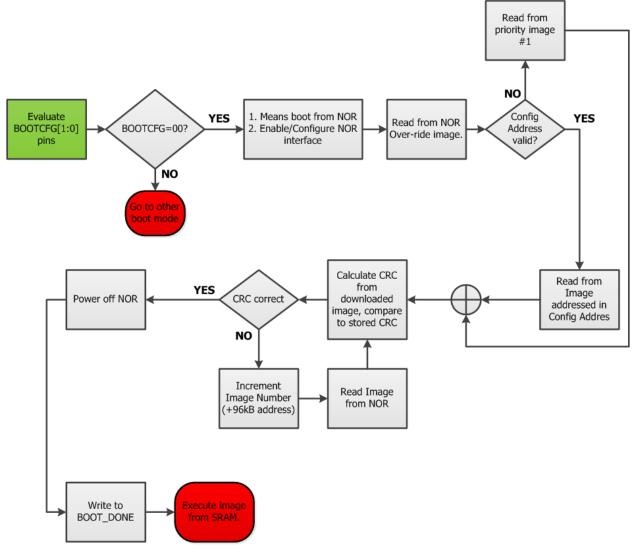

|   | 12.1  |       | Mode 0 (BOOTCFG = 2'b00)                     |    |

|   | 12.2  |       | Mode 1 (BOOTCFG = 2'b01)                     |    |

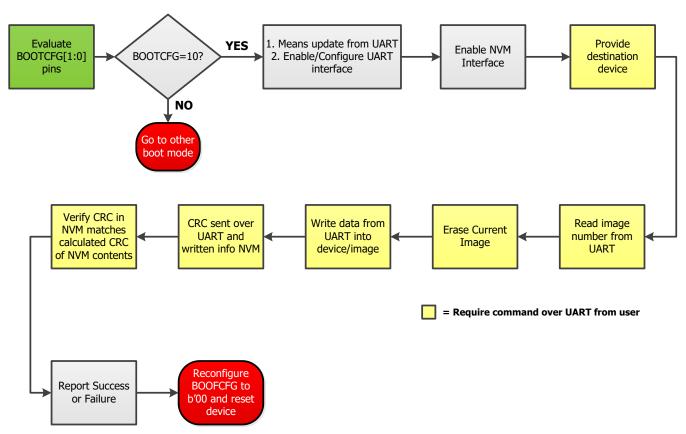

|   | 12.3  |       | Mode 2 (BOOTCFG = 2'b10)                     |    |

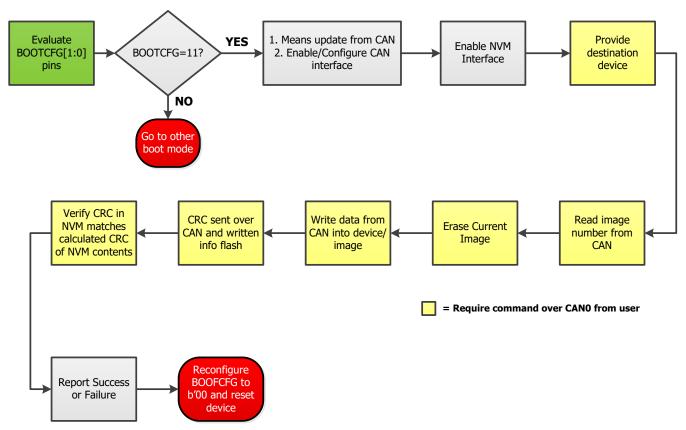

|   | 12.4  |       | Mode 3 (BOOTCFG = 2'b11)                     |    |

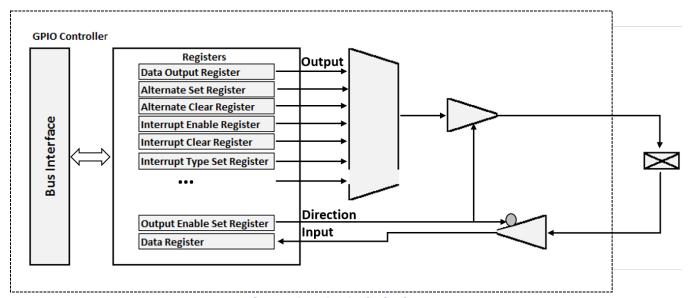

| 1 |       |       | al Purpose Input/Output (GPIO) Port          |    |

|   | 13.1  |       | view                                         |    |

|   | 13.2  |       | tional Description                           |    |

|   | 13.3  |       | ation                                        |    |

|   | 13.4  |       | nal Interrupt generation                     |    |

|   | 13.5  |       | ed access                                    |    |

|   | 13.6  |       | Reset Mode                                   |    |

|   | 13.7  |       | nate Function Configuration                  |    |

|   | 13.8  | •     | t Configuration                              |    |

|   | 13.9  | -     | ut Configuration                             |    |

|   | 13.10 |       | gisters                                      |    |

|   | 13.1  |       | DATA Register (DATA)                         |    |

|   | 13.1  |       | Data Out Register (DATAOUT)                  |    |

|   | 13.1  |       | Output Enable Set Register (OUTENABLESET)    |    |

|   | 13.1  |       | Output Enable Clear Register (OUTENABLECLR)  |    |

|   | 13.1  | .U.5  | AILETHALE FUNCTION SEL KEGISLEF (ALTFUNCSET) | oυ |

|    | 13.10.6  | Alternate Function Clear Register (ALTFUNCCLR)                                   | 86  |

|----|----------|----------------------------------------------------------------------------------|-----|

|    | 13.10.7  | Interrupt Enable Set Register (INTENSET)                                         | 87  |

|    | 13.10.8  | Interrupt Enable Clear Register (INTENCLR)                                       | 87  |

|    | 13.10.9  | Interrupt Type Set Register (INTTYPESET)                                         | 88  |

|    | 13.10.10 | Interrupt Type Clear Register (INTTYPECLR)                                       | 88  |

|    | 13.10.11 | Interrupt Polarity Level and Edge Configuration Set Register (INTPOLSET)         | 89  |

|    | 13.10.12 | 2 Interrupt Polarity Level and Edge Configuration Clear Register (INTPOLCLR)     | 89  |

|    | 13.10.13 | Interrupt Request Clear Register (INTSTATUS, INTCLEAR)                           | 91  |

|    | 13.10.14 | Soft Reset Option Enable Register (SOFT_RESET)                                   | 91  |

|    | 13.10.15 | Pullup/Pulldown Enable Register (PULL_ENABLE)                                    | 92  |

|    | 13.10.16 | Pullup/Pulldown Configuration Register (PULL_UP_DOWN)                            | 92  |

|    | 13.10.17 | Low Byte Access Mask Register (LB_MASKED)                                        | 93  |

|    | 13.10.18 | B Upper Byte Access Mask Register (UB_MASKED)                                    | 93  |

| 14 | Anal     | og-to-Digital Converter (ADC)                                                    | 94  |

| 14 | .1 Ov    | erview                                                                           | 94  |

| 14 | .2 AD    | C Filter Selection                                                               | 96  |

| 14 | .3 CO    | I Filter                                                                         | 96  |

| 14 | .4 Sin   | c4 Filter                                                                        | 96  |

| 14 | .5 Ou    | tput Word Range                                                                  | 97  |

| 14 | .6 AD    | C Module Functionality                                                           | 98  |

|    | 14.6.1   | Interrupt Functionality                                                          | 98  |

|    | 14.6.2   | System Clock Speed Requirements                                                  | 98  |

|    | 14.6.3   | ADC_SEQDLY Requirements                                                          | 99  |

|    | 14.6.4   | Calculating Channel Conversion Time                                              | 100 |

|    | 14.6.5   | Conversion Error Flags and Their Meanings                                        | 101 |

| 14 | .7 AD    | C Register Details                                                               | 102 |

|    | 14.7.1   | SPB Configuration Register 0 (SPB_CFG_0)                                         | 105 |

|    | 14.7.2   | SPB Configuration Register 1 (ADC.SPB_CFG_1)                                     | 107 |

|    | 14.7.3   | Single-Ended Channel Configuration Register (SECHAN_CFG[0] to SECHAN_CFG[15])    | 108 |

|    | 14.7.4   | Differential Channel Configuration Register (DIFFCHAN_CFG[0] to DIFFCHAN_CFG[7]) | 109 |

|    | 14.7.5   | Temperature Channel Configuration Register (TEMPCHAN_CFG)                        | 110 |

|    | 14.7.6   | Timing Control Register (TIM_CTRL)                                               |     |

|    | 14.7.7   | Sequence Control Register (SEQ_CTRL)                                             |     |

|    | 14.7.8   | DSM Digital Stability Control (STAB_CTRL)                                        | 114 |

|    | 14.7.9   | Interrupt Status Register (INT_STATUS)                                           | 115 |

|    | 14.7.10  | Data Output Word Register (DATA)                                                 | 117 |

| 15   | Digita | al-to-Analog (DAC)                                   | 119 |

|------|--------|------------------------------------------------------|-----|

| 15.1 | Ove    | rview                                                | 119 |

| 15.2 | DAG    | Register Details                                     | 119 |

| 15   | .2.1   | Control Register (CONTROL)                           | 120 |

| 15   | .2.2   | DAC0 Data Register (DATA1)                           | 121 |

| 15   | .2.3   | DAC1 Data Register (DATA2)                           | 122 |

| 16   | Comp   | parators                                             | 123 |

| 16.1 | Ove    | rview                                                | 123 |

| 16.2 | Cor    | nparator Register Details                            | 123 |

| 16   | 5.2.1  | Control Register (CTRL)                              | 124 |

| 16   | 5.2.2  | Status Register (STATUS)                             | 125 |

| 17   | Time   | 'S                                                   | 126 |

| 17.1 | Ove    | rview                                                | 126 |

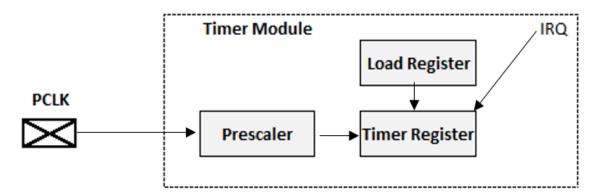

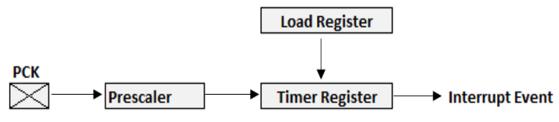

| 17.2 | Fur    | ctional Description                                  | 126 |

| 17.3 | Ope    | eration                                              | 127 |

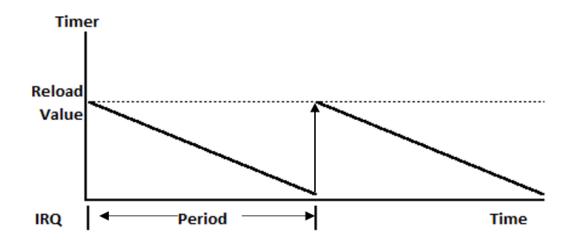

| 17   | '.3.1  | Prescaler                                            | 127 |

| 17   | '.3.2  | Free-Running Mode                                    | 128 |

| 17   | '.3.3  | Periodic Timer Mode                                  | 128 |

| 17   | '.3.4  | One-Shot Timer Mode                                  | 128 |

| 17.4 | Tim    | er Register Details                                  | 129 |

| 17   | '.4.1  | Timer X Load Register (TIMERxLOAD)                   | 130 |

| 17   | '.4.2  | Timer X Counter Current Value Register (TIMERxVALUE) | 130 |

| 17   | '.4.3  | Timer X Control Register (TIMERxCONTROL)             |     |

| 17   | .4.4   | Timer X Interrupt Clear Register (TIMERxINTCLR)      | 132 |

| 17   | '.4.5  | Timer X Raw Interrupt Status Register (TIMERxRIS)    | 132 |

| 17   | '.4.6  | Timer X Masked Interrupt Status Register (TIMERxMIS) | 133 |

| 17   | '.4.7  | Timer X Background Load Register (TIMERxBGLOAD)      | 133 |

| 18   |        | Width Modulator (PWM)                                |     |

| 18.1 |        | rview                                                |     |

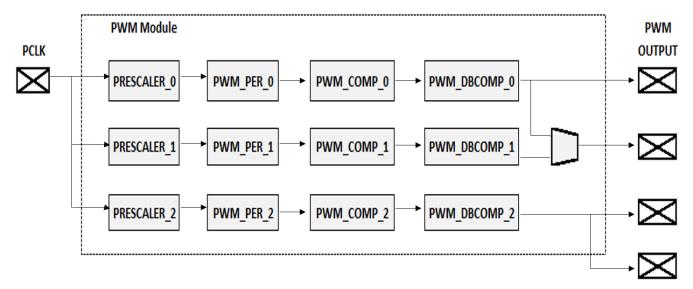

| 18.2 | Fur    | ctional Description                                  | 134 |

| 18.3 | Ope    | eration                                              | 135 |

| 18   | 3.3.1  | Prescaler                                            |     |

| 18   | 3.3.2  | Single Output Signal                                 | 137 |

| 18   | 3.3.3  | Paired Output Signal                                 | 138 |

| 18   | 3.3.4  | Dead Band Time                                       | 139 |

| 18   | 3.3.5  | Interrupts                                           | 140 |

| 1  | 8.4  | PWM   | 1 Register Details                               | . 142 |

|----|------|-------|--------------------------------------------------|-------|

|    | 18.4 | .1    | Core Control Register (CTRLREG)                  | . 143 |

|    | 18.4 | .2    | Scaler Reload Register (SCALREG)                 | . 144 |

|    | 18.4 | .3    | Interrupt Pending Register (IRQREG)              | . 144 |

|    | 18.4 | .4    | Capability Register 1 (CAPREG1)                  | . 145 |

|    | 18.4 | .5    | Capability Register 2 (CAPREG2)                  | . 146 |

|    | 18.4 | .6    | Period Register (PWM_PER_X)                      | . 147 |

|    | 18.4 | .7    | Compare Register (PWM_COMP_X)                    | . 148 |

|    | 18.4 | .8    | Dead Band Compare Register (PWM_DBCOMP_X)        | . 149 |

|    | 18.4 | .9    | Control Register (PWM_CTRL_X)                    | . 150 |

| 19 | W    | Vatch | ndog Timer (WDT)                                 | 153   |

| 1  | 9.1  | Over  | view                                             | . 153 |

| 1  | 9.2  | Wato  | chdog Timer Register Details                     | . 153 |

|    | 19.2 | .1    | Load Register (LOAD)                             | . 154 |

|    | 19.2 | .2    | Current Count Value Register (VALUE)             | . 154 |

|    | 19.2 | .3    | Control Register (CONTROL)                       | . 155 |

|    | 19.2 | .4    | Interrupt Clear Register (INT_CLR)               | . 156 |

|    | 19.2 | .5    | Interrupt Status Register (RAW_INT_STAT)         | . 157 |

|    | 19.2 | .6    | Masked Interrupt Status Register (MASK_INT_STAT) | . 158 |

|    | 19.2 | .7    | Window Value Register (WINDOW_VALUE)             | . 159 |

|    | 19.2 | .8    | Lock Register (LOCK)                             | . 160 |

| 20 | R    | eal T | ime Counter (RTC)                                | 161   |

| 2  | 0.1  | Over  | view                                             | . 161 |

| 2  | 0.2  | Func  | tional Description                               | . 162 |

| 2  | 0.3  | Oper  | ration                                           | . 162 |

| 2  | 0.4  | RTC   | Register Details                                 | . 163 |

|    | 20.4 | .1    | Current Count Value Register (CCVR)              | . 163 |

|    | 20.4 | .2    | Counter Match Register (CMR)                     | . 164 |

|    | 20.4 | .3    | Counter Load Register (CLR)                      | . 164 |

|    | 20.4 | .4    | Counter Control Register (CCR)                   | . 165 |

|    | 20.4 | .5    | Interrupt Status Register (STAT)                 | . 166 |

|    | 20.4 | .6    | Interrupt Raw Status Register (RSTAT)            |       |

|    | 20.4 | .7    | End of Interrupt Register (EOI)                  | . 167 |

|    | 20.4 | .8    | Component Version Register (CMP_VER)             | . 167 |

| 21 | U    | nive  | rsal Asynchronous Receiver/Transmitter (UART)    | 168   |

| 2  | 1.1  | Over  | view                                             | . 168 |

| 2  | 21.2  | Prot  | ocol                              | 168 |

|----|-------|-------|-----------------------------------|-----|

| 2  | 21.3  | Chai  | acter-Encoding Scheme             | 169 |

| 2  | 21.4  | Baud  | d-Rate Generation                 | 169 |

| 2  | 21.5  | Ope   | ration                            | 169 |

|    | 21.5  | .1    | Transmitter Operation             | 169 |

|    | 21.5  | .2    | Receiver Operation                | 170 |

| 2  | 21.6  | Loop  | back mode                         | 170 |

| 2  | 21.7  | FIFC  | debug mode                        | 171 |

| 2  | 21.8  | Exte  | rnal Interrupt                    | 171 |

| 2  | 21.9  | UAR   | T Register Details                | 172 |

|    | 21.9  | .1    | Data Register (DATA)              | 172 |

|    | 21.9  | .2    | Status Register (STATUS)          | 173 |

|    | 21.9  | .3    | Control Register (CONTROL)        | 175 |

|    | 21.9  | .4    | Scaler Register (SCALER)          | 177 |

|    | 21.9  | .5    | FIFO Debug Register (FIFO_DEBUG)  | 177 |

| 22 | S     | erial | Peripheral Interface (SPI)        | 178 |

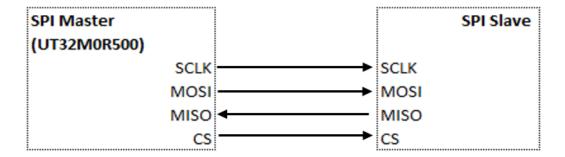

| 2  | 22.1  | Ove   | rview                             | 178 |

| 2  | 22.2  | Cloc  | k generation                      | 179 |

| 2  | 22.3  | Ope   | ration                            | 179 |

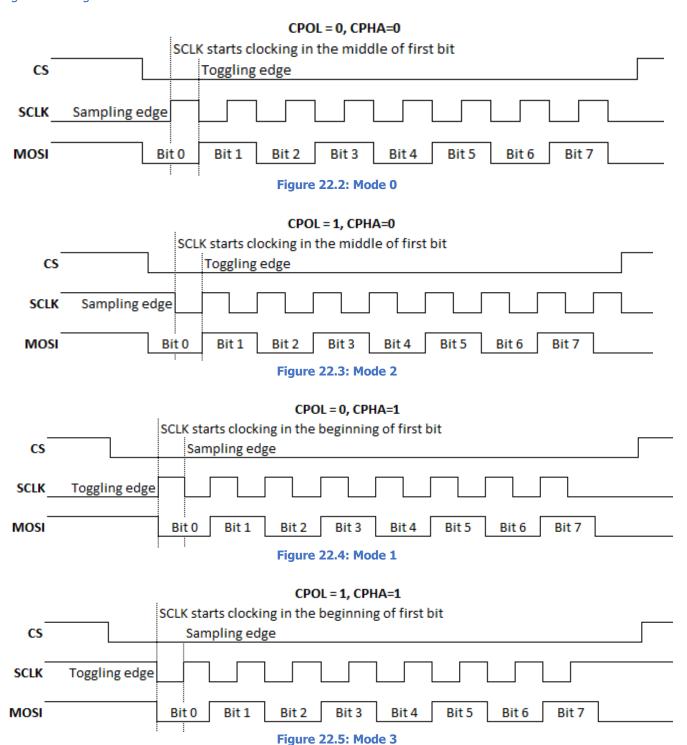

|    | 22.3  | .1    | Clocking Modes                    | 179 |

| 2  | 22.4  | Tran  | smit and Receive FIFO Buffers     | 181 |

| 2  | 22.5  | Exte  | rnal Interrupt                    | 181 |

| 2  | 22.6  | FIFC  | Empty Interrupt                   | 181 |

| 2  | 22.7  | FIFC  | Full Interrupt                    | 181 |

| 2  | 22.8  | FIFC  | Overrun Interrupt                 | 181 |

| 2  | 22.9  | Tran  | sfer Modes                        | 182 |

|    | 22.9  | .1    | Transmit and Receive, TMOD = 00   | 182 |

|    | 22.9  | .2    | Transmit Only, TMOD = 01          |     |

|    | 22.9  | .3    | Receive Only, TMOD = 10           |     |

|    | 22.9  | .4    | EEPROM Read, TMOD = 11            | 182 |

| 2  | 22.10 | D     | ata Transfers                     | 182 |

|    | 22.1  | 0.1   | SPI Register Details              | 183 |

|    | 22.1  | 0.2   | Control Register 0 (CTRLR0)       | 184 |

|    | 22.1  | 0.3   | Control Register 1 (CTRLR1)       | 186 |

|    | 22.1  | 0.4   | SSI Enable Register (SPIENR)      | 187 |

|    | 22.1  | 0.5   | Microwire Control Register (MWCR) | 188 |

| 22.1 | 0.6   | Slave Enable Register (SER)                              | 188 |

|------|-------|----------------------------------------------------------|-----|

| 22.1 | 0.7   | Baud Rate Select Register (BAUDR)                        | 189 |

| 22.1 | 8.0.  | Transmit FIFO Threshold Level Register (TXFTLR)          | 190 |

| 22.1 | 0.9   | Receive IFO Threshold Level Register (RXFTLR)            | 191 |

| 22.1 | 0.10  | Transmit FIFO Level Register (TXFLR)                     | 191 |

| 22.1 | 0.11  | Receive FIFO Level Register (RXFLR)                      | 192 |

| 22.1 | 0.12  | Status Register (SR)                                     | 193 |

| 22.1 | 0.13  | Interrupt Mask Register (IMR)                            | 194 |

| 22.1 | 0.14  | Interrupt Status Register (ISR)                          | 195 |

| 22.1 | 0.15  | Raw Interrupt Status Register (RISR)                     | 196 |

| 22.1 | 0.16  | Transmit FIFO Overflow Interrupt Clear Register (TXOICR) | 197 |

| 22.1 | 0.17  | Receive FIFO Overflow Interrupt Clear Register (RXOICR)  | 197 |

| 22.1 | 0.18  | Receive FIFO Underflow Interrupt Clear Register (RXUICR) | 198 |

| 22.1 | 0.19  | Multi-Master Interrupt Clear Register (MSTICR)           | 198 |

| 22.1 | 0.20  | Interrupt Clear Register (ICR)                           | 199 |

| 22.1 | 0.21  | Identification Register (IDR)                            | 200 |

| 22.1 | 0.22  | CoreKit Version ID Register (SSI_COMP_VERSION)           | 201 |

| 22.1 | 0.23  | DR Register (DR)                                         | 202 |

| 22.1 | 0.24  | RXD Sample Delay Register (RX_SAMPLE_DLY)                | 203 |

| 23 I | nter- | Integrated Circuit (I <sup>2</sup> C)                    | 204 |

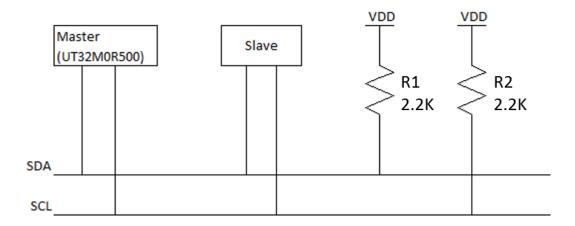

| 23.1 | Over  | view                                                     | 204 |

| 23.2 | Oper  | ration                                                   | 205 |

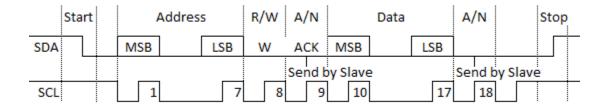

| 23.3 | I2C I | Protocol                                                 | 206 |

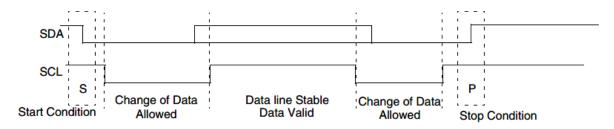

| 23.3 | 3.1   | Start and Stop Conditions                                | 206 |

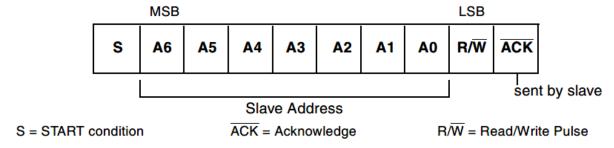

| 23.3 | 3.2   | 7-bit Addressing                                         | 206 |

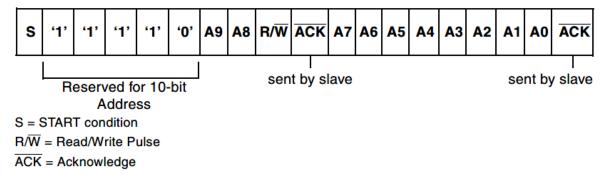

| 23.3 | 3.3   | 10-Bit Addressing                                        | 207 |

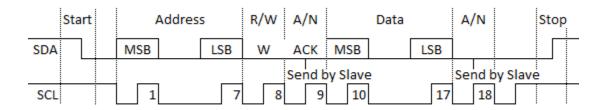

| 23.3 | 3.4   | Master to Slave Transmission                             | 207 |

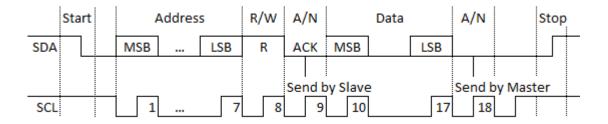

| 23.3 | 3.5   | Slave to Master Transmission                             | 208 |

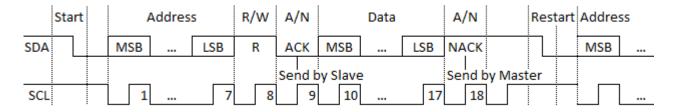

| 23.3 | 3.6   | Master to Multiple Slaves Transmission                   | 208 |

| 23.4 | Clocl | k Generation                                             | 209 |

| 23.4 | 1.1   | PCLK Frequency Configuration                             | 209 |

| 23.4 | 1.2   | Minimum High and Low Counts in SS, FS and FM+ Modes      | 210 |

| 23.4 | 1.3   | Minimum PCLK Frequency                                   | 211 |

| 23.4 | 1.4   | Standard Mode 100Kbps Baud-rate Generation               | 212 |

| 23.4 | 15    |                                                          | 212 |

|      | r.J   | Fast Speed Mode 400Kbps Baud-rate Generation             | 212 |

| 23.5  | SDA   | Hold Time                                                               | 213 |

|-------|-------|-------------------------------------------------------------------------|-----|

| 23.5  | 5.1   | SDA Hold Timings in Receiver                                            | 213 |

| 23.5  | 5.2   | SDA Hold Timings in Transmitter                                         | 214 |

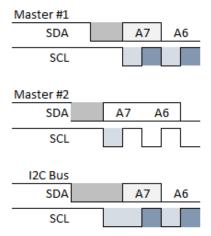

| 23.6  | Synd  | chronization                                                            | 215 |

| 23.6  | 5.1   | Clock Synchronization                                                   | 215 |

| 23.6  | 5.2   | Data Arbitration                                                        | 215 |

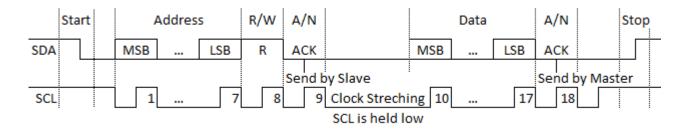

| 23.6  | 5.3   | Clock Stretching                                                        | 215 |

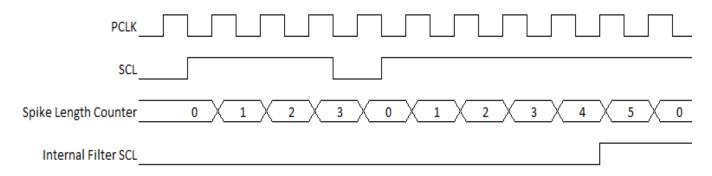

| 23.7  | Spik  | e Suppression                                                           | 216 |

| 23.8  | Exte  | rnal Interrupt                                                          | 217 |

| 23.9  | FIFC  | Empty Interrupt                                                         | 217 |

| 23.10 | F)    | [FO Full Interrupt                                                      | 217 |

| 23.11 | F)    | IFO Overrun Interrupt                                                   | 217 |

| 23.12 | I2    | 2C Register Details                                                     | 218 |

| 23.1  | 12.1  | Control Register (CON)                                                  | 220 |

| 23.1  | 12.2  | Target Address Register (TAR)                                           | 223 |

| 23.1  | 12.3  | Slave Address Register (SAR)                                            | 224 |

| 23.1  | 12.4  | Data Command Register (DATA_CMD)                                        | 225 |

| 23.1  | 12.5  | Standard Speed Clock SCL High Count Register (SS_SCL_HCNT)              | 227 |

| 23.1  | 12.6  | Standard Speed Clock SCL Low Count Register (SS_SCL_LCNT)               | 228 |

| 23.1  | 12.7  | Fast Mode or Fast Mode Plus Clock SCL High Count Register (FS_SCL_HCNT) | 229 |

| 23.1  | 12.8  | Fast Mode or Fast Mode Plus Clock SCL Low Count Register (FS_SCL_LCNT)  | 230 |

| 23.1  | 12.9  | Interrupt Status Register (INTR_STAT)                                   | 231 |

| 23.1  | 12.10 | Interrupt Mask Register (INTR_MASK)                                     | 232 |

| 23.1  | 12.11 | Raw Interrupt Status Register (RAW_INTR_STAT)                           | 233 |

| 23.1  | 12.12 | Receive FIFO Threshold Register (RX_TL)                                 | 236 |

| 23.1  | 12.13 | Transmit FIFO Threshold Register (TX_TL)                                | 237 |

| 23.1  | 12.14 | Clear Combined and Individual Interrupt Register (CLR_INTR)             | 238 |

| 23.1  | 12.15 | Clear RX_UNDER Interrupt Register (CLR_RX_UNDER)                        | 238 |

| 23.1  | 12.16 | Clear RX_OVER Interrupt Register (CLR_RX_UNDER)                         | 239 |

| 23.1  | 12.17 | Clear TX_OVER Interrupt Register (CLR_TX_OVER)                          | 239 |

| 23.1  | 12.18 | Clear RD_REQ Interrupt Register (CLR_RD_REQ)                            | 240 |

| 23.1  | 12.19 | Clear TX_ABRT Interrupt Register (CLR_TX_ABRT)                          | 240 |

| 23.1  | 12.20 | Clear RX_DONE Interrupt Register (CLR_RX_DONE)                          | 241 |

| 23.1  | 12.21 | Clear ACTIVITY Interrupt Register (CLR_ACTIVITY )                       | 241 |

| 23.1  | 12.22 | Clear STOP_DET Interrupt Register (CLR_STOP_DET)                        | 242 |

| 23.1  | 12.23 | Clear START DET Interrupt Register (CLR START DET)                      | 242 |

| 23.12.24   | Clear GEN_CALL Interrupt Register (CLR_GEN_CALL)                                                                     | . 243         |

|------------|----------------------------------------------------------------------------------------------------------------------|---------------|

| 23.12.25   | Enable Register (ENABLE)                                                                                             | . 244         |

| 23.12.26   | Status Register (STATUS)                                                                                             | . 246         |

| 23.12.27   | Transmit FIFO Level Register (TXFLR)                                                                                 | . 247         |

| 23.12.28   | Receive FIFO Level Register (RXFLR)                                                                                  | . 247         |

| 23.12.29   | SDA Hold Time Length Register (SDA_HOLD)                                                                             | . 248         |

| 23.12.30   | Transmit Abort Source Register (TX_ABORT_SOURCE)                                                                     | . 249         |

| 23.12.31   | Generate Slave Data NACK Register (SLV_DATA_NACK_ONLY)                                                               | . 251         |

| 23.12.32   | SDA Setup Register (SDA_SETUP)                                                                                       | . 252         |

| 23.12.33   | ACK General Call Register (ACK_GENERAL_CALL)                                                                         | 253           |

| 23.12.34   | Enable Status Register (ENABLE_STATUS)                                                                               | . 254         |

| 23.12.35   | SS and FS Spike Suppression Limit Register (FS_SPKLEN)                                                               | . 256         |

| 23.12.36   | HS Spike Suppression Limit Register (HS_SPKLEN)                                                                      | . 257         |

| 23.12.37   | Clear RESTART_DET Interrupt Register (CLR_RESTART_DET)                                                               | . 257         |

| 23.12.38   | Component Parameter Register 1 (COMP_PARAM_1)                                                                        | . 258         |

| 23.12.39   | Component Version Register (COMP_VERSION)                                                                            | . 259         |

| 23.12.40   | Component Type Register (COMP_TYPE)                                                                                  | . 259         |

| Contro     | oller Area Network (CAN-2.0)                                                                                         | 260           |

| 24.1 Ove   | rview                                                                                                                | . 260         |

| 24.2 Basi  | cCAN Mode of Operation                                                                                               | . 261         |

| 24.2.1     | BasiCAN Register Listing                                                                                             | . 261         |

| 24.2.2     | Control Register (CONTROL)                                                                                           | 262           |

| 24.2.3     | Command Register (COMMAND)                                                                                           | 263           |

| 24.2.4     | Status Register (STATUS)                                                                                             | . 264         |

| 24.2.5     | Interrupt Register (INTERRUPT)                                                                                       | . 265         |

| 24.2.6     | Transmit Buffer Layout                                                                                               | . 266         |

| 24.2.7     | Receive Buffer Layout                                                                                                | . 266         |

| 24.2.8     | Acceptance Filter                                                                                                    | . 266         |

| 24.2.9     | ACCEPTANCE CODE Register (ACCEPT_CODE)                                                                               | . 267         |

| 24.2.10    | ACCEPTANCE MASK Register (ACCEPT_MASK)                                                                               | . 267         |

| 24.4 PeliC | CAN Mode of Operation                                                                                                | . 268         |

| 24.4.1     | PeliCAN Register Listing                                                                                             | . 268         |

| 24.4.2     | Mode Register (MODE)                                                                                                 | . 269         |

| 24.4.3     | Command Register (COMMAND)                                                                                           | . 270         |

| 24.4.4     | Status Register (STATUS)                                                                                             | . 271         |

| 24.4.5     | Interrupt Register (INTERRUPT)                                                                                       | 272           |

|            | 23.12.25 23.12.27 23.12.28 23.12.29 23.12.30 23.12.31 23.12.32 23.12.33 23.12.36 23.12.37 23.12.38 23.12.39 23.12.40 | 14.1 Overview |

| 24.4.          | 6      | Interrupt Enable Register (INTERRUPT_ENABLE)                                                           | . 273 |

|----------------|--------|--------------------------------------------------------------------------------------------------------|-------|

| 24.4.          | 7      | Arbitration Lost Capture Register (ARB_LOST_CAPTURE)                                                   | . 274 |

| 24.4.          | 8      | Error Code Capture Register (ERROR_CODE_CAPTURE)                                                       | . 276 |

| 24.4.          | 9      | Error Warning Limit Register (ERROR_WARNING_LIMIT)                                                     | . 278 |

| 24.4.          | 10     | RX Error Counter Register (RX_ERROR_COUNTER)                                                           | . 278 |

| 24.4.          | 11     | TX Error Counter Register (TX_ERROR_COUNTER)                                                           | . 278 |

| 24.4.          | 12     | Transmit Buffer                                                                                        | . 279 |

| 24.4.          | 13     | Receive Buffer                                                                                         | . 282 |

| 24.4.<br>PELI_ |        | Acceptance Filter (PELI_CAN_ACCEPT_ACCEPT_CODE_0: ACCEPT_CODE_3, _ACCEPT.ACCEPT_MASK_0: ACCEPT_MASK_3) | . 285 |

| 24.4.          | 15     | RX Message Counter (RMC)                                                                               | . 286 |

| 24.5           | Com    | mon Registers                                                                                          | . 287 |

| 24.5.          | 1      | Clock Divider Register (CLOCK_DIVIDER)                                                                 | . 287 |

| 24.5.          | 2      | BUS TIMING 0 Register (BUS_TIMING_0)                                                                   | . 287 |

| 24.5.          | 3      | BUS TIMING 1 Register (BUS_TIMING_1)                                                                   | . 288 |

| 24.6           | Func   | tion Differences for Design                                                                            | . 289 |

| 24.6.          | 1      | SJA1000 Functional Differences                                                                         | . 289 |

| 24.6.          | 2      | BasicCAN Functional Differences                                                                        | . 289 |

| 24.6.          | 3      | PeliCAN Functional Differences                                                                         | . 289 |

| ppendi         | x A:   | Errata                                                                                                 | 290   |

| ADC Co         | ntinu  | ous Mode Wrap Around Hardware Inaccurate Delay                                                         | . 290 |

| Work           | arou   | nds                                                                                                    | . 290 |

| ADC Ext        | terna  | al vs Internal Oscillator CONV_COMPL Conflict                                                          | . 290 |

| Work           | arou   | nds                                                                                                    | . 290 |

| ADC CC         | 013_0  | OVER Low Voltage False Flag                                                                            | . 290 |

| Work           | arou   | nds                                                                                                    | . 291 |

| ADC Sir        | ngle-l | Ended Even/Odd Channel Offset Error                                                                    | . 291 |

| Work           | arou   | nds                                                                                                    | . 291 |

| I2C RD         | _REQ   | Interrupt Re-Asserts Itself After a Slave Address Register Change                                      | . 291 |

| Work           | arou   | nds                                                                                                    | . 291 |

| evision        | Hie    | tory                                                                                                   | 292   |

#### 1 INTRODUCTION

#### 1.1 Scope

This document provides information for application and system-level software development for the UT32M0R500 32-bit ARM Cortex M0+ microcontroller.

Chapter 2-8 give an introduction and overview of the Cortex M0+ processor, which the UT32M0R500 microcontroller is based on. Chapter 9 and 10 deal with SRAM and FLASH memory respectively. Chapter 11 provides information about the ARM Keil MDK. Chapter 12 deals with the bootloader configuration. Chapter 13 deals with GPIO's. Chapter 14-16 deal with analog signals. Chapter 17-20 deal with analog signals. Chapter 21-24 deal with serial communication, and Appendix A: Errata has the known bugs.

#### 1.2 Related Resources

Arm Cortex M0+ Technical Reference Manual, available at <a href="www.arm.com">www.arm.com</a>

ARMv6-M Architecture Reference Manual, available at <a href="www.arm.com">www.arm.com</a>

ARM Cortex M0+ Generic User Guide, available at <a href="www.arm.com">www.arm.com</a>

UT32M0R500 Datasheet, available at <a href="www.cobhamaes.com/HiRel">www.cobhamaes.com/HiRel</a>

#### 1.3 Architecture

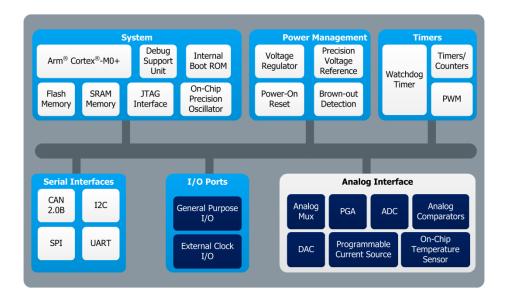

The UT32M0R500 contains the following components:

- ARM Cortex M0+

- Two CAN 2.0B Interfaces

- JTAG Debug Interface

- Forty-Eight General Purpose I/O Ports

- One 16-channel Analog-to-Digital Converters

- Two Digital-to-Analog Converters

- Watchdog Timer

- SPI Master Interface

- Two UART Interfaces

- Nor Flash Controller

- Two High-Speed Comparators

- Two I2C Interfaces

- Three Pulse Width Modulators, supporting 3 single-ended or 2 differential PWM outputs

- Four 32-bit Timers

- Real Time Clock

- AHB-to-SRAM Module

- Precision Current Source

- On-Chip Temperature Sensor

The following is a block diagram of the UT32M0R500:

#### 1.4 Features

Table 1.1: UT32M0R500 Features

| Features                         | ARM M0+ Configurable Option | UT32M0R500 Configuration |

|----------------------------------|-----------------------------|--------------------------|

| Interrupts                       | 0 – 32                      | 32                       |

| Data Endianness                  | Little-endian or big-endian | Little-endian            |

| SysTick Timer                    | Present or absent           | Present                  |

| Number of Watchpoint Comparators | 0, 1, 2                     | 2                        |

| Number of Breakpoint Comparators | 0 - 4                       | 4                        |

| Multiplier                       | Fast or small               | Fast (Single Cycle)      |

| Wakeup Interrupt Controller      | Supported or not supported  | Supported                |

| Vector Table offset Register     | Present or absent           | Present                  |

| Unprivileged/Privileged Support  | Present or absent           | Present                  |

| Memory Protection Unit           | Present or absent           | Present                  |

| Reset All Registers              | Present or absent           | Present                  |

| Debug Configuration              | Present or absent           | Present                  |

| Micro Trace Buffer               | Present or absent           | Present                  |

## **1.5 Generic Register Format**

[11...1]

Reset

This manual uses the following register format.

REGISTER NAME Offset = 0x0000

| Bit#  | 31 | 30    | 29    | 28  | 27   | 26                 | 25     | 24   | 23    | 22                   | 21 | 20    | 19    | 18 | 17 | 16 |

|-------|----|-------|-------|-----|------|--------------------|--------|------|-------|----------------------|----|-------|-------|----|----|----|

| R     |    |       |       |     | DVD. | TTAL I             | DEC [1 | 0.71 |       |                      | RE | AD_OI | NLY_R | EG |    |    |

| W     |    |       |       |     | PAR  | PARTIAL_REG [10:7] |        |      |       |                      |    |       |       |    |    |    |

| Reset |    | [00.  | 0]    |     | 0xD  |                    |        |      | [000] |                      |    |       |       |    |    |    |

|       |    |       |       |     |      |                    |        |      |       |                      |    |       |       |    |    |    |

| Bit#  | 15 | 14    | 13    | 12  | 11   | 10                 | 9      | 8    | 7     | 6                    | 5  | 4     | 3     | 2  | 1  | 0  |

| R     |    |       |       |     | DE   | DEAD WRITE DEC     |        |      | AR    | AD DARTIAL DEC [6:0] |    |       |       |    |    |    |

| W     | WR | ITE_O | NLY_F | REG | KL/  | READ_WRITE_REG     |        |      | AK    | PARTIAL_REG [6:0]    |    |       |       |    |    |    |

Legend: Bit# = Register bit number; R = Read; W = Write; Reset = Value after reset

0x3

**Table 1.2: Description of an Example Register**

| Table 1.2. Description of an Example Register |                             |                |                                                                                                                                                        |  |  |  |

|-----------------------------------------------|-----------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT<br>NUMBER(S)                              | BIT NAME                    | RESET<br>STATE | DESCRIPTION                                                                                                                                            |  |  |  |

| 31-24                                         | RESERVED                    | [000]          | RESERVED bits. Must be kept at reset value                                                                                                             |  |  |  |

| 27-24                                         | PARTIAL_REG<br>[10:7]       | 0xD            | Partial Register. Relevant bits are specified in the register name.                                                                                    |  |  |  |

| 23-16                                         | READ_ONLY<br>_REG           | [000]          | Read-Only Register. Software can only read these bits. [000] = 0x00 = 0b0000_0000                                                                      |  |  |  |

| 15-12                                         | WRITE_ONLY<br>_REG          | [111]          | Write-Only Register. Software can only write to these bits. $[111] = 0xF = 0b1111$                                                                     |  |  |  |

| 11-8                                          | READ_WRITE<br>_REG          | 0x3            | Read and Write Register. Software can read and write to these bits.                                                                                    |  |  |  |

| 7                                             | ABBREVIATED<br>_REG<br>(AR) | 1              | Abbreviated Register (Abbreviated name in parenthesis)                                                                                                 |  |  |  |

| 6-0                                           | PARTIAL_REG<br>[6:0]        | 0x4F           | Partial Register. Relevant bits are specified in the register name.  0x0F = 0b100_1111 (hex values should be compared to the number of bits available) |  |  |  |

#### 2 ARM CORTEX M0+ PROCESSOR

#### 2.1 Overview

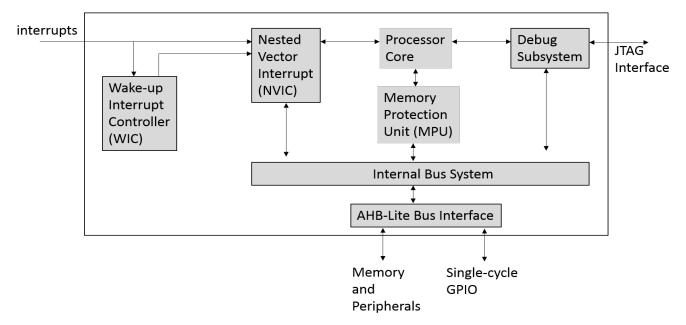

The UT32M0R500 microcontroller is based on the Arm Cortex M0+ processor. The Arm Cortex M0+ is developed based on the ARM v6-M architecture, which describes the details related to programming, including memory map, registers, instruction set architecture, and exception model. In addition to the architecture, the processor includes timing information and hardware structure. The UT32M0R500 microcontroller consists of the ARM processor core and peripheral components.

UT32M0R500 microcontroller contains the following components:

- Single core CPU optimized for power.

- On chip RAM and ROM memory components.

- Peripherals.

- Internal bus system to communicate with all microcontroller components.

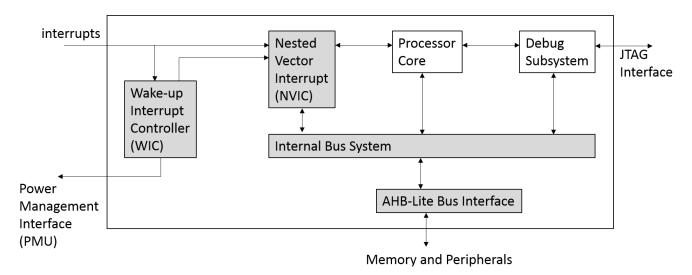

Arm Cortex M0+ processor is a von Neumann architecture containing a single bus for accessing code and data. It implements a version of the Thumb instruction set based on Thumb-2 technology, ensuring high code density and reduced program memory requirements--Thumb stands for variable length execution sets with a length of 16 or 32 bit. It implements a 2-stage pipeline. It supports up to 32 external Interrupts, each with up to 4 levels of priority that can be changed dynamically. The processor can be put into a very low-power sleep mode, leaving the Wakeup Interrupt Controller (WIC) to identify and prioritize Interrupts. It has a hardware single-cycle (32x32) multiplier and Memory Protection Unit (MPU). Figure 2.1 show a simplify block diagram of the Arm Cortex M0+.

For ARM Cortex M0+ Instruction Set, see Chapter 4 for more information.

The Arm Cortex-M0+ Memory Map describes the address space organization, see Chapter 5 for more information. For more detailed information on Arm Cortex M0+ architecture, refer to ARMv6-M Architecture Reference Manual.

Figure 2.1: Cortex M0+ Block Diagram

#### 2.2 Processor Core

The processor core contains internal registers: includes sixteen 32-bit registers for both general and special usage, the ALU, data path and control logic.

## 2.3 2-stage Pipeline

The processor is a load/store architecture. It loads data from memory to a register, processes it inside the core, and if needed, writes back to memory. All load/store always complete in program order and up to two 16-bit instructions can be fetched in one transfer

#### **2.4 NVIC**

The Nested Vector Interrupt Controller (NVIC) automatically handles nested Interrupts: compares priorities between Interrupts and the current priority level.

For more information on the NVIC, see Chapter 7.

#### **2.5 WIC**

The Wake-up Interrupt controller (WIC) masks Interrupt signals while the processor is in deep sleep. For more information on the WIC, see section 6.12.

#### 2.6 Bus Interface

The Cortex M0+ processor uses AMBA 3 AHB-Lite bus to communicate with other parts of the system, such as memory blocks, peripherals and application-specific logic. AHB-Lite is a subset of the AHB specifications, designed for single master systems with simple peripherals.

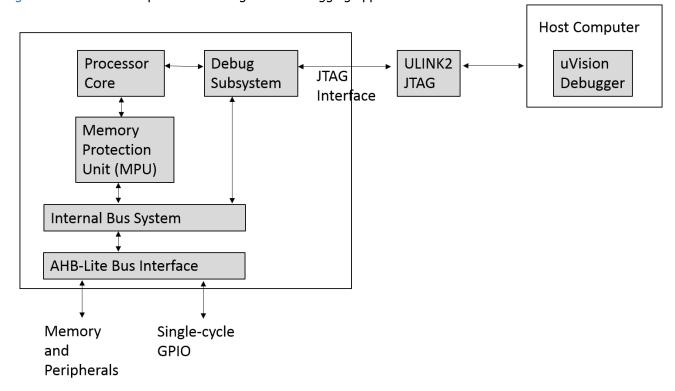

## 2.7 Debug System

The debug system provides a standard debug interface. It handles debug control, program breakpoints and data watch points. When a debug event occurs, the processor is halted and the debug subsystem allows the execution of one instruction at a time in order to analyze register values and flags. Supports unlimited software breakpoints using BKPT instruction. Non-intrusive access to core peripherals including memory.

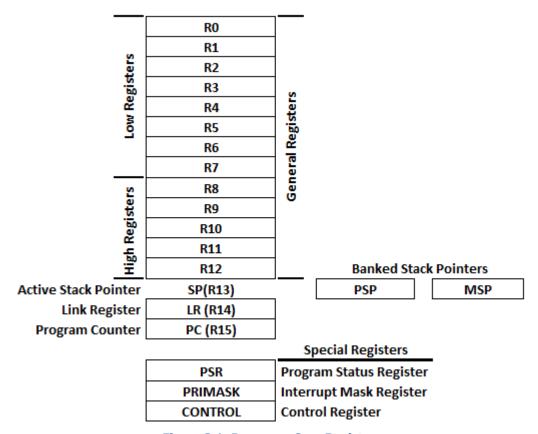

### 2.8 Cortex M0+ Registers

The processor has sixteen 32-bit generic registers: thirteen general-purpose registers (R0-R12) and several special-purpose registers a Stack Pointer (SP) R13, a Link Register (LR) R14, a Program Counter (PC) R15 and Special-purpose Program Status Registers, (xPSR)).

For more information on the Cortex M0+ registers, see Chapter 3.

For more detailed information on Arm Cortex M0+ registers, refer to ARMv6-M Architecture Reference Manual.

### 2.9 Memory Protection Unit (MPU)

The MPU can be used to make an embedded system more robust and more secure by:

- Prohibiting the user applications from corrupting data used by critical tasks (such as the operating system kernel).

- Defining the SRAM memory region as a non-executable to prevent code injection attacks.

- Changing the memory access attributes.

- Independent attribute settings for each region

- Overlapping regions

- The export of memory attributes to the system.

The MPU can be used to protect up to eight memory regions. These, in turn can have eight sub-regions, if the region is at least 256 bytes. The sub-regions are always of equal size, and can be enabled or disabled by a sub-region number. Because the minimum region size is driven by the cache line length (32 bytes), 8 sub-regions of 32 bytes correspond to a 256 bytes size.

The regions are numbered 0-7. In addition, there is another region called the default region with an id of -1. All the 0-7 memory regions take priority over the default region.

The regions can overlap, and can be nested. The region 7 has the highest priority and the region 0 has the lowest one and this governs how overlapping the regions behave. The priorities are fixed, and cannot be changed. Every region can have an access permission attribute (no accesses allowed, read-only, or read/write). Those can be further refined by fetch or no-fetch guards.

Further information on the details for accessing and using the MPU can be found at Arm Developer <u>Arm Developer Infocenter - Cortex-M0+ Devices Generic User Guide</u> and/or <u>Arm Developer Infocenter - ARMv6-M Architecture</u> Reference Manual.

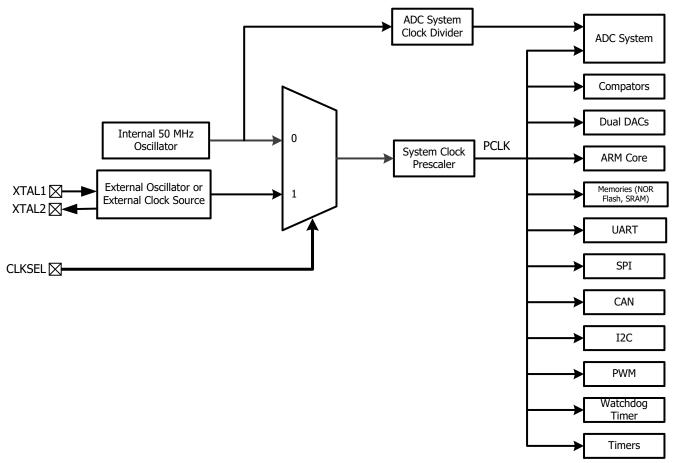

## 2.10 Clocking System

The UT32M0R500 implements a flexible clocking system that allows for using an internal or external clock source. This selection is based on the CLKSEL pin. The internal clock source is an oscillator running at a fixed frequency of 50 MHz. For the external clock source, the UT32M0R500 supports either a single-ended square wave or a crystal oscillator based input. From the clock source selection, the system clock, called PCLK, is generated. The system clock has user programmable frequency through the CLK\_DIVIDE register in the system control module (SYSCON) and drives the Arm core and all the peripherals. A notable exception is that the ADC module operates directly from the internal oscillator. Within each peripheral, there are various programmable options for changing the clock frequency for that particular peripheral.

Figure 2.2: Block diagram of UT32M0R500 clocking architecture

#### 3 ARM CORTEX M0+ REGISTERS

#### 3.1 Overview

The processor has sixteen 32-bit registers that includes thirteen general-purpose registers (R0-R12) and several special-purpose registers: R13 is the Stack Pointer (SP), R14 is the Link Register (LR), R15 is the Program Counter (PC). The Special-purpose Program Status Registers is xPSR. The exception mask register (PRIMASK) disables the handling of exceptions by the processor; it can be used for timing critical tasks. The CONTROL register controls the stack used and the privilege level for software execution when the processor is in Thread mode.

Figure 3.1 shows the Cortex M0+ registers.

**Figure 3.1: Processor Core Register**

## 3.2 Cortex M0+ General-Purpose Registers

The general-purpose registers R0-R12 have no special architecturally-defined uses.

Most instructions that can specify a general-purpose register can use R0-R12.

Low registers: R0-R7 are accessible by all instructions that specify a general-purpose register.

High registers: R8-R12 are accessible by all 32-bit instructions that specify a general-purpose register, and are not accessible by most 16-bit instructions.

#### 3.3 Stack Pointer (SP)

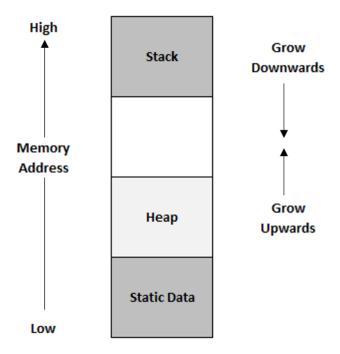

R13 is used as the Stack Pointer (SP) and it's auto aligned to a word, four-byte boundary.

Handler mode always uses the main stack pointer (MSP), but for Thread mode, it can use either process stack pointer or main stack pointer. The SP keeps track of the memory's address that holds the last value stored on the stack. It is used for saving the context of a program while switching between tasks. There are two SPs in the Cortex-M0 processor: main (MSP) and process (PSP). For simple applications, the MSP is the only stack pointer used. For applications that require privileged access, the MSP is used for OS kernel and exception handlers, while the PSP is used for other tasks.

## 3.4 Link Register (LR)

R14 is the Link Register (LR). LR is used to store the return address of a function call; the PC will load the value from the LR after a function is finished.

### 3.5 Program Counter (PC)

R15 is the Program Counter (PC). PC contains the address of the next assembly instruction to be executed. For 32-bit instruction code, the PC is automatically incremented by 4, except for branching instructions.

## 3.6 Program Status Registers (PSR)

The Program Status Register (PSR) combines mutually exclusive the Application Program Status Register (APSR), Interrupt Program Status Register (IPSR) and the Execution Program Status Register (EPSR).

- APSR contains the current state of the condition flags (N, Z, C, V) from previous instruction executions.

- IPSR contains the exception type number of the current Interrupt Service Routine (ISR).

- The EPSR contains the Thumb state bit.

### 3.7 Interrupt Mask Register (PRIMASK)

When bit [0] is set to 1, the PRIMASK register blocks the handling of exceptions by the processor, can be used to prevent data race conditions.

### 3.8 Control Register (CONTROL)

The CONTROL register controls the stack used and the privilege level for software execution when the processor is in Thread mode. After reset, the MSP is used but when using an OS, PSP can be used for Threads and MSP for OS and ISR's implementation.

#### 4 ARM CORTEX M0+ INSTRUCTION SET

#### 4.1 Overview

The Cortex-M0+ Instruction Set Architecture is developed based on the Arm v6-M architecture, which is a combination of Armv6 architecture's Thumb instruction set and Armv7-M architecture memory map, exception model, and Thumb-2 system.

Armv6-M supports the Thumb instruction set including a small number of 32-bit instructions introduced with Thumb-2 technology. The 16-bit instruction support is equivalent to the Thumb instruction set support in Armv6 prior to the introduction of Thumb-2 technology. Thumb instructions are either 16-bit or 32-bit, and are aligned on a two-byte boundary. 16-bit and 32-bit instructions can be intermixed freely.

For more detailed information on Arm Cortex M0+ Instruction Set, refer to Cortex-M0+ Devices Generic User Guide

Below is the Cortex-M0+ Instruction Set assembly syntax.

Label

Mnemonic Operand1, Operand2,...; Comments

- Labels are symbolic representations of addresses; labels are used to mark specific addresses to refer to from other parts of the code

- **Mnemonic** is the name of the instruction. Most data processing instructions can optionally update the condition flags according to the result of the operation

- **operand1** is the destination register

- Operand2 is the source register

- ";" are comments and don't affect the program

**Note:** mnemonics, pseudo-instructions, directives and symbolic register names can be written in all uppercase or all lowercase, but not mixed. Labels and comments can be in uppercase, lowercase, or mixed.

**Table 4.1: Cortex M0+ Instruction Set**

| 16-Bit Tl | 16-Bit Thumb Instructions Supported on Cortex-M0+ |      |      |      |      |      |       |      |       |

|-----------|---------------------------------------------------|------|------|------|------|------|-------|------|-------|

| ADCS      | ADDS                                              | ADR  | ANDS | ASRS | В    | BIC  | BLX   | BKPT | BX    |

| CMN       | CMP                                               | CPS  | EORS | LDM  | LDR  | LDRH | LDRSH | LDRB | LDRSB |

| LSLS      | LSRS                                              | MOV  | MVN  | MULS | NOP  | ORRS | POP   | PUSH | REV   |

| REV16     | REVSH                                             | ROR  | RSB  | SBCS | SEV  | STM  | STR   | STRH | STRB  |

| SUBS      | SVC                                               | SXTB | SXTH | TST  | UXTB | UXTH | WFE   | WFI  | YIELD |

| 32-Bit Thumb-2 Instructions Supported on Cortex-M0+ |     |     |     |     |     |  |  |  |  |

|-----------------------------------------------------|-----|-----|-----|-----|-----|--|--|--|--|

| BL                                                  | DSB | DMB | ISB | MRS | MSR |  |  |  |  |

- The special registers **Control**, **MASK** and **xPSR** are accessed using the **MRS** and **MSR** instructions.

- MRS moves the data from a special register into a general purpose register, and

- MSR moves the data from a general purpose register into a special register.

- **ISB**, **DSB**, and **DMB** are memory synchronization instructions.

- **BL** was supported in the traditional Thumb instruction set, but the bit field definition was extended in Thumb-2.

For **WFE**, **WFI** and **SEV** sleep mode instructions, see Power Management for information.

**Table 4.2: Cortex M0+ Instruction Set Categories**

| Category        | Туре             | Mnemonic                                                   |

|-----------------|------------------|------------------------------------------------------------|

| Memory Access   | Load             | LDR, LDRB, LDRH, LDRSH, LDRSB, LDM                         |

|                 | Store            | STR, STRB, STRH, STM                                       |

|                 | Stack            | PUSH, POP                                                  |

| Data movement   | Move             | MOV, MOVS, MRS, MSR                                        |

| Control flow    | Branch           | B, BL, BX, BLX, BCC                                        |

| Data processing | Math             | ADD, ADDS, ADCS, ADR, MULS, RSBS, SBCS, SUB(S)             |

|                 | Logic            | ANDS, EORS, ORRS, BICS, MVNS, TST                          |

|                 | Compare          | CMP, CMN, TST                                              |

|                 | Shift and Rotate | ASRS, LSLS, LSRS, RORS                                     |

|                 | Extend           | SXTB, SXTH, UXTB, UXTH                                     |

|                 | Reverse          | REV, REV16, REVSH                                          |

| Miscellaneous   |                  | BKPT, CPSID, CPSIE, WFE, WFI, SVC, DMB, DSB, ISB, SEV, NOP |

## 4.2 Memory Access: LOAD

| Syntax                                | Example            | Description                                      |

|---------------------------------------|--------------------|--------------------------------------------------|

| LDR <rt>,=Direct Number</rt>          | LDR R0,=0x01234567 | R0=0x01234567                                    |

| LDR <rt>,[<rn>,Constant]</rn></rt>    | LDR R0,[R1,4]      | R0=memory[R1+4], load word from mem              |

| LDR <rt>,[<rn>,<rm>]</rm></rn></rt>   | LDR R0,[R1,R2]     | R0=memory[R1+R2], load word from mem             |

| LDRH <rt>,[<rn>,<rm>]</rm></rn></rt>  | LDRH R0,[R1,R2]    | R0=memory[R1+R2], load signed half word from mem |

| LDRB <rt>,[<rn>,<rm>]</rm></rn></rt>  | LDRB R0,[R1,R2]    | R0=memory[R1+R2], load signed byte word from mem |

| LDRSH <rt>,[<rn>,<rm>]</rm></rn></rt> | LDRSH R0,[R1,R2]   | R0=memory[R1+R2], load word from mem             |

| LDRSB <rt>,[<rn>,<rm>]</rm></rn></rt> | LDRSB R0,[R1,R2]   | R0=memory[R1+R2], load word from mem             |

## 4.3 Memory Access: STORE

| Syntax                               | Example         | Description                              |

|--------------------------------------|-----------------|------------------------------------------|

| STR <rt>,[<rn>,<rm>]</rm></rn></rt>  | STR R0,[R1,R2]  | memory[R1+R2]=R0, write word to mem      |

| STRH <rt>,[<rn>,<rm>]</rm></rn></rt> | STRH R0,[R1,R2] | memory[R1+R2]=R0, write half word to mem |

| STRB <rt>,[<rn>,<rm>]</rm></rn></rt> | STRB R0,[R1,R2] | memory[R1+R2]=R0, write a byte to mem    |

## **4.4 Multiple Data Access**

| Syntax                                | Example             | Description                                                            |

|---------------------------------------|---------------------|------------------------------------------------------------------------|

| LDM <rn>,{<ra>,<rb>}</rb></ra></rn>   | LDM R0,{R1,R2-R7}   | R1=memory[R0] R2=memory[R0+4]                                          |

| LDMIA <rn>,{<ra>,<rb>}</rb></ra></rn> | LDMIA R0,{R1,R2-R7} | R1=memory[R0], load multiple and inc last address + 4 R2=memory[R0+4]  |

| STMIA <rn>,{<ra>,<rb>}</rb></ra></rn> | STMIA R0,{R1,R2-R7} | R1=memory[R0], store multiple and inc last address + 4 R2=memory[R0+4] |

### 4.5 Stack Access: PUSH and POP

| Syntax                      | Example          | Description                                                           |

|-----------------------------|------------------|-----------------------------------------------------------------------|

| PUSH { <ra>,<rb>}</rb></ra> | PUSH {R0,R1, R2} | Memory[SP-4]=R0,<br>Memory[SP-8]=R1,<br>Memory[SP-12]=R2,<br>SP=SP-12 |

| POP { <ra>,<rb>}</rb></ra>  | POP {R0,R1, R2}  | R2= Memory[SP],<br>R1= Memory[SP+4],<br>R0= Memory[SP+8],<br>SP=SP+12 |

#### 4.6 Arithmetic ADD

| Syntax                             | Example          | Description                    |

|------------------------------------|------------------|--------------------------------|

| ADDS <rd>,<rn>,<rm></rm></rn></rd> | ADDS R0,R1,R2    | R0= R1+R2, update APSR         |

| ADDS <rd>,<rn>,#imm</rn></rd>      | ADDS R0,R1,#0x2  | R0= R1+2, update APSR          |

| ADDS <rd>,#imm</rd>                | ADDS R0,#0x2     | R0= R0+2, update APSR          |

| ADD <rd>,<rn></rn></rd>            | ADDS R0,R1       | R0= R1+R2                      |

| ADDC <rd>,<rm></rm></rd>           | ADDS R0,R1       | R0= R1+R2 + carry, update APSR |

| ADDS <rd>,PC,#imm</rd>             | ADDS R0,PC,#0x04 | R0= PC+4                       |

## 4.7 Arithmetic SUB, MUL

| Syntax                             | Example         | Description                     |

|------------------------------------|-----------------|---------------------------------|

| SUBS <rd>,<rn>,<rm></rm></rn></rd> | SUBS R0,R1,R2   | R0= R1-R2, update APSR          |

| SUBS <rd>,<rn>,#imm</rn></rd>      | SUBS R0,R1,#0x2 | R0= R1-2, update APSR           |

| SUBS <rd>,#imm</rd>                | SUBS R0,#0x2    | R0= R0-2, update APSR           |

| SBCS <rd>,<rd>,<rm></rm></rd></rd> | SBCS R0,R0,R1   | R0= R0-R1 - Borrow, update APSR |

| RSBS <rd>,<rd>,#0</rd></rd>        | RSBS R0,R0,#0   | R0= -R0                         |

| MULS <rd>,<rm>,<rd></rd></rm></rd> | MULS R0,R1,R0   | R0=R0*R1                        |

## 4.8 Arithmetic CMP

| Syntax                  | Example     | Description        |

|-------------------------|-------------|--------------------|

| CMP <rn>,<rm></rm></rn> | CMP R0,R1   | R0-R1, update APSR |

| CMP <rn>,#imm</rn>      | CMP R0,#0x1 | R0-1, update APSR  |

| CMN <rn>,<rm></rm></rn> | CMN R0,R1   | R0+R1, update APSR |

## 4.9 Logic Operations

| Syntax                   | Example    | Description                   |

|--------------------------|------------|-------------------------------|

| ANDS <rd>,<rm></rm></rd> | ANDS R0,R1 | update APSR                   |

| ORRS <rd>,<rm></rm></rd> | ORRS R0,R1 | update APSR                   |

| EORS <rd>,<rm></rm></rd> | EORS R0,R1 | XOR(R0,R1), update APSR       |

| MVNS <rd>,<rm></rm></rd> | MVNS R0,R1 | R0=NOT(R1), update APSR       |

| BICS <rd>,<rm></rm></rd> | BICS R0,R1 | AND(R0, NOT(R1)), update APSR |

| TST <rd>,<rm></rm></rd>  | TST R0,R1  | AND(R0, R1), update APSR      |

## **4.10 Arithmetic Shift Operation**

| Syntax                       | Example         | Description            |  |

|------------------------------|-----------------|------------------------|--|

| ASRS <rd>,<rm></rm></rd>     | ASRS R0,R1      | R0=R0>>R1, update APSR |  |

| ASRS <rd>,<rm>#imm</rm></rd> | ASRS R0,R1,#0x1 | R0=R1>>1, update APSR  |  |

## 4.11 Logic Shift Operation

| Syntax                       | Example         | Description                                 |

|------------------------------|-----------------|---------------------------------------------|

| LSRS <rd>,<rm></rm></rd>     | LSRS R0,R1      | R0=R0>>R1, update APSR                      |

| LSRS <rd>,<rm>#imm</rm></rd> | LSRS R0,R1,#0x1 | R0=R1>>1, update APSR                       |

| LSLS <rd>,<rm></rm></rd>     | LSLS R0,R1      | R0=R0< <r1, apsr<="" td="" update=""></r1,> |

| LSLS <rd>,<rm>#imm</rm></rd> | ASRS R0,R1,#0x1 | R0=R1<<1, update APSR                       |

## **4.12 Rotate Operation**

| Syntax                   | Example    | Description                    |

|--------------------------|------------|--------------------------------|

| RORS <rd>,<rm></rm></rd> | RORS R0,R1 | R0=R0>>R1(rotate), update APSR |

## **4.13 Reverse Ordering Operation**

| Syntax                    | Example     | Description                                        |

|---------------------------|-------------|----------------------------------------------------|

| REV <rd>,<rm></rm></rd>   | REV RO,R1   | R0={R1 [7:0], R1 [15:8] , R1 [23:16] , R1 [31:24]} |

| REV16 <rd>,<rm></rm></rd> | REV16 R0,R1 | R0={R1 [23:16], R1 [31:24], R1 [7:0], R1 [15:8]}   |

| REVSH <rd>,<rm></rm></rd> | REVSH R0,R1 | R0=signed extend{R1 [7:0], R1 [15:8]}              |

## **4.14 Extended Operation**

| Syntax                   | Example    | Description                 |

|--------------------------|------------|-----------------------------|

| SXTB <rd>,<rm></rm></rd> | SXTB R0,R1 | R0=signed extend(R1 [7:0])  |

| SXTH <rd>,<rm></rm></rd> | SXTH R0,R1 | R0=signed extend(R1 [15:0]) |

| UXTB <rd>,<rm></rm></rd> | UXTB R0,R1 | R0=zero extend(R1 [7:0])    |

| UXTH <rd>,<rm></rm></rd> | UXTH R0,R1 | R0=zero extend(R1 [15:0])   |

## **4.15 Program Flow Control**

| Syntax                         | Example     | Description                           |

|--------------------------------|-------------|---------------------------------------|

| B <label></label>              | B loop      | Change PC to loop                     |

| B <cond><label></label></cond> | BEQ loop    | If Z=1 in APSR reg, change PC to loop |

| BL <label></label>             | BL function | Change PC to function, LR = PC+4      |

| BX <rm></rm>                   | BX R0       | PC = R0                               |

| BLX                            | BLX R0      | PC = R0, LR = PC+4                    |

#### 5 ARM CORTEX MO+ MEMORY MAP

#### 5.1 Overview

The Arm Cortex-M0+ Memory Map describes the organization of the processor's address space. The address space contains internal and external RAM and ROM as well as buses and peripherals. The total memory space of a 32-bit system is 4GB. It is split and separated into regions with different functionality which can be individually changed, except for internal private peripheral bus of the processor.

The processor stores 8-bit bytes, 16-bit half words or 32-bit words, so a particular memory address specifies a particular byte in memory, and in order to get a byte from memory, the processor accesses the next three-byte addresses to get a full 32-bit word.

Figure 5.1 shows the predefined regions within the memory map of the UT32M0R500 microcontroller.

|             |                 | 1                            |

|-------------|-----------------|------------------------------|

| 0xE010_0000 | System          | System ROM, MTB, etc.        |

|             | Private         | NVIC, SCS, etc.              |

| 0xE000_0000 | Peripheral Bus  | NVIC, 3C3, etc.              |

|             | Reserved        |                              |

| 0x4002_0000 | AHB Peripherals | On-chip peripherals          |

| 0x4000_0000 | APB Peripherals | on emp peripherus            |

|             | Reserved        |                              |

| 0x2000_0000 | SRAM            | 96KB of progam code and data |

|             | Reserved        |                              |

| 0x0100_0000 | NOR Flash       | NOR Flash 64KB window        |

|             | Reserved        |                              |

| 0x0000_0000 | Boot ROM        | 32KB Boot ROM                |

Figure 5.1: UT32M0R500 Memory Map

Table 5.1 and Table 5.2 specify the predefined regions for the different peripherals with boundary addresses.

**Table 5.1. AHB Memory Map Table**

| Address Range             | Size<br>(bytes) | UT32M0R500 Peripheral                              | Description                                    |

|---------------------------|-----------------|----------------------------------------------------|------------------------------------------------|

| 0x0000 0000 - 0x0000 7FFF | 32K             | Boot ROM                                           | See 5.2 Boot ROM for info                      |

| 0x0100 0000 - 0x0100 FFFF | 64K             | NOR Flash                                          | See section 5.2 and chapter 18 for info        |

| 0x2000 0000 - 0x2001 7FFF | 96K             | SRAM                                               | See section 5.3 Embedded SRAM for more info    |

| 0x4000 0000 - 0x4001 FFFF | 128K            | APB Peripherals                                    | See Table 5.2                                  |

| 0x4002 0000 - 0x4002 0FFF | 4K              | AHB GPIO Bank 0                                    | See Table 12.2 and Table 12.3 for register map |

| 0x4002 1000 - 0x4002 1FFF | 4K              | AHB GPIO Bank 1                                    | See Table 12.2 and Table 12.3 for register map |

| 0x4002 2000 - 0x4002 2FFF | 4K              | AHB GPIO Bank 2                                    | See Table 12.2 and Table 12.3 for register map |

| 0x4002 3000 - 0x4002 3FFF | 4K              | AHB CAN 0                                          | See Table 24.1 for register map                |

| 0x4002 4000 - 0x4002 4FFF | 4K              | AHB CAN 1                                          | See Table 24.1 for register map                |

| 0x4002 0000 - 0x4002 FFFF | 4K              | System Controller                                  | See Table 8.1 for register map                 |

| 0xE000 0000 - 0xE00F FFFF | 4K              | Private peripheral bus addresses in the Cortex-M0+ | See CMSIS section 6.11 for info                |

| 0xF000 0000 - 0xF000 0FFF | 4K              | System ROM                                         | See CoresSight-MTB-M+ for more info            |

| 0xF020 0000 - 0xF020 0FFF | 4K              | MTB SFR                                            | See CoresSight-MTB-M+ for more info            |

| 0xF021 0000 - 0xF021 FFFF | 64K             | 4kB MTB SRAM                                       | See CoresSight-MTB-M+ for more info            |

| 0xF022 0000 - 0xFFFF FFFF |                 | Cortex M0+                                         |                                                |

**Table 5.2. APB Peripheral Memory Map Table**

| Address Range             | Size (bytes) | UT32M0R500 Peripheral | Description                     |

|---------------------------|--------------|-----------------------|---------------------------------|

| 0x4000 0000 - 0x4000 0FFF | 4K           | RTC                   | See Table 20.1 for register map |

| 0x4000 1000 - 0x4000 1FFF | 4K           | Dual Timer0           | See Table 17.1 for register map |

| 0x4000 2000 - 0x4000 2FFF | 4K           | Dual Timer1           | See Table 17.1 for register map |

| 0x4000 3000 - 0x4000 3FFF | 4K           | PWM                   | See Table 18.5 for register map |

| 0x4000 4000 - 0x4000 4FFF | 4K           | UART0                 | See Table 21.2 for register map |

| 0x4000 5000 - 0x4000 5FFF | 4K           | UART1                 | See Table 21.2 for register map |

| 0x4000 6000 - 0x4000 6FFF | 4K           | SPI                   | See Table 22.1 for register map |

| 0x4000 7000 - 0x4000 7FFF | 4K           | DACs                  | See Table 15.1 for register map |

| 0x4000 8000 - 0x4000 8FFF | 4K           | Watchdog              | See Table 19.1 for register map |

| 0x4000 9000 - 0x4000 9FFF | 4K           | I2C0                  | See Table 23.3 for register map |

| 0x4000 A000 - 0x4000 AFFF | 4K           | I2C1                  | See Table 23.3 for register map |

| 0x4000 B000 - 0x4000 BFFF | 4K           | Trim Control          |                                 |

| 0x4000 C000 - 0x4000 CFFF | 4K           | NFC                   | See Table 10.1 for register map |

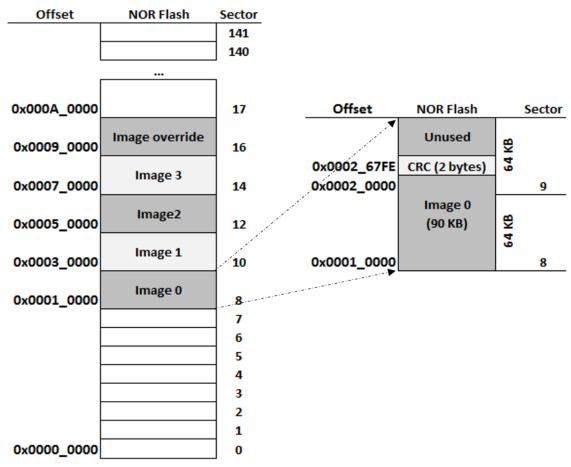

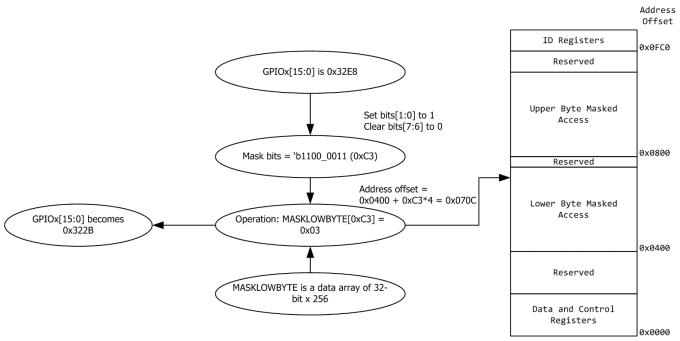

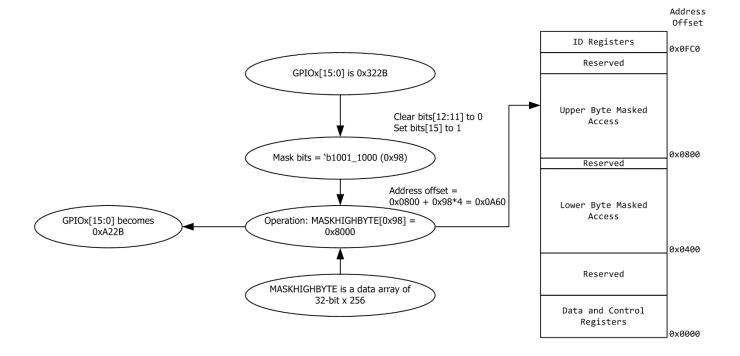

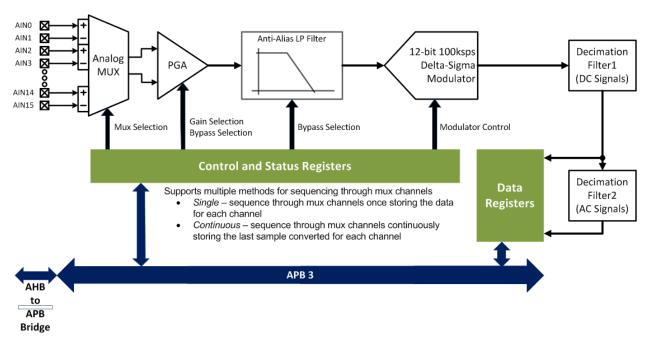

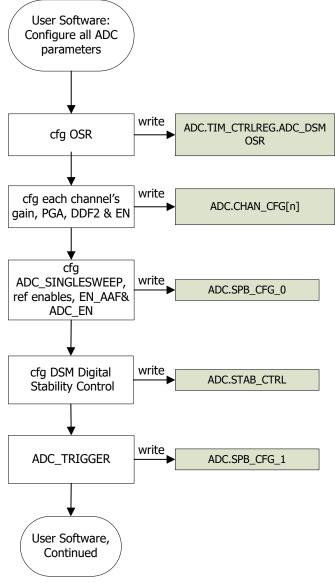

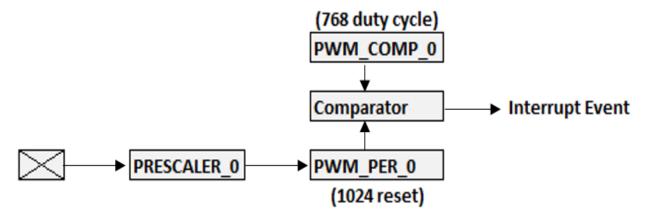

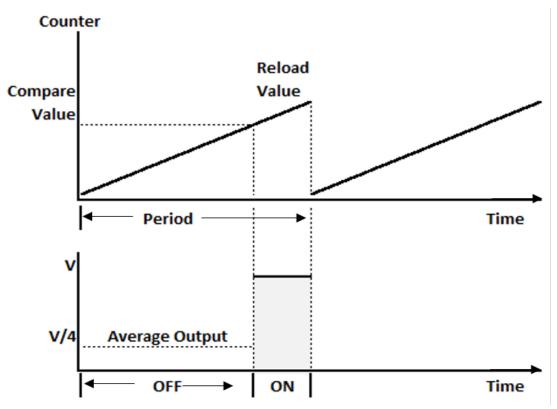

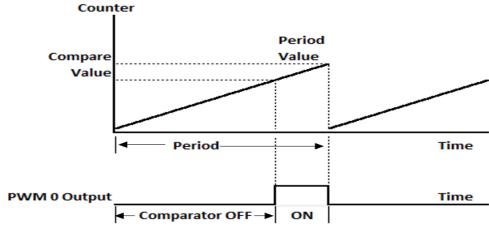

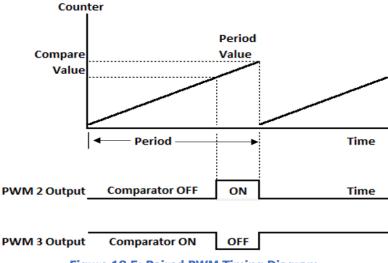

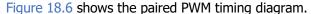

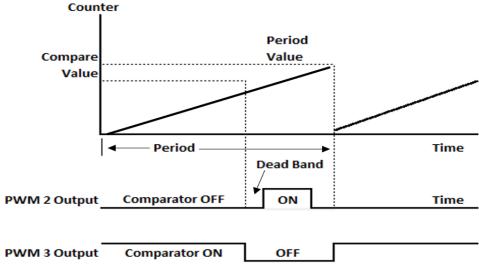

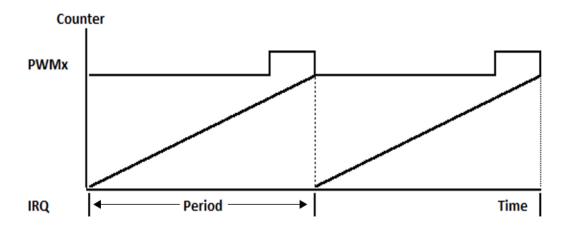

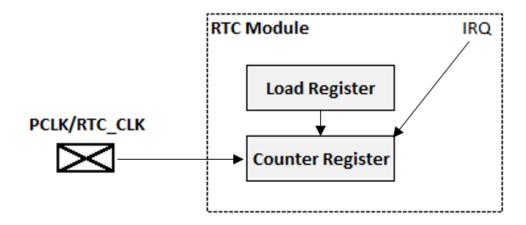

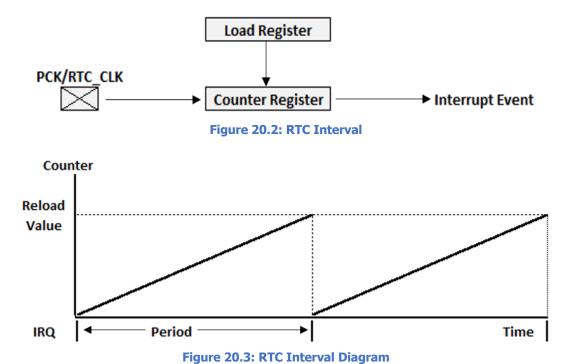

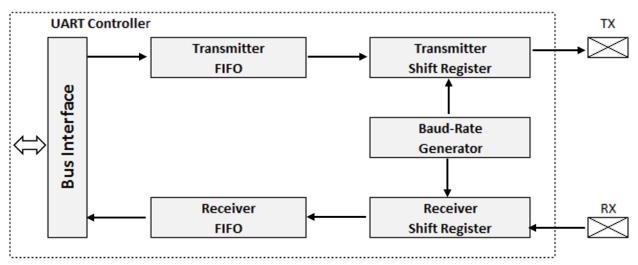

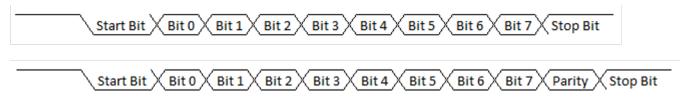

| 0x4000 D000 - 0x4000 DFFF | 4K           | SRAM EDAC/Scrub       | See Table 9.1 for register map  |