### UT7C138/139

#### **Features**

- 45ns and 55ns maximum address access time

- Asynchronous operation for compatibility with industry standard 4K x 8/9 dual-port static RAM

- CMOS compatible inputs, TTL/CMOS compatible output levels

- Three-state bidirectional data bus

- Low operating and standby current

- Radiation-hardened process and design; total dose irradiation testing to MIL-STD-883 Method 1019

- Total-dose: 1.0E6 rads(Si)

- Memory Cell LET threshold: 85 MeV-cm<sup>2</sup>/mg

- Latchup immune (LET >100 MeV-cm<sup>2</sup>/mg)

- QML Q and QML V compliant part

- Packaging options:

- 68-lead Flatpack

- 68-pin PGA

- 5-volt operation

- Standard Microcircuit Drawing 5962-96845

#### Introduction

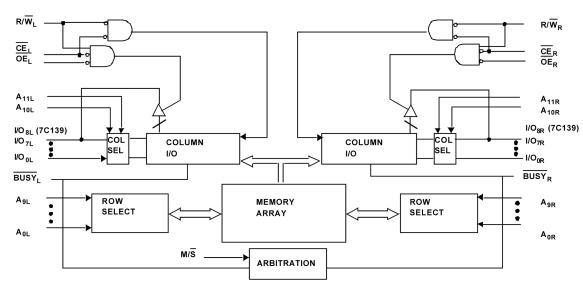

The UT7C138 and UT7C139 are high-speed radiation-hardened CMOS  $4K \times 8$  and  $4K \times 9$  dual-port static RAMs. Arbitration schemes are included on the UT7C138/139 to handle situations when multiple processors access the same memory location. Two ports provide independent, asynchronous access for reads and writes to any location in memory. The UT7C138/139 can be utilized as a stand-alone 32/36-Kbit dual-port static RAM or multiple devices can be combined in order to function as a 16/18-bit or wider master/ slave dual-port static RAM. For applications that require depth expansion, the  $\overline{BUSY}$  pin is open-collector allowing for wired OR circuit configuration. An M/ $\overline{S}$  pin is provided for implementing 16/18-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications, and status buffering.

Each port has independent control pins: chip enable  $(\overline{CE})$ , read or write enable  $(R/\overline{W})$ , and output enable  $(\overline{OE})$ .  $\overline{BUSY}$  signals that the port is trying to access the same location currently being accessed by the other port.

Figure 1. Logic Block Diagram

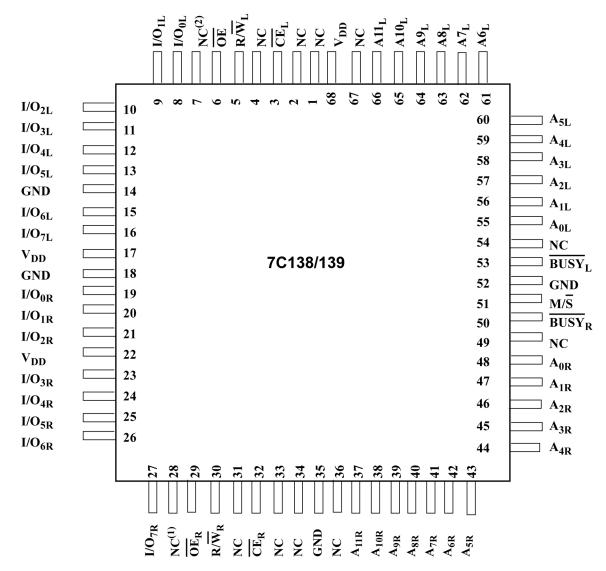

Figure 2a. DPRAM Pinout (68-Flatpack) (Top View)

- 1) I/O8R on the7C139

- 2) I/O8L on the 7C139

|    | A                                     | B                                | $\mathbf{C}$      | D                 | $\mathbf{E}$      | F                 | $\mathbf{G}$      | H                 | J                 | K                   | L                                   |

|----|---------------------------------------|----------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------------------------|

| 1  |                                       | I/O <sub>3L</sub>                | I/O <sub>5L</sub> | I/O <sub>6L</sub> | V <sub>DD</sub>   | I/O <sub>0R</sub> | I/O <sub>2R</sub> | I/O <sub>3R</sub> | I/O <sub>5R</sub> | I/O <sub>6R</sub>   |                                     |

| 1  |                                       | B1                               | C1                | D1                | E1                | F1                | G1                | H1                | J1                | K1                  |                                     |

| 2  | I/O <sub>1L</sub>                     | I/O <sub>2L</sub>                | I/O <sub>4L</sub> | GND               | I/O <sub>7L</sub> | GND               | I/O <sub>1R</sub> | V <sub>DD</sub>   | I/O <sub>4R</sub> | I/O <sub>7R</sub>   | NC <sup>(1)</sup>                   |

| 2  | A2                                    | B2                               | C2                | D2                | E2                | F2                | G2                | H2                | J2                | K2                  | L2                                  |

|    | I/O <sub>0L</sub>                     | $NC^{(2)}$                       |                   |                   |                   |                   |                   |                   |                   | $\overline{OE}_{R}$ | $R/\overline{W}_R$                  |

| 3  | A3                                    | B3                               | 1                 |                   |                   |                   |                   |                   |                   | K3                  | L3                                  |

| •  | $\overline{\mathbf{OE}}_{\mathbf{L}}$ | $R/\overline{W}_L$               |                   |                   |                   |                   |                   |                   |                   | NC                  | $\overline{\text{CE}}_{\mathbf{R}}$ |

| 4  | A4                                    | B4                               | 1                 |                   |                   |                   |                   |                   |                   | K4                  | L4                                  |

| 3  | NC                                    | $\overline{\text{CE}}_{	ext{L}}$ |                   |                   |                   |                   |                   |                   |                   | NC                  | NC                                  |

| 5  | A5                                    | B5                               | 1                 |                   |                   |                   |                   |                   |                   | K5                  | L5                                  |

| v  | NC                                    | NC                               |                   |                   | 70                | C138/13           | 39                |                   |                   | GND                 | NC                                  |

| 6  | A6                                    | B6                               | 1                 |                   |                   |                   |                   |                   |                   | K6                  | L6                                  |

| ,  | V <sub>DD</sub>                       | NC                               |                   |                   |                   |                   |                   |                   |                   | A <sub>11R</sub>    | A <sub>10R</sub>                    |

| 7  | A7                                    | B7                               | 1                 |                   |                   |                   |                   |                   |                   | K7                  | L7                                  |

| 8  | A <sub>11L</sub>                      | A <sub>10L</sub>                 |                   |                   |                   |                   |                   |                   |                   | A <sub>9R</sub>     | A <sub>8R</sub>                     |

| O  | A8                                    | B8                               | †                 |                   |                   |                   |                   |                   |                   | K8                  | L8                                  |

| 9  | A <sub>9</sub> L                      | $A_{8L}$                         |                   |                   |                   |                   |                   |                   |                   | A <sub>7R</sub>     | A <sub>6R</sub>                     |

| _  | A9                                    | B9                               | J.L               | IL                | I                 | 1                 | l K               | UK                |                   | K9                  | L9                                  |

| 10 | A <sub>7L</sub>                       | A <sub>6L</sub>                  | A <sub>3L</sub>   | A <sub>1L</sub>   | NC                | GND               | BUSYR             | $A_{0R}$          | A <sub>2R</sub>   | A <sub>4R</sub>     | A <sub>5R</sub>                     |

| 10 | A10                                   | B10                              | C10               | D10               | E10               | F10               | G10               | H10               | J10               | K10                 | L10                                 |

| 11 |                                       | $A_{5L}$                         | $A_{4L}$          | $A_{2L}$          | $A_{0L}$          | BUSYL             | $M/\overline{S}$  | NC                | $A_{1R}$          | $A_{3R}$            |                                     |

| 11 |                                       | B11                              | C11               | D11               | E11               | F11               | G11               | H11               | J11               | K11                 |                                     |

Figure 2b: DPRAM Pinout (68 PGA) (top view)

#### **Notes:**

- 1) I/O8R on the7C139

- 2) I/O8L on the 7C139

#### **Pin Names**

| Left Port                | Right Port                   | Description            |

|--------------------------|------------------------------|------------------------|

| I/O <sub>0L-7L(8L)</sub> | I/O <sub>0R-7R(8R)</sub>     | Data Bus Input/Output  |

| A <sub>0L-11L</sub>      | A <sub>0R-11R</sub>          | Address Lines          |

| CEL                      | <u>CE</u> <sub>R</sub>       | Chip Enable            |

| ŌĒL                      | $\overline{OE}_R$            | Output Enable          |

| $R/\overline{W}_L$       | $R/\overline{W}_R$           | Read/Write Enable      |

| BUSY <sub>L</sub>        | $\overline{\text{BUSY}}_{R}$ | Busy Flag Input/Output |

| M/S                      |                              | Master or Slave Select |

| $V_{DD}$                 |                              | Power                  |

| GND                      |                              | Ground                 |

### UT7C138/139

The UT7C138/139 consists of an array of 4K words of 8 or 9 bits of dual-port SRAM cells, I/O and address lines, and control signals ( $\overline{\text{CE}}$ ,  $\overline{\text{OE}}$ , R/ $\overline{\text{W}}$ ). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes/reads to the same location, a  $\overline{\text{BUSY}}$  pin is provided on each port. With the M/ $\overline{\text{S}}$  pin, the UT7C138/139 can function as a master ( $\overline{\text{BUSY}}$  pins are outputs) or as a slave ( $\overline{\text{BUSY}}$  pins are inputs). Each port is provided with its own output enable control ( $\overline{\text{OE}}$ ), which allows data to be read from the device.

### **Write Cycle**

A combination of  $R/\overline{W}$  less than  $V_{IL}$  (max), and  $\overline{CE}$  less than  $V_{IL}$  (max), defines a write cycle. The state of  $\overline{OE}$  is a "don't care" for a write cycle. The outputs are placed in the high-impedance state when either  $\overline{OE}$  is greater than  $V_{IH}$  (min), or when  $R/\overline{W}$  is less than  $V_{IL}$  (max).

### **Write Operation**

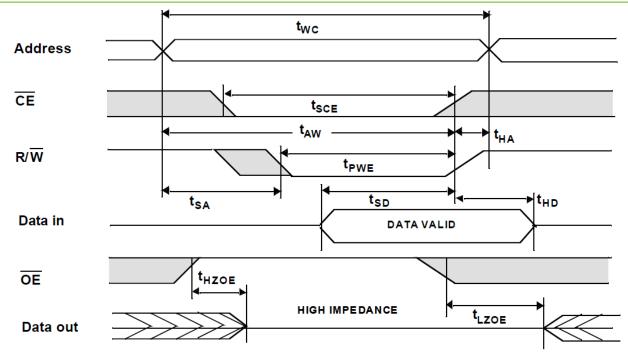

Write Cycle 1, the Write Enable-controlled Access shown in figure 4a, is defined by a write terminated by  $R/\overline{W}$  going high with  $\overline{CE}$  active. The write pulse width is defined by  $t_{PWE}$  when the write is initiated by  $R/\overline{W}$ ,, and by  $t_{SCE}$  when the write is initiated by  $\overline{CE}$  going active. Unless the outputs have been previously placed in the high-impedance state by  $\overline{OE}$ , the user must wait  $t_{HZOE}$  before applying data to the eight/nine bidirectional pins I/O (0:7/0:8) to avoid bus contention.

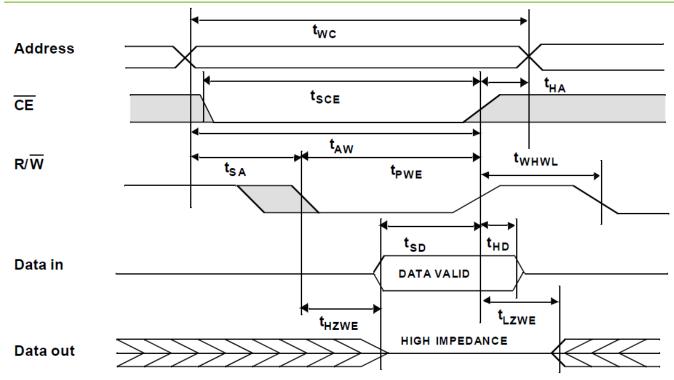

Write Cycle 2, the Chip Enable-controlled Access shown in figure 4b, is defined by a write terminated by CE going inactive. The write pulse width is defined by  $t_{PWE}$  when the write is initiated by  $R/\overline{W}$ , and by  $t_{SCE}$  when the write is initiated by  $\overline{CE}$  going active. For the  $R/\overline{W}$ , initiated write, unless the outputs have been previously placed in the high-impedance state by  $\overline{OE}$ , the user must wait  $t_{HZWE}$  before applying data to the eight/nine bidirectional pins I/O (0:7/0:8) to avoid bus contention.

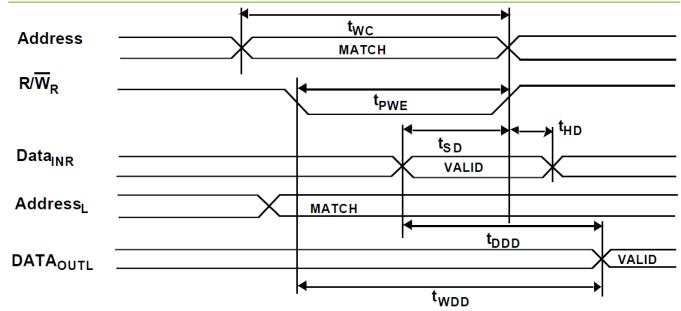

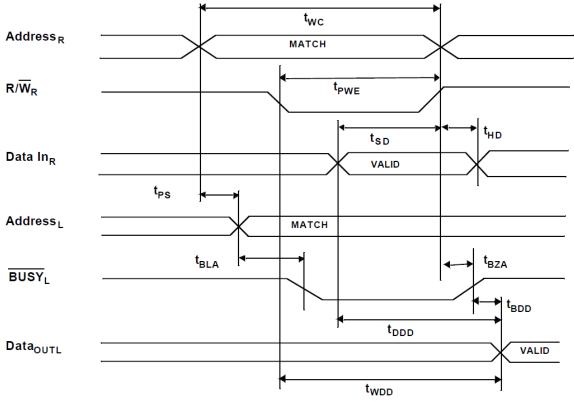

If a location is being written by one port and the opposite port attempts to read that location, a port-to-port flow through delay must be met before the data is read on the output. Data will be valid on the port wishing to read the location ( $t_{BZA} + t_{BDD}$ ) after the data is written on the other port (see figure 5a).

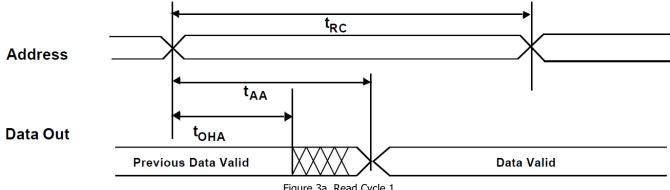

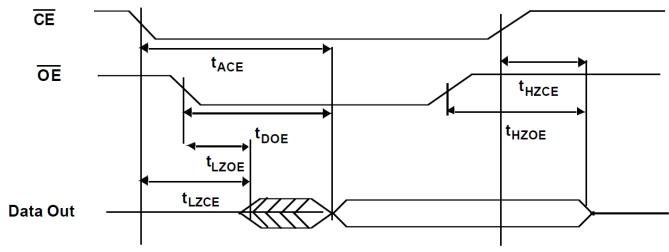

### **Read Operation**

When reading the device, the user must assert both the  $\overline{OE}$  and  $\overline{CE}$  pins. Data will be available t<sub>ACE</sub> after  $\overline{CE}$  or t<sub>DOE</sub> after  $\overline{OE}$  is asserted (see figures 3a and 3b).

#### Master/Slave

A  $M/\overline{S}$  pin is provided in order to expand the word width by configuring the device as either a master or a slave. The  $\overline{BUSY}$  output of the master is connected to the  $\overline{BUSY}$  input of the slave. Writing of slave devices must be delayed until after the BUSY input has settled. Otherwise, the slave chip may begin a write cycle during a contention situation. When presented as a HIGH input, the  $M/\overline{S}$  pin allows the device to be used as a master and, therefore, the  $\overline{BUSY}$  line is an output.  $\overline{BUSY}$  can then be used to send the arbitration outcome to a slave. When presented as a LOW input, the  $M/\overline{S}$  pin allows the device to be used as a slave, and, therefore, the  $\overline{BUSY}$  pin is an input.

### UT7C138/139

Table 1. Non-Contending Read/Write

| Inputs |     |               | Outputs            |                    |

|--------|-----|---------------|--------------------|--------------------|

| CE     | R/W | <del>OE</del> | I/O <sub>0-7</sub> | Operation          |

| Н      | Х   | Х             | High Z             | Power Down         |

| Х      | Х   | Н             | High Z             | I/O Lines Disabled |

| L      | Н   | L             | Data Out           | Read               |

| L      | L   | Х             | Data In            | Write              |

| L      | Х   | Х             |                    | Illegal Condition  |

#### **Radiation Hardness**

The UT7C138/139 incorporates special design and layout features which allow operation in high-level radiation environments. UTMC has developed special low-temperature processing techniques designed to enhance the total-dose radiation hardness of both the gate oxide and the field oxide while maintaining the circuit density and reliability. For transient radiation hardness and latchup immunity, UTMC builds all radiation-hardened products on epitaxial wafers using an advanced twin-tub CMOS process. In addition, UTMC pays special attention to power and ground distribution during the design phase, minimizing dose-rate upset caused by rail collapse.

Table 2. Radiation Hardness Design Specifications<sup>1</sup>

| Total Dose                                                        | 1.0E6                                                          | rads(Si)                |

|-------------------------------------------------------------------|----------------------------------------------------------------|-------------------------|

| LET Threshold                                                     | 85                                                             | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence <sup>2</sup>                                      | 3.0E14                                                         | n/cm²                   |

| Memory Device Cross Section @ LET<br>= 120MeV-cm <sup>2</sup> /mg | ≤ 1.376E <sup>-2</sup> (4K×8)<br>≤ 1.548E <sup>-2</sup> (4K×9) | cm <sup>2</sup>         |

- 1) The DPRAM will not latchup during radiation exposure under recommended operating conditions.

- 2) Not tested for CMOS technology.

## UT7C138/139

### Absolute Maximum Ratings 1

(Referenced to Vss)

| Symbol            | Parameter                                         | Limits                            |

|-------------------|---------------------------------------------------|-----------------------------------|

| $V_{DD}$          | DC supply voltage                                 | -0.5 to 7.0V                      |

| V <sub>I/O</sub>  | Voltage on any pin                                | -0.5 to (V <sub>DD</sub> + 0.3) V |

| T <sub>STG</sub>  | Storage temperature                               | -65 to +150°C                     |

| P <sub>D</sub>    | Maximum power dissipation                         | 2.0 W                             |

| Tı                | Maximum junction temperature <sup>2</sup>         | +150°C                            |

| $\Theta_{\sf JC}$ | Thermal resistance, junction-to-case <sup>3</sup> | 3.3℃/W                            |

| $I_{I}$           | DC input current                                  | ±10mA                             |

#### **Notes:**

- 1) Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2) Maximum junction temperature may be increased to +175°C during burn-in and steady-static life.

- 3) Test per MIL-STD-883, Method 1012, infinite heat sink.

### **Recommended Operating Conditions**

| Symbol          | Parameter               | Limits                |

|-----------------|-------------------------|-----------------------|

| $V_{DD}$        | Positive Supply voltage | 4.5 to 5.5V           |

| T <sub>C</sub>  | Case temperature range  | -55 to +125℃          |

| V <sub>IN</sub> | DC input voltage        | 0V to V <sub>DD</sub> |

### DC Electrical Characteristics (Pre/Post-Radiation)\*

$(V_{DD} = 5.0V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| Symbol                          | Parameter                          | Condition                                                                 | MIN                | MAX                | Unit     |

|---------------------------------|------------------------------------|---------------------------------------------------------------------------|--------------------|--------------------|----------|

| $V_{\mathrm{IH}}$               | High-level input voltage           | (CMOS)                                                                    | 0.7V <sub>DD</sub> |                    | V        |

| $V_{\mathrm{IL}}$               | Low-level input voltage            | (CMOS)                                                                    |                    | 0.3V <sub>DD</sub> | V        |

| V <sub>OL</sub>                 | Low-level output voltage           | $I_{OL} = 8mA$ , $V_{DD} = 4.5V$ (TTL)                                    |                    | 0.4                | V        |

| V <sub>OL</sub>                 | Low-level output voltage           | $I_{OL} = 200 \mu A$ , $V_{DD} = 4.5 V$ (CMOS)                            |                    | 0.05               | V        |

| V <sub>OH</sub>                 | High-level output voltage          | $I_{OH} = -4mA$ , $V_{DD} = 4.5V$ (TTL)                                   | 2.4                |                    | V        |

| V <sub>OH</sub>                 | High-level output voltage          | $I_{OH} = -200 \mu A$ , $V_{DD} = 4.5 V$ (CMOS)                           | 4.45               |                    | V        |

| $C_{IN}^1$                      | Input capacitance                  | f = 1MHz @ 0V                                                             |                    | 25                 | pF       |

| C <sub>IO</sub> <sup>1</sup>    | Bidirectional I/O capacitance      | f = 1MHz @ 0V                                                             |                    | 25                 | pF       |

| $I_{IN}$                        | Input leakage current              | $V_{IN} = V_{DD}$ and $V_{SS}$                                            | -10                | 10                 | μΑ       |

| I <sub>OZ</sub>                 | Three-state output leakage current | $V_{O} = V_{DD}$ and $V_{SS}$<br>$V_{DD} = 5.5V$<br>$\overline{G} = 5.5V$ | -10                | 10                 | μΑ       |

| I <sub>OS</sub> <sup>2, 3</sup> | Short-circuit output current       | $V_{DD} = 5.5V, V_{O} = V_{DD}$<br>$V_{DD} = 5.5V, V_{O} = 0V$            | -90                | 90                 | mA<br>mA |

### UT7C138/139

| I <sub>DD</sub> (OP) <sup>4, 5</sup> | Supply current operating (both ports)<br>@ 22.2MHz   | CMOS inputs ( $I_{OUT} = 0$ ) $V_{DD} = 5.5V$                                                                                           | 300 | mA |

|--------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| I <sub>DD</sub> (OP) <sup>4, 6</sup> | Supply current operating (single port)<br>@ 22.2 MHz | CMOS inputs ( $I_{OUT} = 0$ ) $V_{DD} = 5.5V$                                                                                           | 150 | mA |

| I <sub>DD</sub> (OP) <sup>4,5</sup>  | Supply current operating (both ports)<br>@ 18.2MHz   | CMOS inputs ( $I_{OUT} = 0$ ) $V_{DD} = 5.5V$                                                                                           | 275 | mA |

| I <sub>DD</sub> (OP) <sup>4, 6</sup> | Supply current operating (single port)<br>@ 18.2 MHz | CMOS inputs ( $I_{OUT} = 0$ ) $V_{DD} = 5.5V$                                                                                           | 138 | mA |

| I <sub>DD</sub> (SB) <sup>4</sup>    | Supply current standby                               | $\frac{\text{CMOS inputs (I}_{\text{OUT}} = 0)}{\overline{\text{CE}} = \text{V}_{\text{DD}} - 0.5, \text{V}_{\text{DD}} = 5.5\text{V}}$ | 1   | mA |

#### **Notes:**

- \* Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019.

- 1) Measured only for initial qualification and after process or design changes that could affect input/output capacitance.

- 2) Supplied as a design limit but not guaranteed or tested.

- 3) Not more than one output may be shorted at a time for maximum duration of one second.

- 4)  $V_{IH} = 5.5V$ ,  $V_{IL} = 0V$ .

- 5) I<sub>DD</sub> (OP) derates at 6.4mA/MHz.

- 6) I<sub>DD</sub> (OP) derates at 3.4mA/MHz.

### **AC Characteristics Read Cycle 1,2**

$(V_{DD} = 5.0V \pm 10\%)$

| Symbol            | Parameter                          |    | 8 - 45<br>9 - 45<br>MAX | 7C138 - 55<br>7C139 - 55<br>MIN MAX |    | Unit |

|-------------------|------------------------------------|----|-------------------------|-------------------------------------|----|------|

| $t_{RC}$          | Read cycle time                    | 45 |                         | 55                                  |    | ns   |

| t <sub>AA</sub>   | Address to data valid <sup>2</sup> |    | 45                      |                                     | 55 | ns   |

| t <sub>oha</sub>  | Output hold from address change    | 5  |                         | 5                                   |    | ns   |

| $t_{ACE}$         | CE LOW to data valid <sup>2</sup>  |    | 45                      |                                     | 55 | ns   |

| $t_{DOE}$         | OE LOW to data valid <sup>2</sup>  |    | 20                      |                                     | 20 | ns   |

| t <sub>LZOE</sub> | OE LOW to low Z                    | 0  |                         | 0                                   |    | ns   |

| t <sub>HZOE</sub> | OE HIGH to high Z                  |    | 20                      |                                     | 20 | ns   |

| t <sub>LZCE</sub> | CE LOW to low Z                    | 0  |                         | 0                                   |    | ns   |

| t <sub>HZCE</sub> | CE HIGH to high Z                  |    | 20                      |                                     | 20 | ns   |

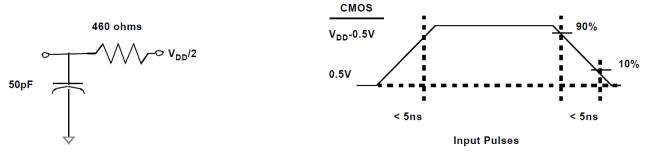

- 1) Test conditions assume signal transition time of 5ns or less, timing reference levels of  $V_{DD}/2$ , input pulse levels of 0.5V to  $V_{DD}-0.5V$ , and output loading of the specified  $I_{OL}/I_{OH}$  and 50-pF load capacitance.

- 2) AC test conditions use  $V_{OH}/V_{OL}=V_{DD}/2 + 500$ mV.

# UT7C138/139

Figure 3a. Read Cycle 1

#### **Assumptions:**

- 1)  $R/\overline{W}$  is HIGH for read cycle

- 2) Device is continuously selected  $\overline{CE}$ =LOW and  $\overline{OE}$ =LOW

Figure 3b. Read Cycle 2

#### **Assumptions:**

- 1) Address valid prior to or coincident with  $\overline{\text{CE}}$  transition LOW

- 2)  $R/\overline{W}$  is HIGH for read cycle

## UT7C138/139

Figure 3c: Read Timing with Port-to-Port Delay

#### **Assumptions:**

- 1)  $\overline{\text{BUSY}}$  = HIGH for the writing port

- 2)  $\overline{CE}_L = \overline{CE}_R = LOW$

# UT7C138/139

### **AC Characteristics Write Cycle<sup>1</sup>**

$(V_{DD} = 5.0V \pm 10\%)$

| Symbol                 | Parameter                           | 7C138 - 45<br>7C139 - 45 |     | 7C138 - 55<br>7C139 - 55 |     | Unit |

|------------------------|-------------------------------------|--------------------------|-----|--------------------------|-----|------|

| <b>5</b> , <b>5</b> 6. |                                     | MIN                      | MAX | MIN                      | MAX |      |

| t <sub>wc</sub>        | Write cycle time                    | 45                       |     | 55                       |     | ns   |

| t <sub>SCE</sub>       | CE LOW to write end                 | 40                       |     | 50                       |     | ns   |

| t <sub>AW</sub>        | Address set-up to write end         | 40                       |     | 50                       |     | ns   |

| t <sub>HA</sub>        | Address hold from write end         | 0                        |     | 0                        |     | ns   |

| t <sub>SA</sub>        | Address set-up to write start       | 0                        |     | 0                        |     | ns   |

| t <sub>PWE</sub>       | Write pulse width                   | 40                       |     | 50                       |     | ns   |

| t <sub>SD</sub>        | Data set-up to write end            | 40                       |     | 50                       |     | ns   |

| t <sub>HD</sub>        | Data hold from write end            | 0                        |     | 0                        |     | ns   |

| t <sub>HZWE</sub>      | R/W LOW to high Z                   |                          | 20  |                          | 20  | ns   |

| t <sub>LZWE</sub>      | R/W HIGH to low Z                   | 0                        |     | 0                        |     | ns   |

| t <sub>WDD</sub>       | Write pulse to data delay           | 95                       |     | 105                      |     | ns   |

| t <sub>DDD</sub>       | Write data valid to read data valid | 95                       |     | 105                      |     | ns   |

| t <sub>whwL</sub>      | Write disable time                  | 5                        |     | 5                        |     | ns   |

#### Note:

1) For information on part-to-part delay through DPRAM cells from writing port to reading port, refer to Read Timing with Port-to-Port Delay waveform (see figure 3c).

### UT7C138/139

Figure 4a. Write Cycle 1: OE Three-States Data I/Os (Either Port)

#### **Assumptions:**

- 1) The internal write time of memory is defined by the overlap of  $\overline{\text{CE}}$  LOW and  $R/\overline{W}$  LOW. Both signals must be LOW to initiate a write, and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

- 2) If  $\overline{OE}$  is LOW during a R/ $\overline{W}$  controlled write cycle, the write pulse width must be the larger of  $t_{PWE}$  or  $(t_{HZWE} + t_{SD})$  to allow the I/O drivers to turn off and data to be placed on the bus for the required  $t_{SD}$ . If  $\overline{OE}$  is HIGH during a R/ $\overline{W}$  controlled write cycle (as in this example), this requirement does not apply and the write pulse can be as short as the specified  $t_{PWE}$ .

- 3)  $R/\overline{W}$  must be HIGH during all address transactions.

## UT7C138/139

Figure 4b. Write Cycle 2: R/W Three-States Data I/Os (Either Port)

#### **Assumptions:**

- 1) The internal write time of memory is defined by the overlap of  $\overline{\text{CE}}$  LOW and R/W LOW. Both signals must be LOW to initiate a write, and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

- 2)  $R/\overline{W}$  must be HIGH during all address transactions.

- 3) Data I/O pins enter high impedance even if  $\overline{OE}$  is held LOW during write.

### **AC Characteristics Busy Cycle <sup>1</sup>**

$(V_{DD} = 5.0V \pm 10\%)$

| Symbol                         | Parameter                         |    | 8 - 45<br>9 - 45<br>MAX | 7C13<br>7C13<br>MIN | 8 - 55<br>9 - 55<br>MAX | Unit |

|--------------------------------|-----------------------------------|----|-------------------------|---------------------|-------------------------|------|

| t <sub>BLA</sub>               | BUSY LOW from address match       |    | 25                      |                     | 30                      | ns   |

| t <sub>BZA</sub>               | BUSY HIGH-Z from address mismatch |    | 25                      |                     | 30                      | ns   |

| t <sub>BLC</sub>               | BUSY LOW from CE LOW              |    | 25                      |                     | 30                      | ns   |

| t <sub>BZC</sub>               | BUSY HIGH from CE HIGH            |    | 25                      |                     | 30                      | ns   |

| t <sub>PS</sub> <sup>2,3</sup> | Port set-up for priority          | 5  |                         | 5                   |                         | ns   |

| t <sub>WB</sub>                | R/W LOW after BUSY LOW            | 0  |                         | 0                   |                         | ns   |

| twн                            | R/W HIGH after BUSY HIGH          | 40 |                         | 50                  |                         | ns   |

| t <sub>BDD</sub>               | BUSY HIGH to data valid           |    | 45                      |                     | 55                      | ns   |

#### **Notes:**

- 1) Test conditions assume signal transition time of 5ns or less, timing reference levels of  $V_{DD}/2$ , input pulse levels of 0.5V to  $V_{DD}-0.5V$ , and output loading of the specified  $I_{OL}/I_{OH}$  and 50-pF load capacitance.

- 2) Violation of t<sub>PS</sub> (with addresses matching) results in at least one of the two busy output signals asserting, only one port remains busy.

- 3) When violating t<sub>PS</sub>, the busy signal asserts on one port or the other; there is no guarantee on which port the busy signal asserts.

Figure 5a. Read Timing with  $\overline{BUSY}$  (M/ $\overline{S}$ =HIGH)

#### **Assumption:**

1)  $\overline{CE}_L = \overline{CE}_R = LOW$

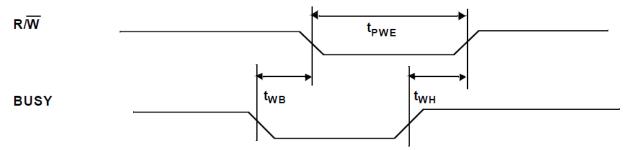

Figure 5b. Write Timing with  $\overline{BUSY}$  (M/ $\overline{S}$ =LOW)

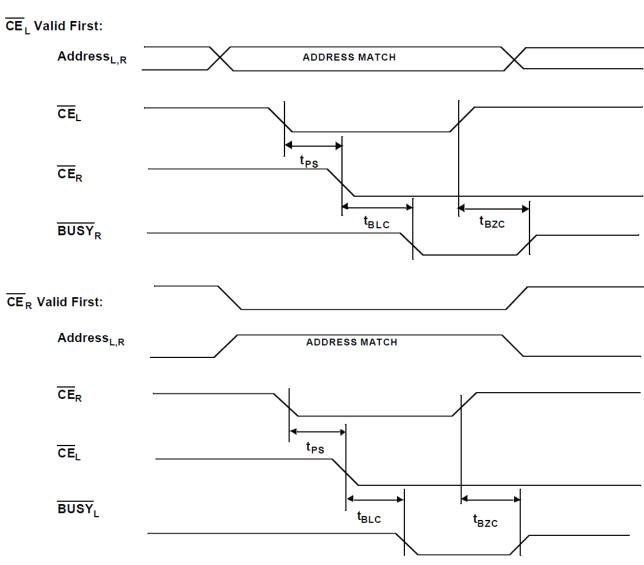

Figure 5c: BUSY Timing Diagram No. 1 (CE Arbitration)

#### **Assumption:**

1) If t<sub>PS</sub> is violated, the BUSY signal will be asserted on one side or the other, but there is no guarantee on which side BUSY will be asserted.

#### **Left Address Valid First:**

### **Right Address Valid First:**

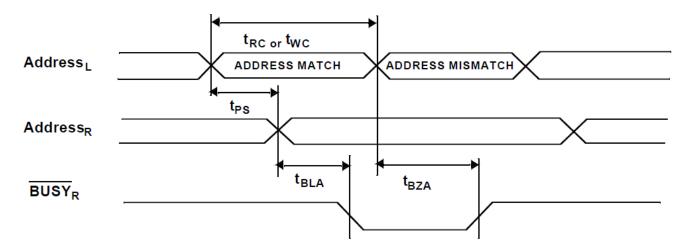

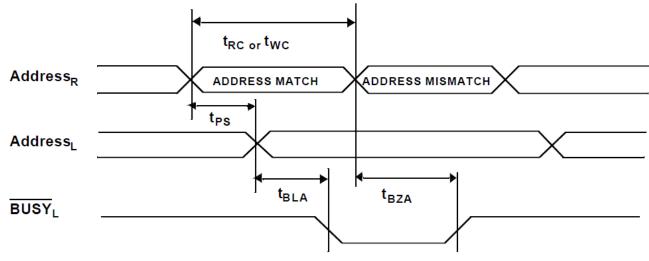

Figure 5d. BUSY Timing Diagram No. 2 (Address Arbitration)

#### **Assumptions:**

1) If  $t_{PS}$  is violated, the  $\overline{BUSY}$  signal will be asserted on one side or the other, but there is no guarantee on which side  $\overline{BUSY}$  will be asserted.

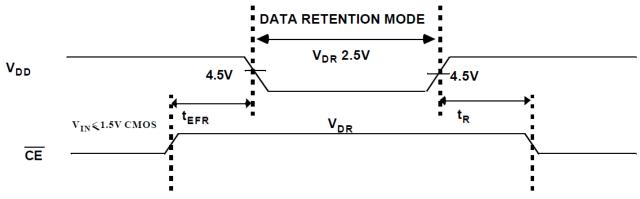

### **Data Retention Characteristics (Pre-Radiation)**

$(T_C = 25^{\circ}C)$

| Symbol                        | Parameter                            | Minimum                            | Maximum<br>V <sub>DD</sub> @<br>2.5V | Unit |

|-------------------------------|--------------------------------------|------------------------------------|--------------------------------------|------|

| $V_{DR}$                      | V <sub>DD</sub> for data retention   | 2.5                                |                                      | ٧    |

| I <sub>DDR</sub> <sup>1</sup> | Data retention current               |                                    | 400                                  | μΑ   |

| t <sub>EFR</sub> 1,2          | Chip deselect to data retention time | 0                                  |                                      | ns   |

| t <sub>R</sub> 1,2            | Operation recovery time              | t <sub>WC</sub> or t <sub>RC</sub> |                                      | ns   |

#### **Notes:**

- 1)  $\overline{\text{CE}}$  equals  $V_{DR}$ , all other inputs equal  $V_{DR}$  or  $V_{SS}$ .

- 2) Guaranteed but not tested.

Figure 6. Low V<sub>DD</sub> Data Retention Waveform

Figure 7. AC Test Loads and Input Waveforms

- 1) 50pF including scope probe and test socket.

- 2) Measurement of data output occurs at the low to high or high to low transition mid-point (CMOS input =  $V_{DD}/2$ ).

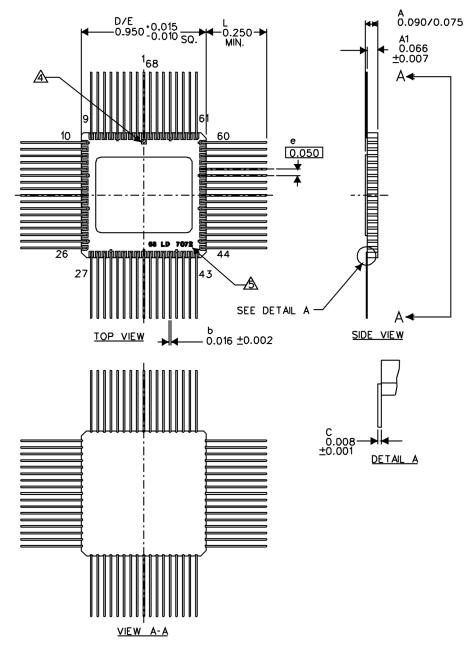

Figure 8. 68-pin Flatpack

- 1) All package finishes are per MIL-PRF-38535.

- 2) Letter designations are for cross-reference to MIL-STD-1835.

- 3) All leads increase max limit by 0.003 measured at the center of the flat, when lead finish A (solder) is applied.

- 4) ID mark: Configuration is optional.

- 5) Lettering is not subject to marking criteria.

- 6) Total weight is approximately 4.5 grams.

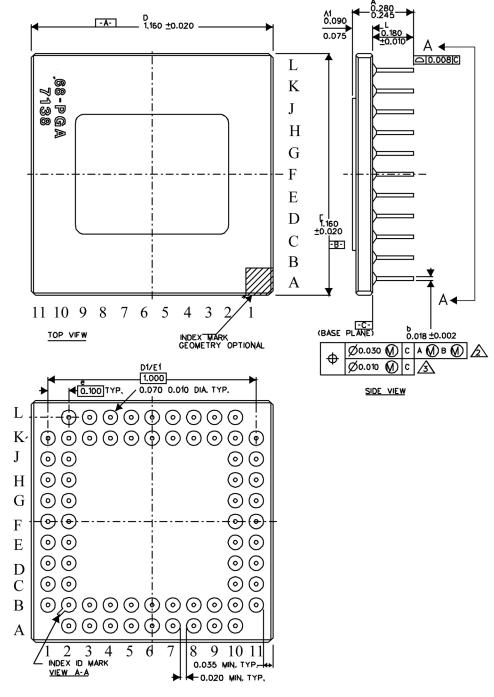

Figure 9. 68-pin PGA

- 1) All package finishes are per MIL-PRF-38535.

- 2) True position applies at base plane (Datum C).

- 3) True position applies at pin tips.

- 4) Letter designations are for cross-reference to MIL-STD-1835.

- 5) Total weight is approximately 7.0 grams.

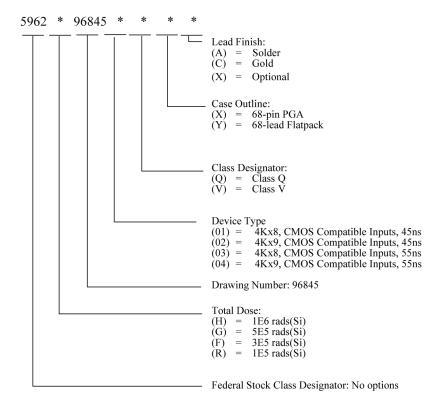

### **Ordering Information**

#### UT7C138/UT7C139 Dual-Port SRAM: SMD

- 1) Lead finish (A, C, or X) must be specified.

- 2) If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening.

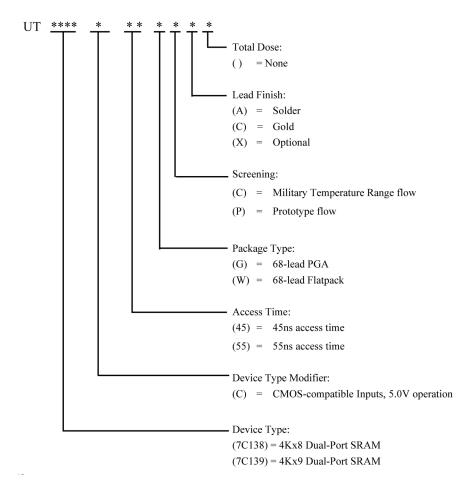

#### UT7C138/UT7C139 Dual-Port SRAM

- 1) Lead finish (A, C, or X) must be specified.

- 2) If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Military Temperature Range flow per UTMC Manufacturing Flows Document. Radiation characteristics are neither tested nor guaranteed and may not be specified.

- 4) Prototypes are produced to UTMC's prototype flow and are tested at 25°C only. Radiation characteristics are neither tested nor guaranteed. Lead finish is GOLD only.

#### **Datasheet Definitions**

|                       | DEFINITION                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet <b>is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                             |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.