### Features

- 8 x 8, Full Duplex Crosspoint Switch Matrix

- Data Rates up to 3.125 Gbps per Channel

- Protocol Independent

- Low Latency

- Low Channel-to-Channel Skew

- SPI Port Control Interface

- Diagnostic Serial Loopback Mode

- Low Power Dissipation

- Separate Power Domains per Bank

- Power Down Feature for Unused Lanes

- Loss of Signal (LOS) Detect

- Adjustable 50  $\Omega$  High-Speed Terminations

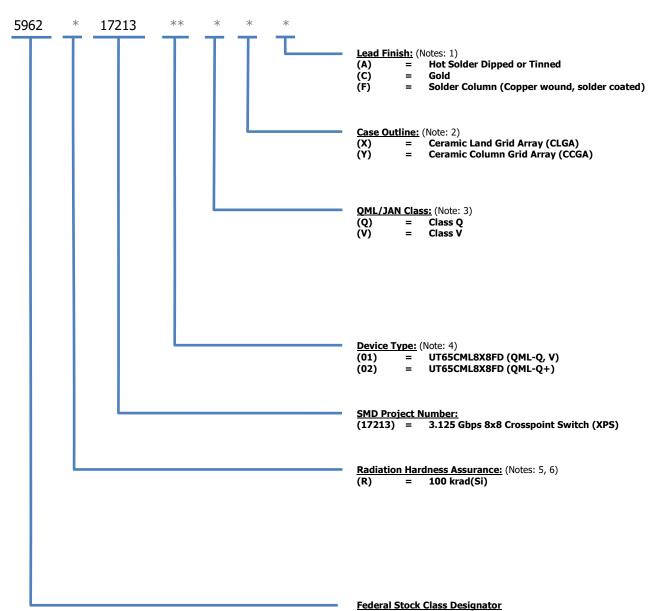

- Standard Microelectronics Drawing (SMD):

- 5962-17213 (QML-Q, V Pending)

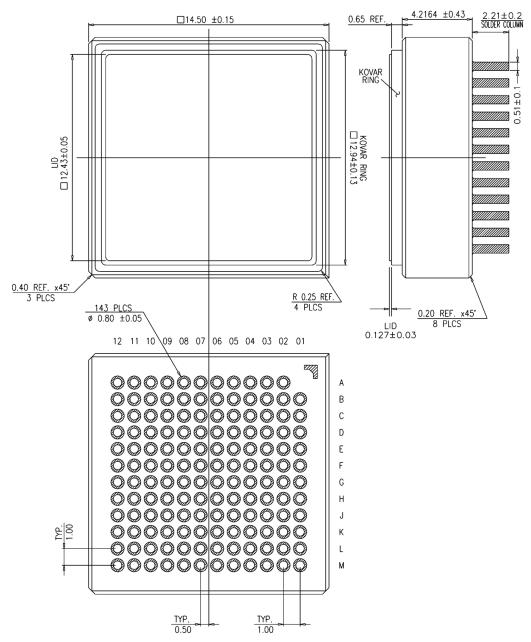

- Package Information:

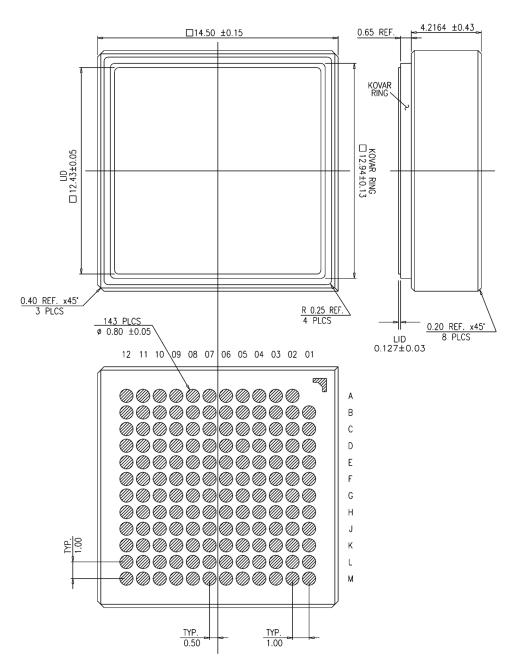

- 143-Pin Ceramic Land Grid Array (C-LGA)

- Base Package (Pads Only)

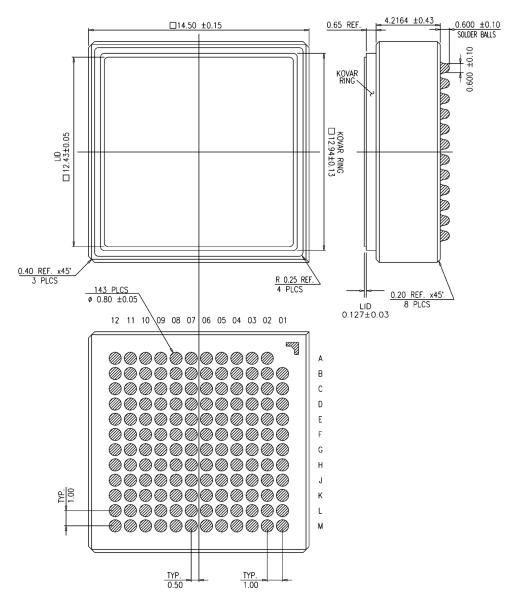

- Ceramic Column Grid Array (C-CGA)

- Flight Units

- Ceramic Ball Grid Array (C-BGA)

- Prototypes

- Small Size: 14.5 x 14.5 mm; 1 mm Pad Pitch

### **Operational Environment**

- Temperature Range: -55°C ≤ Tc ≤ +105°C

- Total Dose: 1x10<sup>5</sup> rad(Si)

- SEL Immune: ≤ 100 MeV·cm<sup>2</sup>/mg

- SET-BER: 7x10<sup>-17</sup> errors/dev-day

#### Applications

- High Speed Serial Repeater and Distribution Applications

- Primary and Redundant Data Switching

- Port Replication

- Space VPX (VITA78) Data Plane Switches

- High Speed 2:1 MUX + 1:2 DEMUX Functions

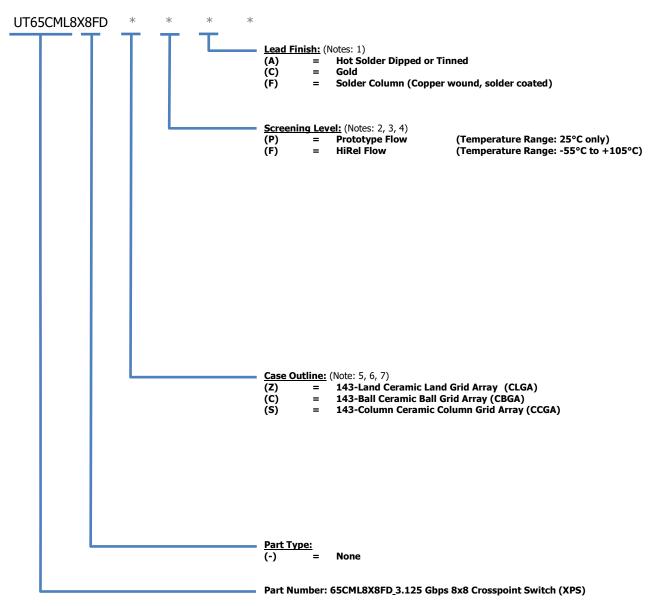

# 3.125 Gbps Crosspoint Switch (XPS)

### Introduction

The emerging VITA78, Space VPX, standard specifies a data plane switch function which enables a redundant and cross strapped serial data path within the VPX chassis. Typically, a primary serial I/O based resource is cross strapped with a redundant resource. There can also be redundant resources configured in a non-cross strapped configuration. This 8 x 8 cross point device can support implementation of either scenario.

Because the switch is purely a cross bar, it is protocol-independent. This makes the switch very versatile and can be applied in proprietary architectures, in addition to the Serial Rapid IO protocol specified in VITA78. The loop back feature, available at each four lane XAUI interface, is very useful for system diagnostics, test, and optimization.

Two key advantages of the device are its small size and low power. Any unused lanes can be powered down, and if the device is placed in close proximity to the source device (e.g. the serial data path is less than 1 or 2 cm), the TX driver can be run in half power mode.

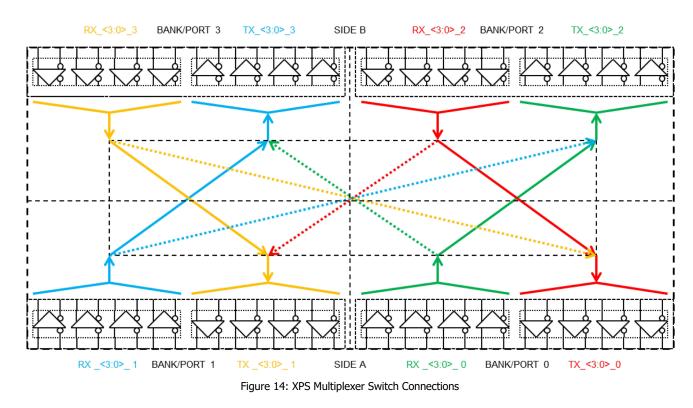

The primary function of the Space VPX 8 x 8 Crosspoint Switch is to perform switching of 10G XAUI serial data streams between one of two, full duplex, current-mode logic (CML) signal I/O pads. The primary I/O configuration is an 8 x 8 XAUI-compatible port switch matrix; each port has four full duplex lanes operating at up to 3.125 Gbps.

Inputs include Receiver (RX) Equalization (EQ) to compensate for input losses. The input signal is then routed through a MUX to the selected output channel. Output Transmit (TX) De-Emphasis (DE) is not currently supported. The Cross Point Switch does not include input Clock and Data Recovery (CDR), and so operates as a Repeater and not a Re-timer.

The MUX switches which determine the core matrix configuration are set via the 4-wire SPI register port.

# **1.0 Functional Description**

### 1.1 Overview

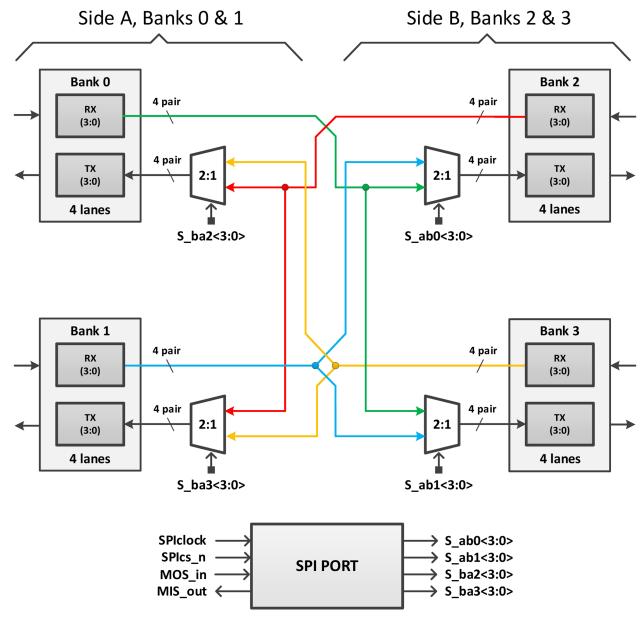

Figure 1 illustrates the functionality of the Crosspoint Switch (XPS). The device is comprised of 4 banks, each containing 4 individual lanes. Each lane can be individually enabled for transmit only, receive only, or full-duplex operation.

Figure 1: Block Diagram

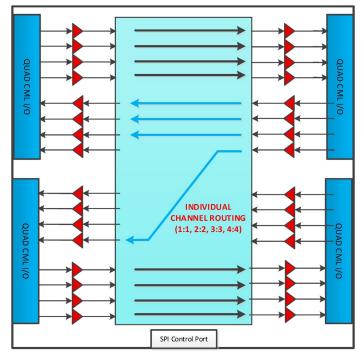

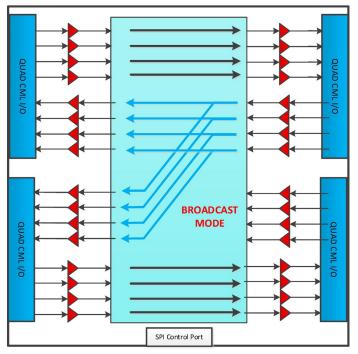

The Crosspoint Switch functionality is illustrated in figures 2 and 3. Individual lanes or groups of lanes within a bank can be routed directly, as an A-B Crosspoint, or broadcasted to associated banks.

Figure 2: Crosspoint Switch Individual Channel Routing

Figure 3: Broadcasting One Input Bank to Two Output Banks

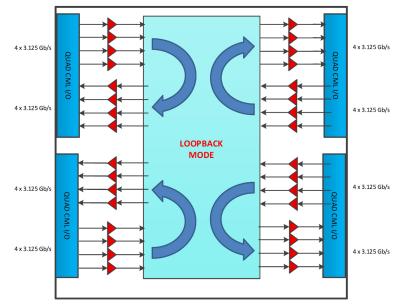

The serial loop-back function is illustrated in Figure 4. Serial data present at the receiver inputs is looped back and re-transmitted within the same lane in the same bank. This function is provided to the system developer for debugging and continuity check purposes.

Figure 4: Serial RX to TX Loopback Mode for System De-Bugging

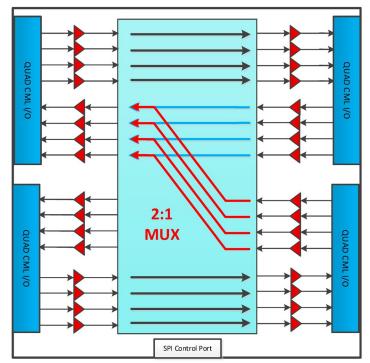

Figure 5: Crosspoint 2:1 MUX Function

**RELEASED 03/23/22**

# UT65CML8X8FD

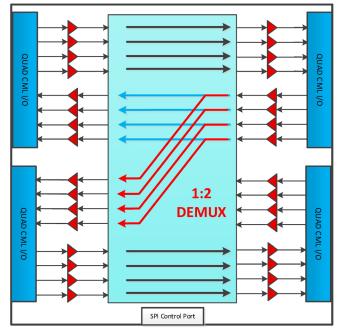

Figure 6: Crosspoint 1:2 DEMUX Function

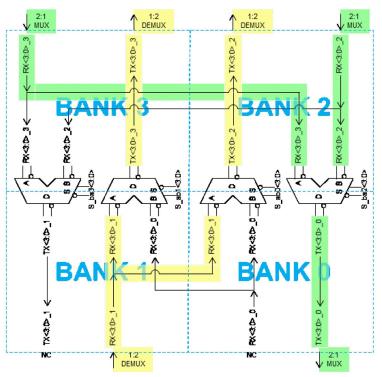

Figure 7: Implementation of Single XPS 2:1 MUX (Green) and 1:2 DEMUX (Yellow) Functions

# 3.125 Gbps Crosspoint Switch (XPS)

# UT65CML8X8FD

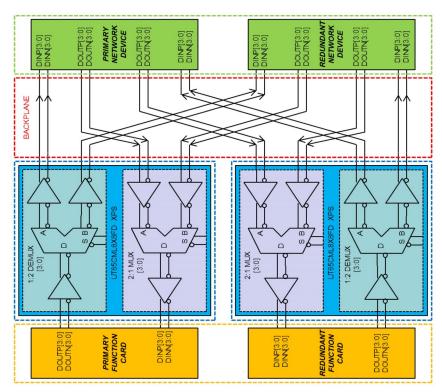

Figure 8: Crosspoint Full Redundancy A-B Cross-Strapping Using Two XPS Devices

### 1.2 Input Receiver (RX)

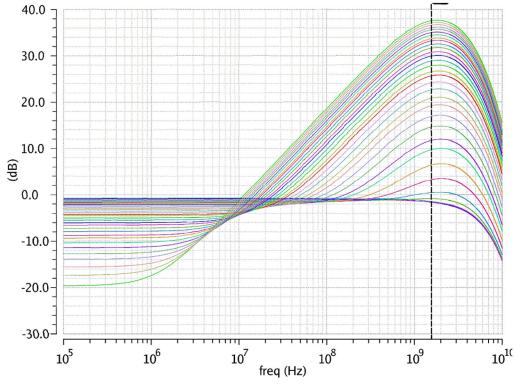

The Receiver (RX) input buffers operate using the current-mode logic (CML) I/O standard and are terminated into  $50\Omega$ . The input buffers accept an input amplitude range of 100-800 mV p-p single-ended, or 200-1600 mV p-p differential. The input termination is tunable over a narrow resistor value range in order to provide adjustment for process variation to approximately  $50\Omega$  input impedance for best signal integrity (SI). An input receiver equalizer is provided to compensate for channel losses. The Rx EQ is composed of a Continuous Time Linear Equalizer (CTLE) circuit with programmable settings. Each receiver equalizer circuit can be programmed to one of 32 values. These values are set through internal registers EQ\_0-3\_0-3<0:4> via the SPI Port interface. An input Loss of Signal (LOS) detect function is supported for system-level monitoring and fault handling. When enabled, if the input signal edge rate falls below 10 MHz, the LOS detect function squelches all associated transmitter outputs. The LOS function is enabled via internal registers EN\_LOS\_0-3<0:3>. The status of the LOS function for any port can be observed by reading SPI registers HEX 27 or 28 <7:0>.

### 1.3 Output Transmitter (TX)

The Transmitter (TX) output drivers operate using the current mode logic (CML) I/O levels. Each output is terminated into 50 or 100  $\Omega$  differentially. No output Pre-Emphasis is provided as the device is not a data re-timer. The output termination is selectable over a narrow resistor value range in order to provide adjustment for process variation. The output TX amplitude is programmable using internal registers TX\_I\_0-1<0:31>, which set the output drive currents. The output amplitude range is 200-600 mV p-p single-ended, or 400-1200 mV p-p differential. Selecting a drive current sufficient to achieve error-free communications, yet less than the maximum available minimizes power consumption.

**Note:** Both RX inputs and TX outputs must be AC-coupled using broadband  $0.1\mu$ F (100nF) capacitors. The intended XPS application is for the XAUI specification using 8b/10b encoding as part of RapidIO and SpaceVPX requirements, as well as other DC balanced data formats.

### 1.4 Serial Peripheral Interface (SPI) PORT

### 1.4.1 Overview

The Serial Peripheral Interface (SPI) bus is a simple, synchronous, full duplex, 4-wire serial communications interface in a Master-Slave device configuration. SPI supports single, or multiple slave devices. There is always only one master device. Although there is no formal SPI bus standard, it is widely used, with many variations in existence. Data is clocked out of the Master device on the MOSI pin to a selected Slave device. One bit is transmitted or received on every SPIclock edge or one byte for eight clock cycles. The SPIcs\_n signal is de-asserted to indicate boundaries between command and data words, or to terminate communication between devices. Because SPI is a primitive protocol, there is no acknowledgement bit (ACK) available. Correct data transmission is verified by reading the selected register byte in question.

### 1.4.2 SPI Advantages

- Full duplex communication

- Faster data transfer than the I2C or SM bus standards

- Simple hardware interfacing

- Slave devices don't require a unique address

- A simple protocol for connecting Master and Slave devices

- Tolerant of clock period variation

- Serial or parallel configurations allow multiple devices to share the same Master SPI port

### 1.4.3 Signals

Table 1 lists the Serial Peripheral Interface signals and their directions and functions.

### Table 1: SPI Bus Signals

| Signal Name | Signal Description            | Signal Direction            |

|-------------|-------------------------------|-----------------------------|

| SPIclock    | SPI Serial Clock              | From Master to Slave device |

| MOS_in      | Master Out / Slave In         | From Master to Slave device |

| MIS_out     | Master In / Slave Out         | From Slave to Master device |

| SPIcs_n     | Slave Chip Select, Active Low | From Master to Slave device |

### **1.4.4 SPI Bus Configurations**

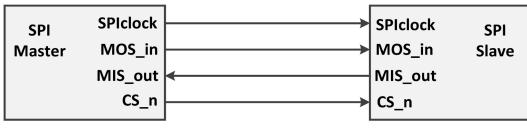

Figure 9a shows a simple point to point SPI configuration. Command and data word operations are conducted in single byte transactions separated by SPIcs\_n assertions.

Figure 9a: Master, single slave – Point-to-point configuration

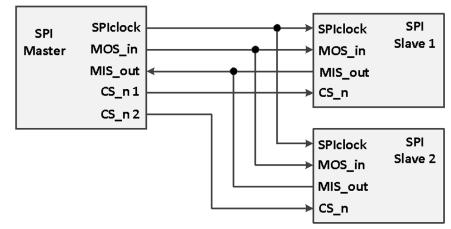

Figure 9b illustrates multiple parallel Slave devices controlled by a single Master device. While command and data word operations are conducted in single byte transactions, each Slave device has a unique SPIcs\_n selection signal.

Figure 9b. Single master, multiple slaves - Parallel configuration

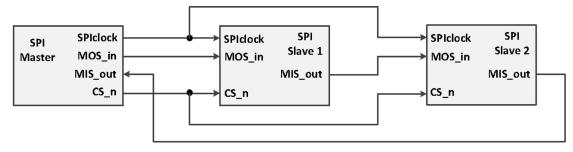

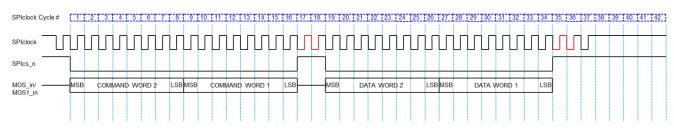

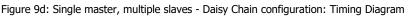

Figures 9c, 9d illustrate multiple serially-connected (i.e. daisy chain) slave devices controlled by a single master device. Command and data word operations are conducted as a string of serially transmitted, byte-wide transactions. For N devices connected in serial, N bytes are transmitted back to back. The SPIcs\_n signal remains enabled for the duration of multiple command or data word operation. For the example of Figure 9thec, 2 bytes of command or data information are transmitted with SPIcs\_n active for 16 clock cycles, when x2 SPI Port devices are daisy-chained, as depicted in Figure 9c. As a result, the Slave device FIFOs receive the byte intended for them. Information for the most distant device is transmitted first, and the closest last. Figure 9d shows an example timing diagram for the daisy chain circuit of Figure 9c.

Figure 9c: Single master, multiple slaves - Daisy Chain configuration: Block Diagram

#### Notes:

- 1) Command & Data Word 1 correspond to SPI Slave 1 device

- 2) Command & Data Word 2 correspond to SPI Slave 2 device

- 3) MOS\_in & MIS\_out correspond to SPI Master device

- 4) MOS1\_in corresponds to SPI Slave 1 device

### 1.4.5 SPI Interface Reset

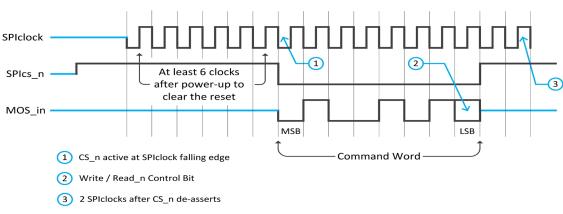

Figure 10 illustrates the SPI port reset and general timing. When the Crosspoint switch is powered, its internal poweron reset (POR) places the SPI port in a reset condition. The user must supply at least 6 clocks to bring the part out of reset. The chip select signal (SPIcs\_n, active low) is asserted at the falling edge of SPIclock ①. In a SPI transaction, a command word is issued first. Its 7 most significant bits address the control register in question, while the least significant bit indicates whether a read or write operation is requested. A data word follows the command word to be written, or the results of a read, and will be shown in detail in the following sections. Upon completion of a command or data transaction, a minimum of two SPIclock cycles are required to register the transaction. The order and number of READs and WRITEs is not critical to SPI port operation. SPIclock can and should be stopped after communication is complete.

Figure 10: SPI Reset and General Timing

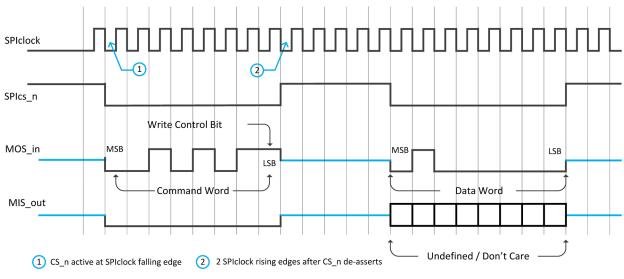

# 1.4.6 SPI WRITE

A SPI WRITE operation is shown in Figure 11. The command word LSB indicates a WRITE operation to address Hex 15. The command word LSB on MOS\_in ("MOSI"), when set to a 1, indicates a WRITE operation. The data word indicates the data to be written to that location. The chip select SPIcs\_n is enabled on the falling edge of SPIclock. After a SPI interface reset, only one clock is required to begin a SPI transaction. Following a command or data word, a minimum of 2 SPIclock cycles are required to register the transaction.

If the previous 8-bit sequence is a WRITE command or WRITE data, then the current 8-bit sequence on MIS\_out ("MISO") is undefined/don't care.

A "continuous" or sequential WRITE operation is supported by the XPS SPI Port. MIS\_out ("MISO") can repeatedly write to selected addresses, i.e. WRITE command word+ data pairs on MOS\_in ("MOSI"), continuously, until all WRITEs are completed (e.g. all XPS registers are written).

Figure 11: SPI Port WRITE operation

**RELEASED 03/23/22**

# 3.125 Gbps Crosspoint Switch (XPS)

### 1.4.7 SPI READ

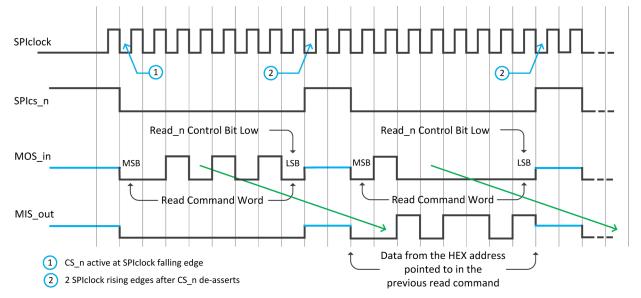

A SPI READ operation is shown in Figure 12. The command word LSB indicates a READ operation from address Hex 15. The command word LSB on MOS\_in ("MOSI"), when set to a 0, indicates a READ operation. The data word indicates the data to be read from that location. Following a data or command word, a minimum of 2 SPIclock cycles are required to register the transaction. Data transmitted on MIS\_out ("MISO") corresponds to the addressed register value of the previous READ command. The MIS\_out ("MISO") data is transmitted on the negative edge of SPIclock. The first bit is valid data as SPIcs\_n is asserted and active at the negative-edge of the SPIclock.

If the previous 8-bit sequence is a READ-command, then the data output on MIS\_out ("MISO"), i.e. the current 8-bit sequence, is valid and corresponds to that READ-command.

A "continuous" or sequential READ operation is supported by the XPS SPI Port. MIS\_out ("MISO") can repeatedly output addressed data as selected by address, i.e. READ Command Word on MOS\_in ("MOSI"), until all READs are completed (e.g. all XPS registers are read).

Figure 12: SPI Port Read operation

### 1.4.8 SPI Port Safety Feature

If the number of bits shifted out on the MOS\_in ("MOSI") is not a multiple of 8, the command will be ignored or dropped. If a WRITE command is a multiple of 8 bits, but the following data word was not, the WRITE command and the data word will be dropped. In either of these two cases, the WRITE command will need to be re-transmitted.

# 2.0 Pinlist

### 2.1 Pinlist – Table Format

### Table 2: Pin List – Pin I/O Function Type Key – Table Format

| Abbreviation | Description                            |

|--------------|----------------------------------------|

| CML-O        | CML Compatible Output                  |

| CML-I        | CML Compatible Input                   |

| SPI-I        | LVCMOS Compatible Input-SPI Port Only  |

| SPI-O        | LVCMOS Compatible Output-SPI Port Only |

| СОВ          | CAES Use Only                          |

| VDD          | Power Supply                           |

| VSS          | Ground                                 |

**RELEASED 03/23/22**

# UT65CML8X8FD

### Table 2: Pin List – Pin Description – Table Format (Continued)

| Number | Name    | Туре                 | Description          |

|--------|---------|----------------------|----------------------|

|        | CN      | IL Transmitters (TX) |                      |

| A3     | TXP_0_0 | CML-O                | CML Output, Positive |

| A4     | TXN_0_0 | CML-O                | CML Output, Negative |

| B1     | TXP_1_0 | CML-O                | CML Output, Positive |

| B2     | TXN_1_0 | CML-O                | CML Output, Negative |

| D1     | TXP_2_0 | CML-O                | CML Output, Positive |

| D2     | TXN_2_0 | CML-O                | CML Output, Negative |

| F1     | TXP_3_0 | CML-O                | CML Output, Positive |

| F2     | TXN_3_0 | CML-O                | CML Output, Negative |

| E12    | TXP_0_1 | CML-O                | CML Output, Positive |

| E11    | TXN_0_1 | CML-O                | CML Output, Negative |

| C12    | TXP_1_1 | CML-O                | CML Output, Positive |

| C11    | TXN_1_1 | CML-O                | CML Output, Negative |

| A12    | TXP_2_1 | CML-O                | CML Output, Positive |

| A11    | TXN_2_1 | CML-O                | CML Output, Negative |

| A8     | TXP_3_1 | CML-O                | CML Output, Positive |

| A7     | TXN_3_1 | CML-O                | CML Output, Negative |

| H1     | TXP_0_2 | CML-O                | CML Output, Positive |

| H2     | TXN_0_2 | CML-O                | CML Output, Negative |

| K1     | TXP_1_2 | CML-O                | CML Output, Positive |

| K2     | TXN_1_2 | CML-O                | CML Output, Negative |

| M1     | TXP_2_2 | CML-O                | CML Output, Positive |

| M2     | TXN_2_2 | CML-O                | CML Output, Negative |

| M5     | TXP_3_2 | CML-O                | CML Output, Positive |

| M6     | TXN_3_2 | CML-O                | CML Output, Negative |

| M10    | TXP_0_3 | CML-O                | CML Output, Positive |

| M9     | TXN_0_3 | CML-O                | CML Output, Negative |

| L12    | TXP_1_3 | CML-O                | CML Output, Positive |

| L11    | TXN_1_3 | CML-O                | CML Output, Negative |

| J12    | TXP_2_3 | CML-O                | CML Output, Positive |

| J11    | TXN_2_3 | CML-O                | CML Output, Negative |

| G11    | TXP_3_3 | CML-O                | CML Output, Positive |

| G12    | TXN_3_3 | CML-O                | CML Output, Negative |

|     | СМ      | L Receivers (RX) |                     |

|-----|---------|------------------|---------------------|

| B6  | RXP_0_0 | CML-I            | CML Input, Positive |

| B5  | RXN_0_0 | CML-I            | CML Input, Negative |

| C3  | RXP_1_0 | CML-I            | CML Input, Positive |

| C4  | RXN_1_0 | CML-I            | CML Input, Negative |

| D5  | RXP_2_0 | CML-I            | CML Input, Positive |

| D6  | RXN_2_0 | CML-I            | CML Input, Negative |

| E3  | RXP_3_0 | CML-I            | CML Input, Positive |

| E4  | RXN_3_0 | CML-I            | CML Input, Negative |

| F10 | RXP_0_1 | CML-I            | CML Input, Positive |

| F9  | RXN_0_1 | CML-I            | CML Input, Negative |

| D10 | RXP_1_1 | CML-I            | CML Input, Positive |

| D9  | RXN_1_1 | CML-I            | CML Input, Negative |

| B10 | RXP_2_1 | CML-I            | CML Input, Positive |

| В9  | RXN_2_1 | CML-I            | CML Input, Negative |

| C8  | RXP_3_1 | CML-I            | CML Input, Positive |

| C7  | RXN_3_1 | CML-I            | CML Input, Negative |

| G3  | RXP_0_2 | CML-I            | CML Input, Positive |

| G4  | RXN_0_2 | CML-I            | CML Input, Negative |

| J3  | RXP_1_2 | CML-I            | CML Input, Positive |

| J4  | RXN_1_2 | CML-I            | CML Input, Negative |

| L3  | RXP_2_2 | CML-I            | CML Input, Positive |

| L4  | RXN_2_2 | CML-I            | CML Input, Negative |

| К5  | RXP_3_2 | CML-I            | CML Input, Positive |

| K6  | RXN_3_2 | CML-I            | CML Input, Negative |

| L8  | RXP_0_3 | CML-I            | CML Input, Positive |

| L7  | RXN_0_3 | CML-I            | CML Input, Negative |

| К10 | RXP_1_3 | CML-I            | CML Input, Positive |

| К9  | RXN_1_3 | CML-I            | CML Input, Negative |

| J8  | RXP_2_3 | CML-I            | CML Input, Positive |

| J7  | RXN_2_3 | CML-I            | CML Input, Negative |

| H10 | RXP_3_3 | CML-I            | CML Input, Positive |

| Н9  | RXN_3_3 | CML-I            | CML Input, Negative |

| SPI Port |          |       |                                |  |  |

|----------|----------|-------|--------------------------------|--|--|

| F7       | MOS_in   | SPI-I | Master Out Slave In ("MOSI")   |  |  |

| G7       | MIS_out  | SPI-O | Master In Slave Out ("MISO")   |  |  |

| F8       | SPIclock | SPI-I | SPI Clock ("SCK")              |  |  |

| G8       | SPIcs_n  | SPI-I | Chip Select Bar ("/CS", "/SS") |  |  |

| CAES-Only Functions |   |     |                                       |  |  |

|---------------------|---|-----|---------------------------------------|--|--|

| D3                  | - | COB | CAES Use Only – $10K\Omega$ to VSS    |  |  |

| D8                  | - | COB | CAES Use Only - $10K\Omega$ to VSS    |  |  |

| E8                  | - | COB | CAES Use Only - $10K\Omega$ to VDD_25 |  |  |

| F4                  | - | COB | CAES Use Only - $10K\Omega$ to VSS    |  |  |

| F5                  | - | COB | CAES Use Only - No Connect (N/C)      |  |  |

| F6                  | - | COB | CAES Use Only - $10K\Omega$ to VSS    |  |  |

| G5                  | - | COB | CAES Use Only - $10K\Omega$ to VSS    |  |  |

| G6                  | - | COB | CAES Use Only - 10KΩ to VSS           |  |  |

| H7                  | - | COB | CAES Use Only - 10KΩ to VDD_25        |  |  |

|                                   | Power            |     |                                |  |  |  |  |  |

|-----------------------------------|------------------|-----|--------------------------------|--|--|--|--|--|

| C6, C10, E7, E10, H5, J10, K3, K7 | VDD              | VDD | Core Power                     |  |  |  |  |  |

| H6, E6                            | VDDA_BIAS_[1:0]  | VDD | Analog Bias Power 1,0          |  |  |  |  |  |

| K12, J1, D12, C1                  | VDDARX_[3:0] (1) | VDD | Analog CML Receive (RX) Power  |  |  |  |  |  |

| M11, L1, B12, A2                  | VDDATX_[3:0] (1) | VDD | Analog CML Transmit (TX) Power |  |  |  |  |  |

| H12, G1, F12, E1                  | VDDRX_[3:0] (1)  | VDD | CML Receive (RX) Power         |  |  |  |  |  |

| M7, M3, A9, A6                    | VDDTX_[3:0] (1)  | VDD | CML Transmit (TX) Power        |  |  |  |  |  |

| G10                               | VDD_25           | VDD | CMOS Power-SPI Port            |  |  |  |  |  |

| Ground                                                                                                                                                                         |  |     |                                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|--------------------------------|--|--|

| A5, A10, B3, B4, B7, B8, B11, C2,<br>C5, C9, D4, D7, D11, E2, E5, E9,<br>F3, F11, G2, G9, H3, H4, H8, H11,<br>J2, J5, J6, J9, K4, K8, K11, L2, L5,<br>L6, L9, L10, M4, M8, M12 |  | VSS | Transmit, Receive, Core Ground |  |  |

#### Note:

1) There are separate VDDARX, VDDATX, VDDRX, VDDTX pins for each bank. This is indicated by the bus notation suffix: \_[3:0]. All four pins for each bank supply are connected to their respective common power supply.

### 2.2 Pinlist – Package Configuration: Top View

### Table 3. Pin List / Package Configuration

|   | 12           | 11           | 10          | 9           | 8            | 7           | 6                   | 5           | 4           | 3           | 2            | 1            |   |

|---|--------------|--------------|-------------|-------------|--------------|-------------|---------------------|-------------|-------------|-------------|--------------|--------------|---|

| м | VSS          | VDDA<br>TX_3 | TXP<br>_0_3 | TXN<br>_0_3 | VSS          | VDD<br>TX_3 | TXN<br>_3_2         | TXP<br>_3_2 | VSS         | VDD<br>TX_2 | TXN<br>_2_2  | TXP<br>_2_2  | м |

| L | TXP<br>_1_3  | TXN<br>_1_3  | VSS         | VSS         | RXP<br>_0_3  | RXN<br>_0_3 | VSS                 | VSS         | RXN<br>_2_2 | RXP<br>_2_2 | VSS          | VDDA<br>TX_2 | L |

| к | VDDA<br>RX_3 | VSS          | RXP<br>_1_3 | RXN<br>_1_3 | VSS          | VDD         | RXN<br>_3_2         | RXP<br>_3_2 | VSS         | VDD         | TXN<br>_1_2  | TXP<br>_1_2  | к |

| J | TXP<br>_2_3  | TXN<br>_2_3  | VDD         | VSS         | RXP<br>_2_3  | RXN<br>_2_3 | VSS                 | VSS         | RXN<br>_1_2 | RXP<br>_1_2 | VSS          | VDDA<br>RX_2 | J |

| н | VDD<br>RX_3  | VSS          | RXP<br>_3_3 | RXN<br>_3_3 | VSS          | VDD<br>_25  | VDDA<br>_BIAS<br>_1 | VDD         | VSS         | VSS         | TXN<br>_0_2  | TXP<br>_0_2  | н |

| G | TXN<br>_3_3  | TXP<br>_3_3  | VDD<br>_25  | VSS         | SPI<br>cs_n  | MIS<br>_out | VSS                 | VSS         | RXN<br>_0_2 | RXP<br>_0_2 | VSS          | VDD<br>RX_2  | G |

| F | VDD<br>RX_1  | VSS          | RXP<br>_0_1 | RXN<br>_0_1 | SPI<br>clock | MOS<br>_in  | VSS                 | N/C         | VSS         | VSS         | TXN<br>_3_0  | TXP<br>_3_0  | F |

| E | TXP<br>_0_1  | TXN<br>_0_1  | VDD         | VSS         | VDD<br>_25   | VDD         | VDDA<br>_BIAS<br>_0 | VSS         | RXN<br>_3_0 | RXP<br>_3_0 | VSS          | VDD<br>RX_0  | Е |

| D | VDDA<br>RX_1 | VSS          | RXP<br>_1_1 | RXN<br>_1_1 | VSS          | VSS         | RXN<br>_2_0         | RXP<br>_2_0 | VSS         | VSS         | TXN<br>_2_0  | TXP<br>_2_0  | D |

| С | TXP<br>_1_1  | TXN<br>_1_1  | VDD         | VSS         | RXP<br>_3_1  | RXN<br>_3_1 | VDD                 | VSS         | RXN<br>_1_0 | RXP<br>_1_0 | VSS          | VDDA<br>RX_0 | с |

| в | VDDA<br>TX_1 | VSS          | RXP<br>_2_1 | RXN<br>_2_1 | VSS          | VSS         | RXP<br>_0_0         | RXN<br>_0_0 | VSS         | VSS         | TXN<br>_1_0  | TXP<br>_1_0  | В |

| A | TXP<br>_2_1  | TXN<br>_2_1  | VSS         | VDD<br>TX_1 | TXP<br>_3_1  | TXN<br>_3_1 | VDD<br>TX_0         | VSS         | TXN<br>_0_0 | TXP<br>_0_0 | VDDA<br>TX_0 |              | A |

|   | 12           | 11           | 10          | 9           | 8            | 7           | 6                   | 5           | 4           | 3           | 2            | 1            |   |

# 3.0 Absolute Maximum Ratings (1)

### **Table 4: Absolute Maximum Ratings**

| Symbol                        | Parameter                                  | MIN  | MAX  | Units |

|-------------------------------|--------------------------------------------|------|------|-------|

| VDD                           | Core Supply Voltage                        | -0.5 | 1.76 | V     |

| VSS                           | Ground Voltage                             | -0.5 | +0.5 | V     |

| VDDA_BIAS_[1:0]               | Analog Bias Supply Voltage                 | -0.5 | 1.76 | V     |

| VDDARX_[3:0] (2)              | Analog CML Receiver (RX) Supply Voltage    | -0.5 | 1.76 | V     |

| VDDATX_[3:0] (2)              | Analog CML Transmitter (TX) Supply Voltage | -0.5 | 1.76 | V     |

| VDDRX_[3:0] (2)               | CML Receiver (RX) Supply Voltage           | -0.5 | 1.76 | V     |

| VDDTX_[3:0] (2)               | CML Transmitter (TX) Supply Voltage        | -0.5 | 2.65 | V     |

| VDD_25                        | SPI Port Supply Voltage                    | -0.5 | 3.85 | V     |

| IOS_LVCMOS                    | LVCMOS Output Short Circuit Current        | -200 | 200  | mA    |

| VIO_LVCMOS                    | LVCMOS Input / Output Signal Voltage       | -0.5 | 3.85 | V     |

| IINDC_CML                     | DC Input Current, CML Inputs               | -10  | 10   | mA    |

| IINDC_LVCMOS                  | DC Input Current, LVCMOS Inputs            | -10  | 10   | mA    |

| ESD_CML                       | CML ESD Rating (HBM)                       | 1 k  | -    | V     |

| ESD_NON-CML                   | Non-CML ESD Rating (HBM)                   | 2 k  | -    | V     |

| P <sub>D</sub> <sup>(3)</sup> | Maximum Power Dissipation                  |      | 2.5  | W     |

| Θις                           | Thermal Resistance (junction to case)      |      | 10.0 | °C/W  |

| TJ                            | Junction Temperature                       |      | 130  | °C    |

| T <sub>STG</sub>              | Storage Temperature                        | -65  | 125  | °C    |

#### Notes:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification are not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2) There are separate VDDARX, VDDATX, VDDRX, VDDTX pins for each bank. This is indicated by the bus notation suffix: \_[3:0]. All four pins for each bank supply are connected to their respective common power supply.

- 3) Per MIL-STD-883, method 1012.1, section 3.4.1,  $P_{D(PACKAGE)}=(T_{J(max)} T_{C(max)}) / \Theta_{JC}$

### 4.0 Operational Environment

#### **Table 5: Operational Environment**

| Symbol                 | Parameter                                     | Limit               | Units                   |

|------------------------|-----------------------------------------------|---------------------|-------------------------|

| TID <sup>(1)</sup>     | Total Ionizing Dose                           | 1x10 <sup>5</sup>   | rad(Si)                 |

| SEL                    | Single Event Latch-up                         | 100                 | MeV·cm <sup>2</sup> /mg |

| SEU/SEFI               | Single Event Upset (Onset LET)                | 77.7                | MeV·cm <sup>2</sup> /mg |

| SET-BER <sup>(2)</sup> | Single Event Transient induced Bit Error Rate | 7x10 <sup>-17</sup> | errors/dev-day          |

#### Notes:

- 1) Irradiated at dose rate = 50 300 rads (Si)/s in accordance with MIL-STD-883, method 1019, condition A

- 2) Adams 90% Geosynchronous orbit

### **5.0 Recommended Operating Conditions**

#### **Table 6: Recommended Operating Conditions**

| Symbol                          | Parameter                    | Conditions                | MIN  | <b>TYP</b> <sup>(3)</sup> | MAX               | Units |

|---------------------------------|------------------------------|---------------------------|------|---------------------------|-------------------|-------|

| VDD                             | Core Supply Voltage          |                           | 1.14 | 1.2                       | 1.26              | V     |

| VSS                             | Ground Voltage               |                           |      | 0.0                       |                   | V     |

| VDDA_BIAS_[1:0]                 | Analog Bias Supply Voltage   |                           | 1.14 | 1.2                       | 1.26              | V     |

| VDDARX_[3:0] (1)                | Analog CML RX Supply Voltage |                           | 1.14 | 1.2                       | 1.26              | V     |

| VDDATX_[3:0] (1)                | Analog CML TX Supply Voltage |                           | 1.14 | 1.2                       | 1.26              | V     |

| VDDRX_[3:0] (1)                 | CML RX Supply Voltage        |                           | 1.14 | 1.2                       | 1.26              | V     |

| VDDTX_[3:0] (1)                 | CML TX Supply Voltage        |                           | 1.14 | 1.5                       | 1.89              | V     |

| VDD_25                          | SPI Port Supply Voltage      |                           | 2.25 | 2.5                       | 2.75              | V     |

| VIN_CML                         | Input Voltage on any CML pin |                           | 0    |                           | V <sub>DDRX</sub> | V     |

| T <sub>C</sub>                  | Case Temperature Range       |                           | -55  |                           | 105               | °C    |

| t <sub>R</sub> , t <sub>F</sub> | Input Rise or Fall time      | SPI Port Inputs, (20/80%) |      |                           | 3                 | ns    |

#### Note:

1) There are separate VDDARX, VDDATX, VDDRX, VDDTX pins for each bank. This is indicated by the bus notation suffix: \_[3:0]. All four pins for each bank supply are connected to their respective common power supply.

### **6.0 Electrical Characteristics**

### **6.1 DC Electrical Characteristics**

$V_{DD}$ ,  $V_{DDA\_BIAS\_0,1}$ ,  $V_{DDARX}$ ,  $V_{DDATX}=1.2V\pm5\%$ ,  $V_{DDRX}=1.2V\pm5\%$ ,  $V_{DDTX}=1.2V-1.8V\pm5\%$ ,  $V_{DD\_25}=2.5V\pm10\%$ , -55°C $\leq$ Tc $\leq$ +105°C, unless otherwise noted.

### **Table 7: DC Characteristics**

| Symbol                                 | Parameter                                   | Conditions                            | MIN | ТҮР | MAX  | Units |

|----------------------------------------|---------------------------------------------|---------------------------------------|-----|-----|------|-------|

| VIL                                    | SPI Port: Input Logic Low                   |                                       |     |     | 0.8  | V     |

| VIH                                    | SPI Port: Input Logic High                  | -                                     | 1.7 |     |      | V     |

| VOL                                    | SPI Port: Output Logic Low                  | IOL=1mA                               |     |     | 0.25 | V     |

| VOH                                    | SPI Port: Output Logic High                 | IOH=1mA                               | 1.9 |     |      | V     |

| IVDD                                   | Core Supply Current                         |                                       |     | 210 | 500  | mA    |

| IVDDA_BIAS_[1:0]                       | Analog Bias Voltage Current                 |                                       |     | 7.3 | 25   | mA    |

| IVDDARX_[3:0] (1), (2)                 | Analog CML RX Supply Current                | RX Equalization<br>set to 5'b00000    |     |     | 275  | mA    |

| IVDDATX_[3:0] <sup>(1), (2)</sup>      | Analog CML TX Supply Current                | TX Drive<br>Current set to<br>4'b0110 |     |     | 75   | mA    |

| IVDDRX_[3:0] <sup>(1)</sup>            | CML Supply RX Current                       | RX Equalization set to 5'b00000       |     | 208 | 250  | mA    |

| IVDDTX_[3:0] <sup>(1)</sup>            | CML Supply TX Current                       | TX Drive<br>Current set to<br>4'b0110 |     | 208 | 400  | mA    |

| IVDD_25                                | SPI Port Supply Current                     |                                       |     | 10  | 350  | μA    |

| P <sub>D(PWR_DWN)</sub> <sup>(3)</sup> | Power-Down Power Dissipation                |                                       |     | 2.4 | 30   | mW    |

| IIL                                    | LVCMOS SPI Input Leakage<br>Current         |                                       | -1  |     | 1    | μA    |

| IIL2                                   | CML RX Input Leakage Current                |                                       | -1  |     | 1    | μA    |

| IIH                                    | LVCMOS SPI Input Leakage<br>Current         |                                       | -1  |     | 1    | μA    |

| IIH2                                   | CML RX Input Leakage Current                |                                       | -5  |     | 5    | μA    |

| IOZL                                   | LVCMOS SPI High-Z Output<br>Leakage Current |                                       | -1  |     | 1    | μA    |

| IOZH                                   | LVCMOS SPI High-Z Output<br>Leakage Current |                                       | -1  |     | 1    | μA    |

| QIDD_VDD                               | Quiescent Current VDD                       |                                       | 100 |     | 1800 | μA    |

| QIDD_VDDA                              | Quiescent Current VDDA                      |                                       | 40  |     | 300  | μA    |

| QIDD_VDDA_RX_TX                        | Quiescent Current<br>VDDA_RX_TX             |                                       | 100 |     | 800  | μA    |

| QIDD_VDDRX                             | Quiescent Current VDDRX                     |                                       | -60 |     | 60   | μA    |

| QIDD_VDDTX                             | Quiescent Current VDDTX                     |                                       | -60 |     | 60   | μA    |

| QIDD_VDD_25                            | Quiescent Current VDD_25                    |                                       | 50  |     | 200  | μA    |

#### Notes:

- 1) There are separate VDDARX, VDDATX, VDDRX, VDDTX pins for each bank. This is indicated by the bus notation suffix: \_[3:0]. All four pins for each bank supply are connected to their respective common power supply.

- 2) IVDDARX\_[3:0], IVDDATX\_[3:0] parameter values are guaranteed by design.

- 3) Power-down mode: Leakage current only. All circuits powered-down.

### **6.2 AC Electrical Characteristics**

### 6.2.1 AC Electrical Characteristics: Small & Large Signal Parameters

$V_{DD}$ ,  $V_{DDA_BIAS_{0,1}}$ ,  $V_{DDARX}$ ,  $V_{DDATX}$ =1.2V±5%,  $V_{DDRX}$ =1.2V±5%,  $V_{DDTX}$ =1.2V-1.8V±5%,  $V_{DD_{25}}$ =2.5V±10%, -55°C≤T<sub>C</sub>≤+105°C, unless otherwise noted.

### **Table 8: AC Characteristics**

| Symbol                          | Parameter                | Conditions                                                         | MIN | ΤΥΡ  | MAX  | Units |

|---------------------------------|--------------------------|--------------------------------------------------------------------|-----|------|------|-------|

| S <sub>11</sub> <sup>(1)</sup>  | Input Return Loss (RL)   | <1.0 GHz                                                           |     |      | -10  | dB    |

| S <sub>22</sub> <sup>(1)</sup>  | Output Return Loss (RL)  | < 1.0 GHz                                                          |     |      | -10  | dB    |

| C <sub>RX</sub> <sup>(1)</sup>  | RX Pin Capacitance       | Zero Bias, f=1MHz                                                  |     |      | 13   | pF    |

| C <sub>TX</sub> <sup>(1)</sup>  | TX Pin Capacitance       | Zero Bias, f=1MHz                                                  |     |      | 13   | pF    |

| C <sub>SPI</sub> <sup>(1)</sup> | SPI Port Pin Capacitance | Zero Bias, f=1MHz                                                  |     |      | 13   | pF    |

| VI_CML <sup>(2)</sup>           | Input Amplitude, s.e.    | Single Ended, Peak-to-Peak                                         | 100 |      | 800  | mV    |

| VID_CML <sup>(2)</sup>          | Input Amplitude, diff.   | Differential, Peak-to-Peak                                         | 200 |      | 1600 | mV    |

| VO_CML <sup>(2)</sup>           | Output Amplitude, s.e.   | Single Ended, Peak-to-Peak                                         | 200 |      | 600  | mV    |

| VOD_CML <sup>(2)</sup>          | Output Amplitude, diff.  | Differential, Peak-to-Peak                                         | 400 |      | 1200 | mV    |

| Pd(total)                       | Total Power Dissipation  | 3.125Gbps, All lanes, Full<br>Duplex, Medium CML Drive<br>Strength |     | 1.50 | 2.2  | W     |

#### Notes:

- 1) Determined by characterization.

- 2) The high-speed I/O are based on current-mode logic (CML) differential (diff.) signaling. Amplitudes are measured from the diff. signals. Single-ended (s.e.) amplitudes are calculated as one-half of the measured diff. signal amplitude.

### 6.2.2 AC Electrical Characteristics: Timing Parameters

$V_{DD}$ ,  $V_{DDA\_BIAS\_0,1}$ ,  $V_{DDARX}$ ,  $V_{DDATX}$ =1.2V±5%,  $V_{DDRX}$ =1.2V±5%,  $V_{DDTX}$ =1.2V-1.8V±5%,  $V_{DD\_25}$ =2.5V±10%, -55°C≤T<sub>C</sub>≤+105°C, unless otherwise noted.

### **Table 9: Timing Characteristics**

| Symbol                                         | Parameter                     | Conditions              | MIN  | ΤΥΡ | MAX   | Units  |

|------------------------------------------------|-------------------------------|-------------------------|------|-----|-------|--------|

| DR <sup>(1)</sup>                              | Data Rate / Channel           |                         | 0.10 |     | 3.125 | Gbps   |

| t <sub>R</sub> , t <sub>F</sub> <sup>(1)</sup> | Output Rise / Fall Time       | Differential, 20% - 80% |      | 140 |       | ps     |

| T <sub>J</sub> <sup>(1), (2)</sup>             | Total Jitter                  |                         |      |     | 40    | ps,p-p |

| f <sub>CLK</sub>                               | SPI Clock Frequency           | SPI Port                |      |     | 1     | MHz    |

| DCR                                            | SPI Clock Duty Cycle<br>Range | SPI Port                | 40   |     | 60    | %      |

| t <sub>su</sub> ,t <sub>H</sub>                | Set Up & Hold Time            | SPI Port                | 10   |     |       | ns     |

Notes:

- 1) Data Rate (DR), Output rise and fall times ( $t_R$ ,  $t_F$ ), Total Jitter ( $T_J$ ): Characterization only.

- Total Jitter (T<sub>3</sub>): Additive DUT jitter. Optimized by adjusting Receiver (RX) Equalization (EQ) setting. The recommended initial RX equalization EQ setting is 5'b10111.

### 6.3 SPI Port Register Map

#### Table 10: SPI Port Register Map

| Name              | Lane | Bank | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Initial Condition<br>(1/ 0) | Register<br>Address | Register<br>Bit |

|-------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|-----------------|

| Reserved          |      |      | - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1/0                         | hex 00              | [0:7]           |

| Version<br>Number |      |      | Design Version Number - Register<br>ADDRESS hex 01 bits [6:0]. This register<br>ADDRESS is READ ONLY.                                                                                                                                                                                                                                                                                                                                                                                     | 1/0                         | hex 01              | [0:6]           |

| POR Flag          |      |      | The POR Flag is register ADDRESS hex<br>01, bit [7]. The POR Flag is active high. A<br>POR event sets this flag to logic '1'. All<br>other XPS registers will be initialized<br>(RESET) to their default values. A WRITE<br>to register ADDRESS hex 01 will RESET<br>the POR flag to a logic '0'. All other XPS<br>registers will be RESET to their default<br>values, as defined in this Register Map.<br>For a WRITE to register ADDRESS hex 01,<br>the DATA field values don't matter. | 1                           | hex 01              | [7]             |

| Name     | Lane | Bank | Function                          | Initial Condition<br>(1/ 0) | Register<br>Address | Register<br>Bit |

|----------|------|------|-----------------------------------|-----------------------------|---------------------|-----------------|

| RLBS0<0> | 0    | 0    | Reverse Loop-Back, lane 0, bank 0 | 0                           | hex 02              | 0               |

| RLBS0<1> | 1    | 0    | Reverse Loop-Back, lane 1, bank 0 | 0                           |                     | 1               |

| RLBS0<2> | 2    | 0    | Reverse Loop-Back, lane 2, bank 0 | 0                           |                     | 2               |

| RLBS0<3> | 3    | 0    | Reverse Loop-Back, lane 3, bank 0 | 0                           |                     | 3               |

| RLBS1<0> | 0    | 1    | Reverse Loop-Back, lane 0, bank 1 | 0                           |                     | 4               |

| RLBS1<1> | 1    | 1    | Reverse Loop-Back, lane 1, bank 1 | 0                           |                     | 5               |

| RLBS1<2> | 2    | 1    | Reverse Loop-Back, lane 2, bank 1 | 0                           |                     | 6               |

| RLBS1<3> | 3    | 1    | Reverse Loop-Back, lane 3, bank 1 | 0                           |                     | 7               |

| RLBS2<0> | 0    | 2    | Reverse Loop-Back, lane 0, bank 2 | 0                           | hex 03              | 0               |

| RLBS2<1> | 1    | 2    | Reverse Loop-Back, lane 1, bank 2 | 0                           |                     | 1               |

| RLBS2<2> | 2    | 2    | Reverse Loop-Back, lane 2, bank 2 | 0                           |                     | 2               |

| RLBS2<3> | 3    | 2    | Reverse Loop-Back, lane 3, bank 2 | 0                           |                     | 3               |

| RLBS3<0> | 0    | 3    | Reverse Loop-Back, lane 0, bank 3 | 0                           |                     | 4               |

| RLBS3<1> | 1    | 3    | Reverse Loop-Back, lane 1, bank 3 | 0                           |                     | 5               |

| RLBS3<2> | 2    | 3    | Reverse Loop-Back, lane 2, bank 3 | 0                           |                     | 6               |

| RLBS3<3> | 3    | 3    | Reverse Loop-Back, lane 3, bank 3 | 0                           |                     | 7               |

#### Note:

1) Reverse Loop-Back (RLB): RLB=0: NOT ACTIVE, RLB=1: ACTIVE

| Name      | Lane | Bank | Function                                          | Initial Condition<br>(1/ 0) | Register<br>Address | Bit<br>Number |

|-----------|------|------|---------------------------------------------------|-----------------------------|---------------------|---------------|

| EQ_0_0<0> | 0    | 0    | Receiver post equalization, lane 0, bank 0, bit 0 | 0                           | hex 04              | 0             |

| EQ_0_0<1> | 0    | 0    | Receiver post equalization, lane 0, bank 0, bit 1 | 0                           |                     | 1             |

| EQ_0_0<2> | 0    | 0    | Receiver post equalization, lane 0, bank 0, bit 2 | 0                           |                     | 2             |

| EQ_0_0<3> | 0    | 0    | Receiver post equalization, lane 0, bank 0, bit 3 | 1                           |                     | 3             |

| EQ_0_0<4> | 0    | 0    | Receiver post equalization, lane 0, bank 0, bit 4 | 0                           |                     | 4             |

| EQ_0_1<0> | 1    | 0    | Receiver post equalization, lane 1, bank 0, bit 0 | 0                           |                     | 5             |

| EQ_0_1<1> | 1    | 0    | Receiver post equalization, lane 1, bank 0, bit 1 | 0                           |                     | 6             |

| EQ_0_1<2> | 1    | 0    | Receiver post equalization, lane 1, bank 0, bit 2 | 0                           |                     | 7             |

| EQ_0_1<3> | 1    | 0    | Receiver post equalization, lane 1, bank 0, bit 3 | 1                           | hex 05              | 0             |

| EQ_0_1<4> | 1    | 0    | Receiver post equalization, lane 1, bank 0, bit 4 | 0                           |                     | 1             |

| EQ_0_2<0> | 2    | 0    | Receiver post equalization, lane 2, bank 0, bit 0 | 0                           |                     | 2             |

| EQ_0_2<1> | 2    | 0    | Receiver post equalization, lane 2, bank 0, bit 1 | 0                           |                     | 3             |

| EQ_0_2<2> | 2    | 0    | Receiver post equalization, lane 2, bank 0, bit 2 | 0                           |                     | 4             |

| EQ_0_2<3> | 2    | 0    | Receiver post equalization, lane 2, bank 0, bit 3 | 1                           |                     | 5             |

| EQ_0_2<4> | 2    | 0    | Receiver post equalization, lane 2, bank 0, bit 4 | 0                           |                     | 6             |

| EQ_0_3<0> | 3    | 0    | Receiver post equalization, lane 3, bank 0, bit 0 | 0                           |                     | 7             |

| EQ_0_3<1> | 3    | 0    | Receiver post equalization, lane 3, bank 0, bit 1 | 0                           | hex 06              | 0             |

| EQ_0_3<2> | 3    | 0    | Receiver post equalization, lane 3, bank 0, bit 2 | 0                           |                     | 1             |

| EQ_0_3<3> | 3    | 0    | Receiver post equalization, lane 3, bank 0, bit 3 | 1                           |                     | 2             |

| EQ_0_3<4> | 3    | 0    | Receiver post equalization, lane 3, bank 0, bit 4 | 0                           |                     | 3             |

| EQ_1_0<0> | 0    | 1    | Receiver post equalization, lane 0, bank 1, bit 0 | 0                           |                     | 4             |

| EQ_1_0<1> | 0    | 1    | Receiver post equalization, lane 0, bank 1, bit 1 | 0                           |                     | 5             |

| EQ_1_0<2> | 0    | 1    | Receiver post equalization, lane 0, bank 1, bit 2 | 0                           |                     | 6             |

| EQ_1_0<3> | 0    | 1    | Receiver post equalization, lane 0, bank 1, bit 3 | 1                           |                     | 7             |

| EQ_1_0<4> | 0    | 1    | Receiver post equalization, lane 0, bank 1, bit 4 | 0                           | hex 07              | 0             |

| EQ_1_1<0> | 1    | 1    | Receiver post equalization, lane 1, bank 1, bit 0 | 0                           |                     | 1             |

| EQ_1_1<1> | 1    | 1    | Receiver post equalization, lane 1, bank 1, bit 1 | 0                           |                     | 2             |

| EQ_1_1<2> | 1    | 1    | Receiver post equalization, lane 1, bank 1, bit 2 | 0                           |                     | 3             |

| EQ_1_1<3> | 1    | 1    | Receiver post equalization, lane 1, bank 1, bit 3 | 1                           |                     | 4             |

| EQ_1_1<4> | 1    | 1    | Receiver post equalization, lane 1, bank 1, bit 4 | 0                           |                     | 5             |

| EQ_1_2<0> | 2    | 1    | Receiver post equalization, lane 2, bank 1, bit 0 | 0                           |                     | 6             |

| EQ_1_2<1> | 2    | 1    | Receiver post equalization, lane 2, bank 1, bit 1 | 0                           |                     | 7             |

| EQ_1_2<2> | 2    | 1    | Receiver post equalization, lane 2, bank1 , bit 2 | 0                           | hex 08              | 0             |

| EQ_1_2<3> | 2    | 1    | Receiver post equalization, lane 2, bank 1, bit 3 | 1                           |                     | 1             |

| EQ_1_2<4> | 2    | 1    | Receiver post equalization, lane 2, bank 1, bit 4 | 0                           |                     | 2             |

| EQ_1_3<0> | 3    | 1    | Receiver post equalization, lane 3, bank 1, bit 0 | 0                           |                     | 3             |

| EQ_1_3<1> | 3    | 1    | Receiver post equalization, lane 3, bank 1, bit 1 | 0                           |                     | 4             |

| EQ_1_3<2> | 3    | 1    | Receiver post equalization, lane 3, bank 1, bit 2 | 0                           |                     | 5             |

| EQ_1_3<3> | 3    | 1    | Receiver post equalization, lane 3, bank 1, bit 3 | 1                           |                     | 6             |

| EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 0     0     hex 09     0       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 1     0     11       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 2     0     22       Q_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     33       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 4     0     44       EQ_2_1     1     2     Receiver post equalization, lane 1, bank 2, bit 1     0     65       EQ_2_1     1     2     Receiver post equalization, lane 1, bank 2, bit 2     0     77       EQ_2_1     1     2     Receiver post equalization, lane 2, bank 2, bit 4     0     11       EQ_2_2     2     2     Receiver post equalization, lane 2, bank 2, bit 1     0     48       EQ_2_2     2     2     Receiver post equalization, lane 2, bank 2, bit 3     11     55       EQ_2_2     2     2     Receiver post equalization, lane 3, bank 2, bit 4     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EQ_1_3<4> | 3    | 1    | Receiver post equalization, lane 3, bank 1, bit 4                                                      | 0 |        | 7            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|--------------------------------------------------------------------------------------------------------|---|--------|--------------|

| Name     Lane     Bank     Function     (1/0)     Address     Numbe       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 0     0     hex 09     0       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 1     0     2       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_2_0     0     2     Receiver post equalization, lane 0, bank 2, bit 4     0     4       EQ_2_1     1     2     Receiver post equalization, lane 1, bank 2, bit 1     0     6       EQ_2_1     1     2     Receiver post equalization, lane 1, bank 2, bit 2     0     7       EQ_2_1     1     2     Receiver post equalization, lane 1, bank 2, bit 3     1     hex 0A     0       EQ_2_1     1     2     Receiver post equalization, lane 2, bank 2, bit 1     0     2     1       EQ_2_1     1     2     Receiver post equalization, lane 2, bank 2, bit 1     0     4     1       EQ_2_2     2     2     Receiver post equal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |      |      |                                                                                                        |   |        |              |

| EQ_2O<1>     O     2     Receiver post equalization, lane 0, bank 2, bit 1     O     1       EQ_2O<2>     0     2     Receiver post equalization, lane 0, bank 2, bit 2     0     2       EQ_2O<3>     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_2O<3>     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_2O<3>     0     2     Receiver post equalization, lane 1, bank 2, bit 1     0     5       EQ_2O<1     1     2     Receiver post equalization, lane 1, bank 2, bit 2     0     7       EQ_2O<1     1     2     Receiver post equalization, lane 1, bank 2, bit 3     1     hex 0A     0       EQ_2O<1     1     2     Receiver post equalization, lane 2, bank 2, bit 3     0     2     2       EQ_2O<2     2     2     Receiver post equalization, lane 2, bank 2, bit 1     0     6     2       EQ_2O<2     2     2     Receiver post equalization, lane 3, bank 2, bit 3     1     2     2       EQ_2O<2     2     2     Rece                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name      | Lane | Bank | Function                                                                                               |   |        | Bit<br>Numbe |

| EQ_20     0     2     Receiver post equalization, lane 0, bank 2, bit 2     0     2       EQ_20-3>     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_20-3>     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_21-0>     1     2     Receiver post equalization, lane 1, bank 2, bit 1     0     6       EQ_21-12>     1     2     Receiver post equalization, lane 1, bank 2, bit 2     0     7       EQ_21-13>     1     2     Receiver post equalization, lane 1, bank 2, bit 4     0     0     2       EQ_21-13>     1     2     Receiver post equalization, lane 2, bank 2, bit 4     0     0     2       EQ_22-14>     2     Receiver post equalization, lane 2, bank 2, bit 1     0     0     2       EQ_22-21     2     Receiver post equalization, lane 2, bank 2, bit 2     0     4     4       EQ_22-22     2     Receiver post equalization, lane 3, bank 2, bit 0     0     7     7       EQ_23-24>     2     Receiver post equalization, lane 3, bank 2, bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EQ_2_0<0> | 0    | 2    | Receiver post equalization, lane 0, bank 2, bit 0                                                      | 0 | hex 09 | 0            |

| EQ_20<3>     0     2     Receiver post equalization, lane 0, bank 2, bit 3     1     3       EQ_20<4>     0     2     Receiver post equalization, lane 0, bank 2, bit 4     0     4       EQ_21<10>     1     2     Receiver post equalization, lane 1, bank 2, bit 1     0     6       EQ_21<2>     1     2     Receiver post equalization, lane 1, bank 2, bit 2     0     7       EQ_21<2>     1     2     Receiver post equalization, lane 1, bank 2, bit 3     1     hex 0A     0       EQ_21<23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EQ_2_0<1> | 0    | 2    | Receiver post equalization, lane 0, bank 2, bit 1                                                      | 0 |        | 1            |

| EQ_20<4>     0     2     Receiver post equalization, lane 0, bank 2, bit 4     0     4       EQ_21<0>     1     2     Receiver post equalization, lane 1, bank 2, bit 0     0     5       EQ_21<2>     1     2     Receiver post equalization, lane 1, bank 2, bit 1     0     6       EQ_21<3>     1     2     Receiver post equalization, lane 1, bank 2, bit 3     1     hex 0A     0       EQ_21<3>     1     2     Receiver post equalization, lane 1, bank 2, bit 3     1     hex 0A     0       EQ_21<4>     1     2     Receiver post equalization, lane 2, bank 2, bit 4     0     2     2       EQ_22<50>     2     2     Receiver post equalization, lane 2, bank 2, bit 1     0     3     3       EQ_22<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EQ_2_0<2> | 0    | 2    | Receiver post equalization, lane 0, bank 2, bit 2                                                      | 0 |        | 2            |

| EQ.2.1   1   2   Receiver post equalization, lane 1, bank 2, bit 0   0   5     EQ.2.1   1   2   Receiver post equalization, lane 1, bank 2, bit 1   0   6     EQ.2.1   1   2   Receiver post equalization, lane 1, bank 2, bit 2   0   7     EQ.2.1   1   2   Receiver post equalization, lane 1, bank 2, bit 2   0   7     EQ.2.1   1   2   Receiver post equalization, lane 1, bank 2, bit 3   1   hex 0A   0     EQ.2.1   2   2   Receiver post equalization, lane 2, bank 2, bit 0   0   2   2     EQ.2.2   2   2   Receiver post equalization, lane 2, bank 2, bit 1   0   3   3     EQ.2.2   2   2   Receiver post equalization, lane 2, bank 2, bit 3   1   5   5     EQ.2.2   2   2   Receiver post equalization, lane 3, bank 2, bit 3   1   6   6     EQ.2.2   2   2   Receiver post equalization, lane 3, bank 2, bit 1   0   1   6     EQ.2.3   3   2   Receiver post equalization, lane 3, bank 2, bit 3   1   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EQ_2_0<3> | 0    | 2    | Receiver post equalization, lane 0, bank 2, bit 3                                                      | 1 |        | 3            |

| EQ_2.1<1>12Receiver post equalization, lane 1, bank 2, bit 106EQ_2.1<2>12Receiver post equalization, lane 1, bank 2, bit 207EQ_2.1<3>12Receiver post equalization, lane 1, bank 2, bit 31hex 0A0EQ_2.1<3>12Receiver post equalization, lane 1, bank 2, bit 401EQ_2.2<1>22Receiver post equalization, lane 2, bank 2, bit 002EQ_2.2<1>22Receiver post equalization, lane 2, bank 2, bit 103EQ_2.2<2>22Receiver post equalization, lane 2, bank 2, bit 204EQ_2.2<2>22Receiver post equalization, lane 2, bank 2, bit 315EQ_2.2<2>22Receiver post equalization, lane 3, bank 2, bit 406EQ_2.2<2>22Receiver post equalization, lane 3, bank 2, bit 315EQ_2.2<3>22Receiver post equalization, lane 3, bank 2, bit 406EQ_2.3<1>32Receiver post equalization, lane 3, bank 2, bit 10hex 0B0EQ_2.3<1>32Receiver post equalization, lane 3, bank 2, bit 2011EQ_2.3<1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EQ_2_0<4> | 0    | 2    | Receiver post equalization, lane 0, bank 2, bit 4                                                      | 0 |        | 4            |

| EQ_21<2>   1   2   Receiver post equalization, lane 1, bank 2, bit 2   0   7     EQ_21<3>   1   2   Receiver post equalization, lane 1, bank 2, bit 3   1   hex 0A   0     EQ_21<4>   1   2   Receiver post equalization, lane 1, bank 2, bit 4   0   1     EQ_2.2   2   Receiver post equalization, lane 2, bank 2, bit 0   0   2     EQ_2.2   2   Receiver post equalization, lane 2, bank 2, bit 1   0   3     EQ_2.2   2   Receiver post equalization, lane 2, bank 2, bit 2   0   6     EQ_2.2   2   Receiver post equalization, lane 2, bank 2, bit 1   0   6     EQ_2.2   2   Receiver post equalization, lane 3, bank 2, bit 0   0   7     EQ_2.2   3   2   Receiver post equalization, lane 3, bank 2, bit 1   0   hex 0B   0     EQ_2.3   3   2   Receiver post equalization, lane 3, bank 2, bit 1   0   1   2     EQ_2.3   3   2   Receiver post equalization, lane 3, bank 2, bit 1   0   1   2     EQ_3.3   3   2   Receiver post equalization, lane 0, bank 3, b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EQ_2_1<0> | 1    | 2    | Receiver post equalization, lane 1, bank 2, bit 0                                                      | 0 |        | 5            |

| EQ.2.1<3>12Receiver post equalization, lane 1, bank 2, bit 31hex OA0EQ.2.1<4>12Receiver post equalization, lane 1, bank 2, bit 401EQ.2.2<2>22Receiver post equalization, lane 2, bank 2, bit 102EQ.2.2<2>22Receiver post equalization, lane 2, bank 2, bit 103EQ.2.2<2>22Receiver post equalization, lane 2, bank 2, bit 204EQ.2.2<3>22Receiver post equalization, lane 2, bank 2, bit 315EQ.2.2<3>22Receiver post equalization, lane 2, bank 2, bit 306EQ.2.3<2>32Receiver post equalization, lane 2, bank 2, bit 007EQ.2.3<3>32Receiver post equalization, lane 3, bank 2, bit 10hex OB0EQ.2.3<3>32Receiver post equalization, lane 3, bank 2, bit 2012EQ.2.3<3>32Receiver post equalization, lane 3, bank 2, bit 3122EQ.2.3<3>32Receiver post equalization, lane 3, bank 2, bit 4033EQ.2.3<3>32Receiver post equalization, lane 3, bank 2, bit 404EQ.2.3<3>32Receiver post equalization, lane 3, bank 3, bit 004EQ.3.03Receiver post equalization, lane 0, bank 3, bit 105EQ.3.03Receiver post equalization, lane 0, bank 3, bit 102 <tr< td=""><td>EQ_2_1&lt;1&gt;</td><td>1</td><td>2</td><td>Receiver post equalization, lane 1, bank 2, bit 1</td><td>0</td><td></td><td>6</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EQ_2_1<1> | 1    | 2    | Receiver post equalization, lane 1, bank 2, bit 1                                                      | 0 |        | 6            |

| EQ_21<4>   1   2   Receiver post equalization, lane 1, bank 2, bit 4   0   1     EQ_22<>>   2   Receiver post equalization, lane 2, bank 2, bit 0   0   2     EQ_22<>>   2   Receiver post equalization, lane 2, bank 2, bit 1   0   3     EQ_22<>>   2   Receiver post equalization, lane 2, bank 2, bit 2   0   4     EQ_22<>>   2   Receiver post equalization, lane 2, bank 2, bit 3   1   5     EQ_22<>>   2   Receiver post equalization, lane 2, bank 2, bit 4   0   6     EQ_23<>   2   Receiver post equalization, lane 3, bank 2, bit 0   0   7     EQ_23   3   2   Receiver post equalization, lane 3, bank 2, bit 1   0   hex 0B   0     EQ_23   3   2   Receiver post equalization, lane 3, bank 2, bit 2   0   1   1   2     EQ_23   3   2   Receiver post equalization, lane 3, bank 2, bit 3   1   2   2     EQ_3   3   2   Receiver post equalization, lane 0, bank 3, bit 0   0   4     EQ_3   0   3   Receiver post equalization, lane 0, bank 3, bit 1   0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EQ_2_1<2> | 1    | 2    | Receiver post equalization, lane 1, bank 2, bit 2                                                      | 0 |        | 7            |

| EQ_2_2<0>   2   2   Receiver post equalization, lane 2, bank 2, bit 0   0   2     EQ_2_2<1>   2   2   Receiver post equalization, lane 2, bank 2, bit 1   0   3     EQ_2_2<2>   2   2   Receiver post equalization, lane 2, bank 2, bit 2   0   4     EQ_2_2<3>   2   2   Receiver post equalization, lane 2, bank 2, bit 3   1   5     EQ_2_3<4>   2   2   Receiver post equalization, lane 3, bank 2, bit 4   0   6     EQ_2_3<4>   3   2   Receiver post equalization, lane 3, bank 2, bit 1   0   hex 0B   0     EQ_2_3<1>   3   2   Receiver post equalization, lane 3, bank 2, bit 2   0   11     EQ_2_3<2>   3   2   Receiver post equalization, lane 3, bank 2, bit 4   0   3     EQ_2_3<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EQ_2_1<3> | 1    | 2    | Receiver post equalization, lane 1, bank 2, bit 3                                                      | 1 | hex 0A | 0            |