# UT54ACS3G99S

### Features

- Voltage Supply: 3.0V to 5.5V

- Advanced CMOS technology

- Schmitt Trigger Inputs

- Tri-State Outputs

- ESD rating HBM: 2000V, Class 2

- Operational environment:

- Total dose: 1 Mrad(Si)

- Latchup immune (LET <= 100 MeV-cm<sup>2</sup>/mg)

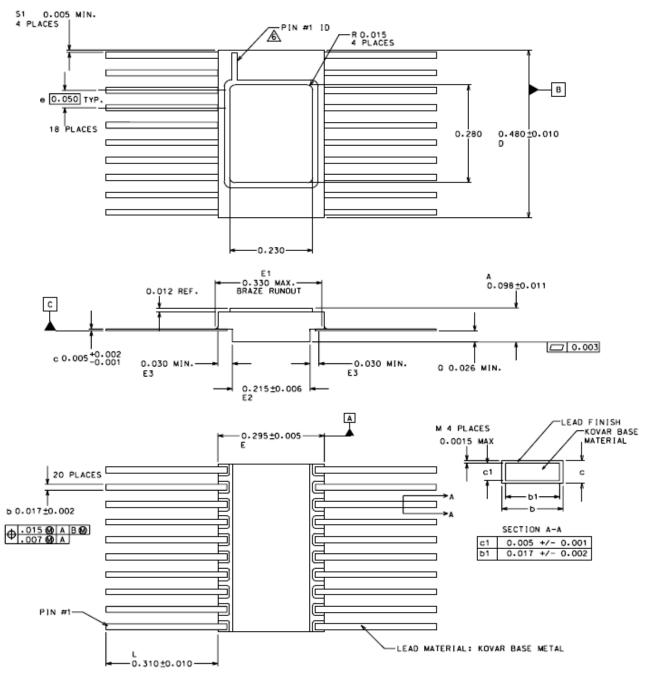

- Packaging:

- 20-lead flatpack

- Standard Microelectronics Drawing (SMD) 5962-15238

- QML Q, V

### Introduction

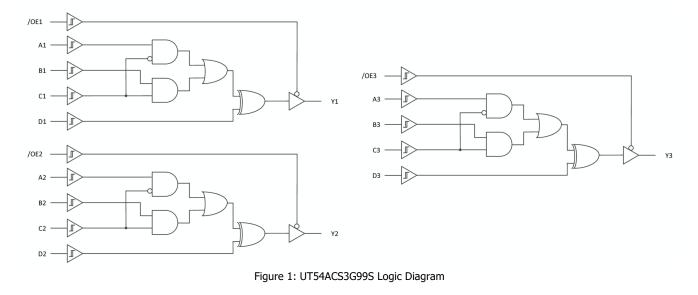

The UT54ACS3G99S is CAES Triple, Combinatorial, ManyGate Configurable Logic Gate with Schmitt Trigger inputs and Tri-State outputs. The output-enable pin /OEn is active LOW. The sixteen possible combinations of the four inputs An-Dn determine one of sixteen Yn output states when /OEn is LOW=VSS. The outputs Yn are disabled when /OEn is HIGH=VDD.

The ManyGate device logic functions are pin configurable by applying either a logic HIGH (VDD) or LOW (VSS) to the logic input pins as noted. Three identical, independently configurable combinatorial logic blocks are included in the UT54ACS3G99S, as shown in the logic diagram of Figure 1. The nine basic Boolean logic functions in each logic block are listed here as follows: AND, NAND, OR, NOR, XOR, XNOR, MUX, inverter, and buffer. All sixteen logic functions are described in Tables 2-9.

The UT54ACS3G99S triple, configurable, combinatorial logic gate is available in a small form factor, 20-lead ceramic flatpack and operates on a power supply range of 3.0V to 5.5V.

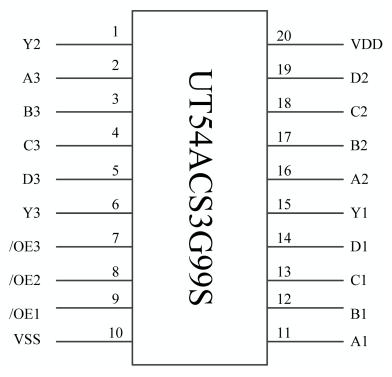

## **1** Pin Definition/Description

### Table 1. Pin Naming

| Pin No.   | Name            | Description              |

|-----------|-----------------|--------------------------|

| 7, 8, 9   | /OEn            | Active LOW output enable |

| 2, 11, 16 | An              | A input                  |

| 3, 12, 17 | Bn              | B input                  |

| 4, 13, 18 | Cn              | C input                  |

| 5, 14, 19 | Dn              | D input                  |

| 1, 6, 15  | Yn              | 3-State Output           |

| 20        | V <sub>DD</sub> | Power supply pin         |

| 10        | V <sub>SS</sub> | Ground pin               |

Figure 2: UT54ACS3G99S Pinout Diagram

## UT54ACS3G99S

### 2 Functional Truth Tables and Operational Modes

### Table 2. Combinatorial Truth Table An, Bn, Cn, Dn to n=1,2,3 of Storage Element Yn Output

| Dn | Cn | Bn | An | Output to D <sub>IN</sub> |

|----|----|----|----|---------------------------|

| L  | L  | L  | L  | L                         |

| L  | L  | L  | Н  | Н                         |

| L  | L  | Н  | L  | L                         |

| L  | L  | Н  | н  | Н                         |

| L  | Н  | L  | L  | L                         |

| L  | Н  | L  | Н  | L                         |

| L  | Н  | Н  | L  | Н                         |

| L  | Н  | Н  | Н  | Н                         |

| Н  | L  | L  | L  | Н                         |

| Н  | L  | L  | Н  | L                         |

| Н  | L  | Н  | L  | Н                         |

| Н  | L  | Н  | Н  | L                         |

| Н  | Н  | L  | L  | Н                         |

| Н  | Н  | L  | н  | Н                         |

| Н  | Н  | Н  | L  | L                         |

| Н  | Н  | Н  | н  | L                         |

### **3 Applications Information**

### Table 3. Equivalent Logic Functions Created from Table 2

| Primary Logic Function                         | Complementary Logic Function              | Table |

|------------------------------------------------|-------------------------------------------|-------|

| 3-state buffer                                 |                                           | 4     |

| 3-state inverter                               |                                           | 5     |

| 3-state 2-in-1 data selector MUX               |                                           | 6     |

| 3-state 2-in-1 data selector MUX, inverted out |                                           | 6     |

| 3-state 2-input AND                            | 3-state 2-input NOR, both inputs inverted | 7     |

| 3-state 2-input AND, one input inverted        | 3-state 2-input NOR, one input inverted   | 7     |

| 3-state 2-input AND, both inputs inverted      | 3-state 2-input NOR                       | 7     |

| 3-state 2-input NAND                           | 3-state 2-input OR, both inputs inverted  | 8     |

| 3-state 2-input NAND, one input inverted       | 3-state 2-input OR, one input inverted    | 8     |

| 3-state 2-input NAND, both inputs inverted     | 3-state 2-input OR                        | 8     |

| 3-state 2-input XOR, both inputs inverted      |                                           | 9     |

# UT54ACS3G99S

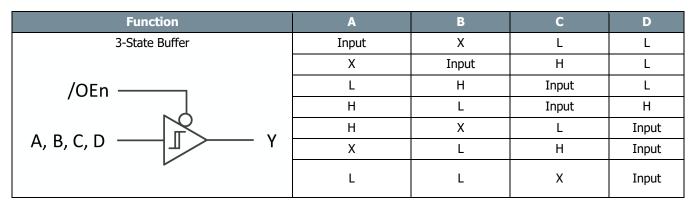

### **Table 4. 3-State Buffer Functions**

### **Table 5. 3-State Inverter Buffer Functions**

| Function                | Α     | В     | С     | D     |

|-------------------------|-------|-------|-------|-------|

|                         | Input | Х     | L     | Н     |

| 3-State inverter buffer | Х     | Input | Н     | Н     |

|                         | L     | Н     | Input | Н     |

|                         | Н     | L     | Input | L     |

| /OEn                    | Н     | Х     | L     | Input |

|                         | Х     | Н     | Н     | Input |

| A, B, C, D Y            | н     | н     | Х     | Input |

# UT54ACS3G99S

### Table 6. 3-State MUX Functions

| Function                                                       | Α                  | В                  | С                  | D |

|----------------------------------------------------------------|--------------------|--------------------|--------------------|---|

| 3-State 2-to-1, Data Selector Mux<br>A/B<br>Input 1<br>Input 2 | Input 1 or Input 2 | Input 1 or Input 2 | Input 1 or Input 2 | L |

| 3-State 2-to-1, Data Selector Mux,<br>Inverted Out             | Input 1 or Input 2 | Input 1 or Input 2 | Input 1 or Input 2 | Н |

## UT54ACS3G99S

### Table 7. 3-State AND/NOR Functions

| #IN | AND                                      | NOR                            | А                  | В                  | С                  | D      |

|-----|------------------------------------------|--------------------------------|--------------------|--------------------|--------------------|--------|

| 2   | /OEn<br>INPUT1                           | /OEn<br>INPUT1 INPUT2 Y        | L                  | Input 1<br>Input 2 | Input 2<br>Input 1 | L<br>L |

| 2   | /OEn<br>INPUT1 O J<br>INPUT2 V           | /OEn<br>INPUT1<br>INPUT2<br>Or | Input 2<br>H       | L<br>Input 1       | Input 1<br>Input 2 | L<br>H |

| 2   | /OEn<br>INPUT1                           | /OEn<br>INPUT1 J Y<br>INPUT2 Y | Input 1<br>H       | L<br>Input 2       | Input 2<br>Input 1 | L<br>H |

| 2   | /OEn<br>INPUT1 - O I Y<br>INPUT2 - O I Y | /OEn<br>INPUT1<br>INPUT2       | Input 1<br>Input 2 | H<br>H             | Input 2<br>Input 1 | H<br>H |

## UT54ACS3G99S

### Table 8. 3-State NAND/OR Functions

| #IN | NAND                                                 | OR                               | Α                  | В                  | С                  | D      |

|-----|------------------------------------------------------|----------------------------------|--------------------|--------------------|--------------------|--------|

| 2   | /OEn<br>INPUT1                                       | /OEn<br>INPUT1 INPUT2 Y          | L                  | Input 1<br>Input 2 | Input 2<br>Input 1 | H<br>H |

| 2   | /OEn<br>INPUT1O Y<br>INPUT2 Y                        | /OEn<br>INPUT1 J Y<br>INPUT2 J Y | Input 2<br>H       | L<br>Input 1       | Input 1<br>Input 2 | H<br>L |

| 2   | /OEn<br>INPUT1                                       | /OEn<br>INPUT1 J Y<br>INPUT2 Y   | Input 1<br>H       | L<br>Input 2       | Input 2<br>Input 1 | H<br>L |

| 2   | /OEn<br>INPUT1 - C J<br>INPUT2 - C J<br>INPUT2 - C J | /OEn<br>INPUT1 I I Y<br>INPUT2 Y | Input 1<br>Input 2 | H                  | Input 2<br>Input 1 | L<br>L |

## UT54ACS3G99S

### Table 9. 3-State XOR/XNOR Functions

| #IN | XOR/XNOR Function                  | Α                  | В                  | С                  | D                  |

|-----|------------------------------------|--------------------|--------------------|--------------------|--------------------|

|     | 2<br>INPUT1<br>INPUT2<br>Y         | Input 1<br>Input 2 | X<br>X             | L                  | Input 2<br>Input 1 |

| 2   |                                    | X<br>X             | Input 1<br>Input 2 | H<br>H             | Input 2<br>Input 1 |

|     |                                    | L                  | H<br>H             | Input 1<br>Input 2 | Input 2<br>Input 1 |

| 2   | /OEn<br>INPUT1 V<br>INPUT2 Y       | н                  | L                  | Input 1            | Input 2            |

| 2   | /OEn<br>INPUT1<br>INPUT2<br>INPUT2 | н                  | L                  | Input 1            | Input 2            |

| 2   | /OEn<br>INPUT1<br>INPUT2           | H<br>H             | L                  | Input 1<br>Input 2 | Input 2<br>Input 1 |

## **4 Operational Environment**

### Table 10. Radiation

| Parameter                    | Limit  | Units                   |

|------------------------------|--------|-------------------------|

| Total Ionizing Dose (TID)    | 1.0E6  | rad(Si)                 |

| Single Event Latchup (SEL)   | >100   | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence <sup>1</sup> | 1.0E13 | n/cm <sup>2</sup>       |

#### Note:

1) Guaranteed by Characterization

### **5 Absolute Maximum Ratings**

### Table 11. Absolute Maximum Ratings Table<sup>1</sup>

| Symbol                      | Parameter                                               | Limit                            | Unit |

|-----------------------------|---------------------------------------------------------|----------------------------------|------|

| V <sub>DD</sub>             | Positive Output Supply Voltage                          | -0.3 to 7.0                      | V    |

| V <sub>IO</sub>             | Voltage on an Input pin during operation                | -0.3 to (V <sub>DD</sub> + 0.3V) | V    |

| I <sub>I/O</sub>            | DC input/output Current                                 | +/-10                            | mA   |

| Θ <sub>JC</sub>             | Thermal resistance, junction-to-case                    | 15                               | °C/W |

| Tյ                          | Junction Temperature <sup>2</sup>                       | +175°C                           | °C   |

| T <sub>STG</sub>            | Storage Temperature                                     | -65°C to+150°C                   | °C   |

| P <sub>D</sub> <sup>3</sup> | Maximum package power dissipation permitted at Tc=125°C | 1                                | w    |

#### Notes:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2) Maximum junction temperature may be increased to +175°C during burn-in and life test.

- 3) Test per MIL-STD-883, Method 1012.

### **6 Recommended Operating Conditions**

### **Table 12. Recommended Operating Conditions**

| Symbol                          | Parameter                      | Limit                  | Unit |

|---------------------------------|--------------------------------|------------------------|------|

| V <sub>DD</sub>                 | Positive Output Supply Voltage | 3.0 to 5.5             | V    |

| V <sub>IN</sub>                 | Input Voltage on any pin       | 0.0 to $V_{\text{DD}}$ | V    |

| Тс                              | Case Temperature Range         | -55 to +125            | °C   |

| t <sub>R</sub> , t <sub>F</sub> | Input Rise/Fall time (20%/80%) | <1                     | sec  |

# UT54ACS3G99S

### 7 3.3V DC Characteristics

(V<sub>DD</sub>=  $3.3V \pm 0.3V$ ,  $-55^{\circ}C < Tc < +125^{\circ}C$ ); Unless otherwise noted, Tc is per the temperature range ordered

For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured

### Table 13. 3.3V DC Electrical Characteristics Table<sup>1,3,4</sup>

| Symbol                          | Parameter                                              | Condition                                                                                                                                                | MIN                    | MAX                 | Unit   |

|---------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|--------|

| $V_{T+}$                        | Positive going input voltage threshold <sup>1</sup>    |                                                                                                                                                          |                        | 0.7*V <sub>DD</sub> | V      |

| V <sub>T</sub> -                | Negative going input voltage threshold <sup>1</sup>    |                                                                                                                                                          | 0.3*V <sub>DD</sub>    |                     | V      |

| V <sub>H</sub>                  | Hysteresis Voltage                                     |                                                                                                                                                          | 0.3                    |                     | V      |

| V <sub>OL</sub> <sup>2</sup>    | Low-level output voltage                               | $I_{OL} = 100 \mu A$ V_DD from 3.0V to 3.6V                                                                                                              |                        | 0.25                | V      |

| V <sub>OH</sub> <sup>2</sup>    | High-level output voltage                              | $I_{OH} = -100 \mu A \label{eq:IOH} V_{DD} \text{ from 3.0V to 3.6V}$                                                                                    | V <sub>DD</sub> – 0.25 |                     | V      |

| $\mathrm{I}_{\mathrm{IN}}$      | Input leakage current                                  | $V_{IN} = V_{DD} \text{ or GND},$ $V_{DD} = 0.0V \text{ to } 3.6V$                                                                                       | -1                     | +1                  | μA     |

| I <sub>OS</sub> <sup>3, 4</sup> | Output Short Circuit Current                           | $V_{OUT} = V_{DD} + V_{SS}$                                                                                                                              | -200                   | +200                | mA     |

| IoL <sup>5</sup>                | Low level output current (sink)                        | $V_{IN} = V_{DD} \text{ or } V_{SS}$ $V_{OL} = 0.4V$ $V_{DD} \text{ from } 3.0V \text{ to}$ $3.6V$                                                       | 8                      |                     | mA     |

| I <sub>OH</sub> 5               | High level output current (source)                     | $\label{eq:VIN} \begin{array}{l} V_{IN} = V_{DD} \text{ or } V_{SS} \\ V_{OH} = V_{DD} - 0.4V \\ V_{DD} \text{ from } 3.0V \text{ to } 3.6V \end{array}$ | -8                     |                     | mA     |

| I <sub>oz</sub>                 | Output Three-State Current                             | Device Enabled,<br>$V_{OUT} = 0V \text{ or } V_{DD},$<br>$V_{DD} = 3.6V$                                                                                 | -5                     | +5                  | μA     |

|                                 | Quiescent Supply Current Pre-Rad (Device Type 01 & 02) |                                                                                                                                                          |                        | 10                  | μA     |

| $\mathbf{I}_{DDQ}$              | Quiescent Supply Current Post-Rad (Device Type 01)     | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{DD} = V_{DD} \text{ MAX}$                                                                                    |                        | 25                  | μA     |

|                                 | Quiescent Supply Current Post-Rad (Device Type 02)     | איזיי טעי – טעי                                                                                                                                          |                        | 130                 | μA     |

| Ptotal <sup>5,6</sup>           | Power dissipation                                      | $C_L = 78 pF$                                                                                                                                            |                        | 3.0                 | mW/MHz |

| $C_{IN}^{6}$                    | Input capacitance                                      |                                                                                                                                                          |                        | 15                  | pF     |

| C <sub>OUT</sub> <sup>7</sup>   | Output capacitance                                     |                                                                                                                                                          |                        | 15                  | pF     |

#### Notes:

- Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, -0%; VIL = VIL(max) + 0%, 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to VIH(min) and VIL(max).

- Per MIL-PRF-38535, for current density <= 5.0E5 amps/cm<sup>2</sup>, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765pF/MHz.

- 3) Supplied as a design limit but not guaranteed or tested.

- 4) Not more than one output may be shorted at a time for maximum duration of one second.

- 5) Guaranteed by characterization but not tested.

- 6) Power dissipation specified per switching output.

- 7) Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and Vss at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

### 8 5.0V DC Characteristics

$(V_{DD} = 5.0V \pm 0.5V, -55^{\circ}C < TC < +125^{\circ}C)$ ; Unless otherwise noted, Tc is per the temperature range ordered

### Table 14. 5V DC Electrical Characteristics Table<sup>1,3,4</sup>

| Symbol                          | Parameter                                                                                                                                                                                                    | Condition                                                                                            | MIN                    | MAX                 | Unit   |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------|---------------------|--------|

| $V_{T+}$                        | Positive going input voltage threshold <sup>1</sup>                                                                                                                                                          |                                                                                                      |                        | 0.7*V <sub>DD</sub> | V      |

| V <sub>T</sub> -                | Negative going input voltage threshold <sup>1</sup>                                                                                                                                                          |                                                                                                      | 0.3*V <sub>DD</sub>    |                     | V      |

| V <sub>H</sub>                  | Hysteresis Voltage                                                                                                                                                                                           |                                                                                                      | 0.3                    |                     | V      |

| $V_{OL}^2$                      | Low-level output voltage                                                                                                                                                                                     | $I_{\text{OL}} = 100 \mu\text{A}; \label{eq:VDD} \ \text{from 5.0V to 5.5V}$                         |                        | 0.25                | V      |

| V <sub>OH</sub> <sup>2</sup>    | High-level output voltage $I_{OH} = -100 \mu A$ V_{DD} from 5.0V to                                                                                                                                          |                                                                                                      | V <sub>DD</sub> – 0.25 |                     | V      |

| $\mathbf{I}_{\text{IN}}$        | Input leakage current $V_{IN} = V_{DD} \text{ or GND}; \\ V_{DD} = 5.0V \text{ to } 5.5V $ -1                                                                                                                |                                                                                                      | +1                     | μA                  |        |

| I <sub>OS</sub> <sup>3, 4</sup> | Output Short Circuit Current $V_{OUT} = V_{DD} + VSS$ -300                                                                                                                                                   |                                                                                                      | -300                   | +300                | mA     |

| $I_{OL}{}^5$                    | $ \label{eq:low_level} \text{Low level output current (sink)} \qquad \begin{array}{c} V_{IN} = V_{DD} \text{ or } V_{SS}; \\ V_{OL} = 0.4V; \\ V_{DD} \text{ from } 5.0V \text{ to } 5.5V \end{array}  -12 $ |                                                                                                      |                        | mA                  |        |

| I <sub>OH</sub> 5               | High level output current (source)                                                                                                                                                                           | Device Enabled;<br>$V_{OUT} = 0V \text{ or } V_{DD};$<br>$V_{DD} = 5.5V$<br>$V_{OH} = V_{DD} - 0.4V$ | 12                     |                     | mA     |

| I <sub>OZ</sub>                 | Output Three-State Current                                                                                                                                                                                   | $V_{IN} = V_{DD}$ or $V_{SS}$ ;<br>$V_{DD}$ from 5.0V to 5.5V                                        | -5                     | +5                  | μA     |

|                                 | Quiescent Supply Current Pre-Rad (Device Type 01 & 02)                                                                                                                                                       | $V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{DD} = V_{DD} \text{ MAX}$                                |                        | 10                  | μA     |

| $\mathbf{I}_{DDQ}$              | Quiescent Supply Current Post-Rad (Device Type 01)                                                                                                                                                           |                                                                                                      |                        | 25                  | μA     |

|                                 | Quiescent Supply Current Post-Rad (Device Type 02)                                                                                                                                                           |                                                                                                      |                        | 130                 | μA     |

| Ptotal <sup>5,6</sup>           | Power dissipation <sup>5, 6</sup>                                                                                                                                                                            | $C_L = 78 pF$                                                                                        |                        | 3.0                 | mW/MHz |

| $C_{IN}^{6}$                    | Input capacitance                                                                                                                                                                                            |                                                                                                      |                        | 15                  | pF     |

| C <sub>OUT</sub> <sup>7</sup>   | Output capacitance                                                                                                                                                                                           |                                                                                                      |                        | 15                  | pF     |

#### Notes:

- 1) Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, 0%; VIL = VIL(max) + 0%, 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to VIH(min) and VIL(max).

- 2) Per MIL-PRF-38535, for current density <=5.0E5 amps/cm2, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765pF/MHz.

- 3) Supplied as a design limit but not guaranteed or tested.

- 4) Not more than one output may be shorted at a time for maximum duration of one second.

- 5) Guaranteed by characterization but not tested.

- 6) Power dissipation specified per switching output.

- 7) Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and VSS at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

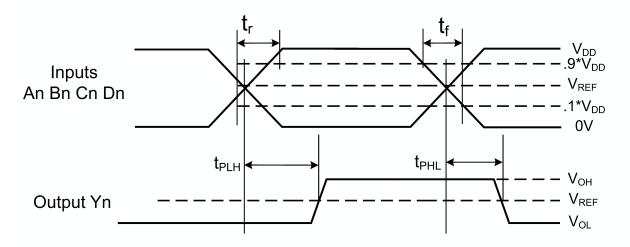

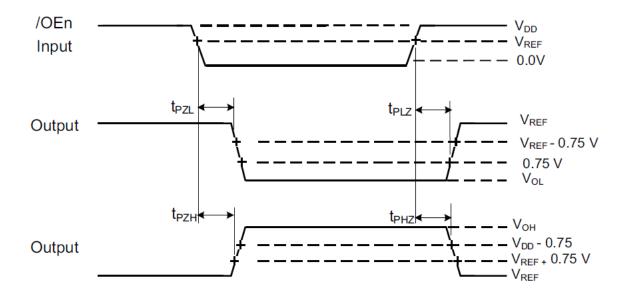

### **9 AC Electrical Characteristics**

(V<sub>DD</sub>= 3.0V to 5.5V, -55°C < Tc < +125°C); Unless otherwise noted, Tc is per the temperature range ordered

### Table 15. AC Electrical Table for the 3G99S

| Symbol           | Parameter                   | Condition    | Minimum | Maximum | Unit |

|------------------|-----------------------------|--------------|---------|---------|------|

| tplh             | A, B, C, Dn to Yn           | 3.0V to 3.6V |         | 18.5    | ns   |

|                  |                             | 4.5V to 5.5V |         | 13      | ns   |

| t <sub>PHL</sub> | A, B, C, Dn to Yn           | 3.0V to 3.6V |         | 20.5    | ns   |

|                  |                             | 4.5V to 5.5V |         | 15      | ns   |

| t <sub>PZL</sub> | /OEn low to Yn              | 3.0V to 3.6V |         | 13.5    | ns   |

|                  |                             | 4.5V to 5.5V |         | 9.5     | ns   |

| t <sub>PZH</sub> | /OEn low to Yn              | 3.0V to 3.6V |         | 14.5    | ns   |

|                  |                             | 4.5V to 5.5V |         | 10.5    | ns   |

| +                | /OEn high to Yn three-state | 3.0V to 3.6V |         | 12      | ns   |

| t <sub>PLZ</sub> |                             | 4.5V to 5.5V |         | 10      | ns   |

| t                | /OEn high to Yn three-state | 3.0V to 3.6V |         | 16      | ns   |

| t <sub>PHZ</sub> |                             | 4.5V to 5.5V |         | 13      | ns   |

Note:

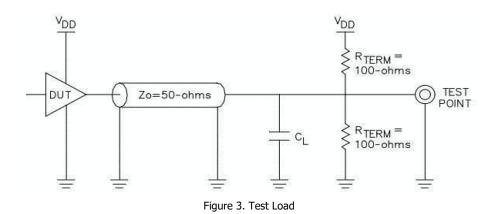

1) CL = 78 pF minimum or equivalent (includes scope probe and test socket). Measurement of data output occurs at the low to high or high to low transition mid-point, typically VDD/2.

## UT54ACS3G99S

## **Propagation Delay**

## **Enable/Disable Times**

Figure 4. Timing Diagram

- 1)  $V_{REF} = V_{DD}/2$

- 2)  $C_L$  = 78 pF or equivalent (includes probe and jig capacitance).

- 3)  $I_{\text{SRC}}$  is set to -1 mA and  $I_{\text{SNK}}$  is set to +1 mA for  $t_{\text{PHL}}$  and  $t_{\text{PLH}}$  measurements.

- 4) Input signal from pulse generator:  $V_{IN} = 0.0V$  to  $V_{DD}$ ; f  $\leq$  10 MHz; tr = 1.0 ns/V ±0.3 ns/V ±0.3 ns/V; tr and tf shall be measured from0.1  $V_{DD}$  to 0.9  $V_{DD}$  and from 0.9  $V_{DD}$  to 0.1  $V_{DD}$ , respectively.

- 5) Equivalent tst circuit means that DUT performance will be correlated and remain guaranteed to the applicable test circuit, above, whenever a test platform change necessitates a deviation from the applicable test circuit.

**RELEASED 4/16**

Triple ManyGate Configurable Logic Gate

## UT54ACS3G99S

- 1) All exposed metalized areas must be gold plated over electrically plated nickel per MIL-PRF-38535.

- 2) The lid is electrically connected to VSS.

- 3) Lead finishes are in accordance with MIL-PRF-38535.

- 4) Dimensions symbology is in accordance with MIL-PRF-38535.

- 5) Lead position and coplanarity are not measured

- 6) ID mark symbol is vendor option: No Alphanumerics.

# UT54ACS3G99S

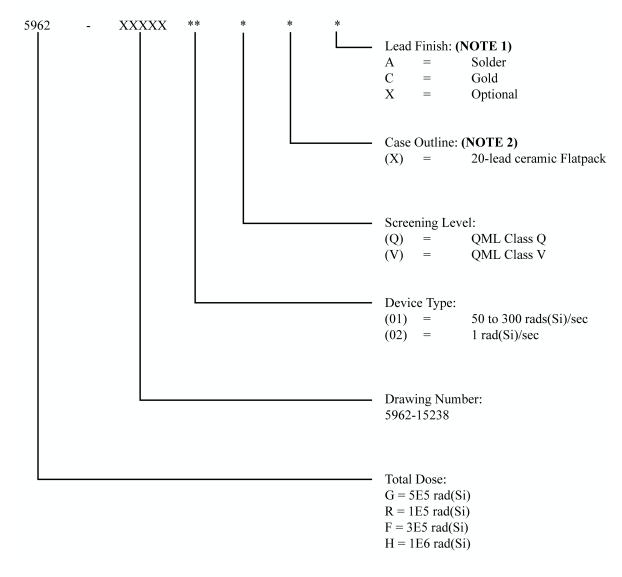

- 1) Lead finish (A, C, or X) must be specified.

- 2) If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Prototype flow per CAES Manufacturing Flows Document. Tested at 25°C only. Lead finish is GOLD ONLY. Radiation neither tested nor guaranteed.

- 4) HiRel Temperature Range flow per CAES Manufacturing Flows Document. Devices are tested at -55°C, room temp, and +125°C. Radiation neither tested nor guaranteed.

# UT54ACS3G99S

## 11 UT54ACS3G99S ManyGate<sup>™</sup> Logic Gate: SMD

- 1) Lead finish (A, C, or X) must be specified.

- 2) If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3) Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening. For prototype inquiries, contact factory.

- 4) Device Type 02 is only offered with a TID tolerance guarantee of 1E6 rads(Si) and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A and section 3.11.2. Device type 01 is only offered with a TID tolerance guarantee of 1E5 rads(Si), 3E5 rads(Si), and 5E5 rads(Si), and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A.

# UT54ACS3G99S

## **Data Sheet Revision History**

| REV   | <b>Revision Date</b> | Description of Change                                                      | Page(s)     | Author |

|-------|----------------------|----------------------------------------------------------------------------|-------------|--------|

| 0.1.0 | 7/15                 | Posted Advanced Datasheet                                                  |             | Massey |

| 0.2.0 | 10/15                | Table 7-8-9 edits to existing logic diagrams. Added to Introduction.       | 1-6-7-8     | Massey |

| 0.3.0 | 12/15                | Added Device Type 02 to the DC Characteristics table and order information | 10-11-12-16 | Massey |

| 0.4.0 | 1/16                 | Replaced Figure 3                                                          | 12          | Massey |

| 1.0.0 | 4/16                 | QML Q&V qualified                                                          | 1 Massey    |        |

## Datasheet Definitions

|                       | DEFINITION                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet <b>is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                             |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.