#### Features

- Single 3.3 V Supply Voltage (3.0 V to 3.6 V)

- System

- A rm<sup>®</sup> C ortex<sup>®</sup> M0+

- Arm<sup>®</sup> Cortex<sup>®</sup> M0+ built-in NVIC

- Digital and Communication Peripherals

- 2x CAN 2.0BControllers

- 2x UART

- SPI

- 2x I2C

- JTAG

- 4x General purpose timers

- 3x PWM

- Watchdog Timer

- Real Time Clock

- 48x GPIO (21 dedicated)

- 8x Hardware Interrupts (shared with GPIO)

- Analog Peripherals

- 12-bit A DC 100 ksps with PGA

- 16 Single Ended or 8 Differential Channels

- 1 mA Precision Current Source

- 2x 12-bit DACs

- 2x A nalog Voltage Comparators

- Temperature Sensor

- Power Control

- Multiple power modes for low power optimization

- System clock scalable for low power

- Memories

- 96KB Dual Port SRAM with EDAC + Scrubbing

- 64Mb Flash Memory

- 384KB in 96KB increments for user firmware

- ClockGeneration

- 50 MHz internal clock factory -trimmed RC

- Support for external clock source and crystal oscillator

- Offered in the CAES Constellation process flow, which includes tri-temp testing and radiation assurance, in the same packaging

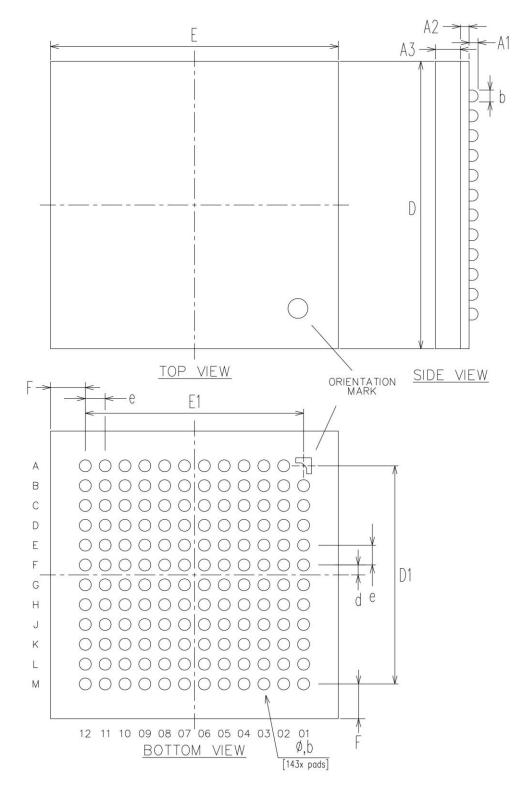

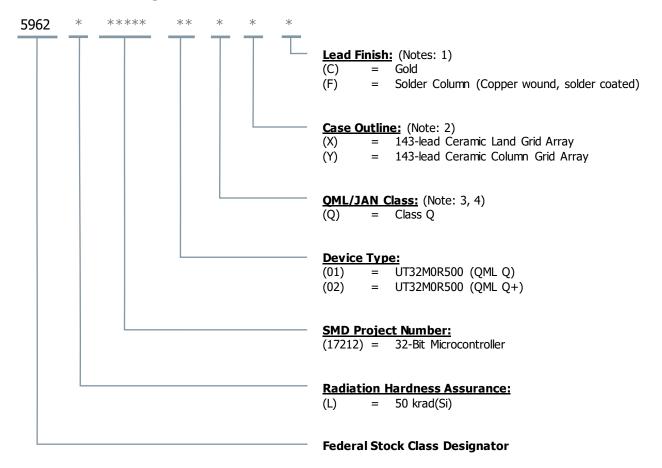

- Standard Microelectronics Drawing (SMD):

- 5962-17212 (QML Q and Q+)

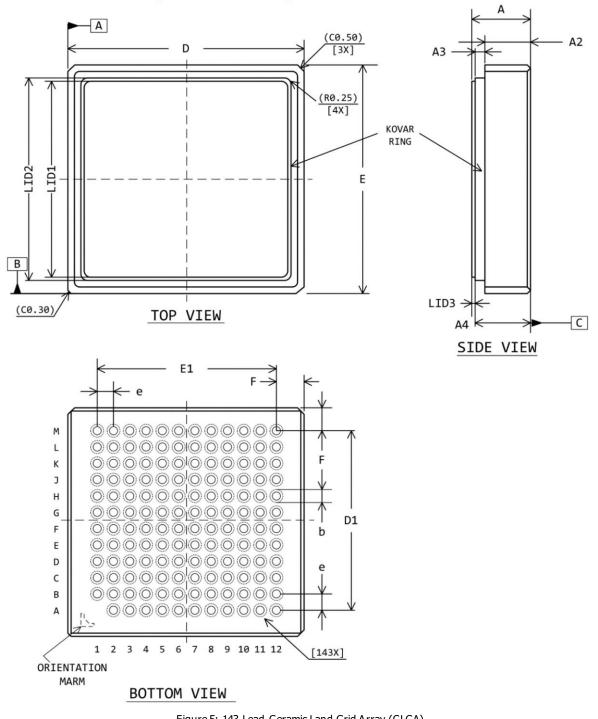

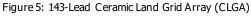

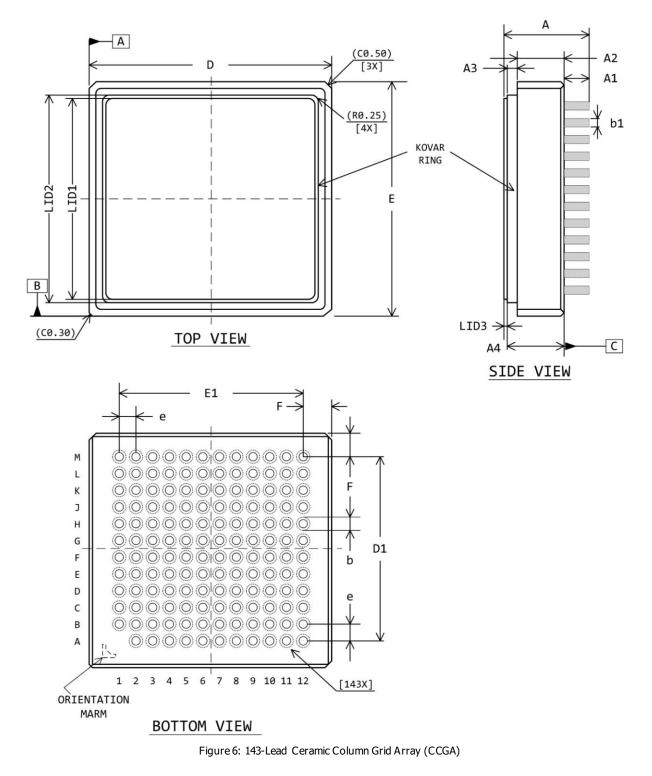

- Package Options:

- 143-Pin

- Ceramic Land Grid Array

- Ceramic Column Grid Array

- Ceramic Ball Grid Array (Prototy pe Only)

- Plastic Ball Grid Array (Preliminary, see Datasheet Definitions)

- 14.5 x 14.5 mm, 1 mm pitch

#### **Operational Environment**

- Temperature Range: -55°C to +105°C

- Total Dose: 50 krad(Si)

- SEL Immune:  $\leq 80 \text{ MeV} \text{cm}^2/\text{mg}$

- SER<sub>HI</sub>:  $8.30 \times 10^{-8}$  errors/device-day

#### Applications

- CAN Bus Controller

- SpaceV PX Chassis Management

- Telemetry/System Health Monitoring

- Distributed Command and Control

- Data Acquisition

- RF Signal Chain Management

#### Introduction

The UT32M0R500 microcontroller utilizes the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit processor with a RISC based architecture operating at a 50 MHz frequency. The microcontroller includes a memory protection unit (MPU), embedded memories, with several peripherals including support for CAN 2.0B. For increased design flexibility, the microcontroller includes several analog features such as an analog signal channel with a multiplexed input combined with a programmable gain amplifier and analog-to-digital converter, two digital-to-analog converters, two analog comparators, and precision current source.

The UT32M0R500 incorporates a variety of power-saving modes to facilitate the design of low-power applications.

The UT32M0R500 is supported by the Keil<sup>®</sup> Development Tool Environment. For information on the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the <u>www.arm.com</u> website.

### UT32M0R500

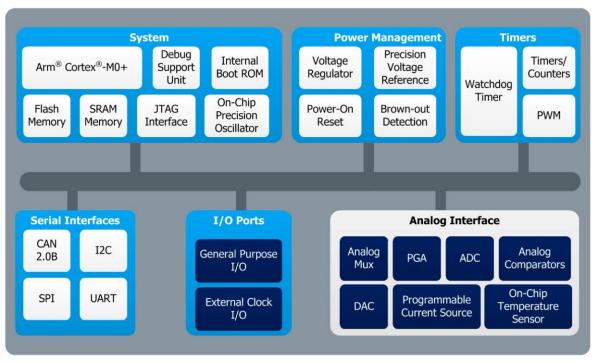

Figure 1: UT32M0R500 Block Diagram

### UT32M0R500

#### 1 Functional Overview/System Summary

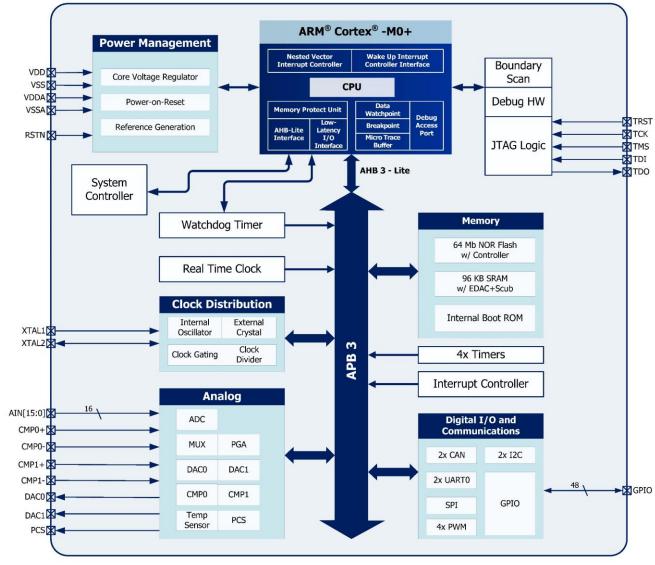

Figure 2: UT32M0R500 Functional Block Diagram

#### 1.1 Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ Processor with MPU

The Cortex-M0+ processor is a low-power 32-bit A RM Cortex processor designed for a wide range of embedded applications. The Cortex-M0+ is based on a highly optimized 32-bit processor core with a pipeline V on Neumann architecture. The processor has exceptional energy efficiency with a small but powerful instruction set coupled with a hardware single-cycle multiplier and Memory Protection Unit (MPU).

With the use of the Arm core, the UT32M0R500 is compatible with the Arm tools and software.

#### 32-Bit A rm $^{\mbox{\tiny B}}$ C ortex $^{\mbox{\tiny B}}$ -M0+ Microcontroller

### UT32M0R500

#### Table 1: UT32M0R500 Cortex-M0+ Configuration

| Features                         | ARM M0+ Configurable Option | UT32M0R500 Configuration |  |  |

|----------------------------------|-----------------------------|--------------------------|--|--|

| Interrupts                       | 0 – 32                      | 32                       |  |  |

| Data Endianness                  | Little-endian or big-endian | Little-endian            |  |  |

| SysTick Timer                    | Present or absent           | Present                  |  |  |

| Number of Watchpoint Comparators | 0, 1, 2                     | 2                        |  |  |

| Number of Breakpoint Comparators | 0 - 4                       | 4                        |  |  |

| Multiplier                       | Fast or small               | Fast (Single Cycle)      |  |  |

| Wakeup Interrupt Controller      | Supported or not support    | Supported                |  |  |

| Vector Table offset Register     | Present or absent           | Present                  |  |  |

| Unprivileged/Privileged Support  | Present or absent           | Present                  |  |  |

| Memory Protection Unit           | Present or absent           | Present                  |  |  |

| Reset All Registers              | Present or absent           | Present                  |  |  |

| Debug Configuration              | Present or absent           | Present                  |  |  |

| Micro Trace Buffer               | Present or absent           | Present                  |  |  |

#### 1.2 Core – M0+ Peripherals

#### 1.2.1 SysTick

The System Timer is a 24-bit timer that extends the functionality of both the processor and the NVIC. Refer to the Cortex-M0+ Technical Reference Manual for details (<u>www.arm.com</u>).

#### 1.2.2 Nested Vector Interrupt Controller (NVIC)

The NVIC and the Cortex-M0+ processor core are closely coupled, providing low latency interrupt processing and efficient processing of late arriving interrupts. The NVIC includes a Non-Maskable Interrupt (NMI), zero jitter interrupt capability, and four interrupt priority levels with 32 programmable interrupts.

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

A ny pin on bank 0, bank 2, or bank 3 regardless of the selected function can be programmed to generate an interrupt on a rising edge, a falling edge, high or low state.

#### 1.2.3 Micro Trace Buffer

The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex-M0+ processor. Refer to section Micro Trace Buffer and the CoreSight MTB-M0+ Technical Reference Manual for details (<u>www.arm.com</u>).

#### **1.3 Low Power Options**

The UT32M0R500 includes built-in flexibility for low power operation. This is supported through power down control for several of the IP blocks in the device.

#### 1.4 System Controller

The UT32M0R500 includes a system controller that provides functionality to support the miscellaneous functions without dedicated controllers. This includes items such as:

- Reset status Last reset source, reset counter

- Power Management Unit (PMU) Enable

- Reset control logic

- Boot Configuration Access

- Clock Divide Control

- Oscillator Shutdown

- A nalog Shutdowns for

- Precision current source

- Temperature Sensor shutdown

- Low Noise Voltage Reference to ADC/DAC/Comparators shutdown

- Current reference to A DC/DAC/Comparators shutdown

- General Purpose Registers with "Stay Alive" option

The UT32M0R500 has a clock distribution unit (CDU) that supports both an internal and external clock source. The internal clock source is based on a highly robust 50 MHz oscillator. The CPU and each peripheral have a clock divider circuit that is controlled by the system controller. The CDU supports a crystal oscillator or square wave input on the XTAL1 and XTA2 pins for the external clock source.

The clock selection is based on the state of the CLKSEL pin (0 =internal, 1 =external) which is read at the end of the boot sequence.

#### **1.5 Power Management**

#### 1.5.1 On-Chip Regulators

The UT32M0R500 includes on-chip regulators for supplying power to the digital core, oscillator, and analog components. CAES recommends separate digital power analog power planes (power and ground) to minimize noise interference. For more information, see the UT32M0R500 Board Design Recommendations appnote on the CAES website:

https://caes.com/product/ut32m0r500#downloads

#### 1.5.2 Power-on-Reset

The UT32M0R500 contains power-on-reset (POR) circuitry. The POR monitors the VDD and VDDA power supplies. The POR also monitors the internally regulated core voltage (VDDC). The POR supports an external reset mode using the RSTN pin.

#### 1.6 Boot Modes

The UT32M0R500 supports four (3) modes of booting the device where the mode selection is based on the configuration of the BOOTCFG0 and BOOTCFG1 pins as specified in Table 2.

#### **Table 2: Boot Mode Selection Description**

| Boot mode selection pins |          | Poet Mede | Description                                                 |

|--------------------------|----------|-----------|-------------------------------------------------------------|

| BOOTCFG1                 | BOOTCFG0 | Boot Mode | Description                                                 |

| 0                        | 0        | 0         | Load image from internal Flash memory into SRAM and execute |

| 0                        | 1        | 1         | Reserved                                                    |

| 1                        | 0        | 2         | Load/Update image over UART0 into flash (reset required)    |

| 1                        | 1        | 3         | Load/Update image over CAN0 into flash (reset required)     |

#### Note:

1) Boot modes will only be switched or interpreted on a RESET event or external reset.

The following sections give further details of the three boot modes supported by the UT32M0R500.

#### 1.6.1 Boot Mode 0 (BOOTCFG = 2'b00)

This mode describes the loading of the firmware image from NOR Flash into internal SRAM memory operation. This mode is considered the normal (default) boot operation mode. In this mode, the bootloader performs a system initialization where the device is placed in the default state and initializes communication with the NOR Flash. The bootloader copies the firmware image from NOR Flash memory to internal SRAM. After copying the user code, a CRC verification of the code is performed to determine if the transfer was successful. Upon a successful code transfer, the bootloader checks the CLKSEL pin to determine if an external clock is to be used. If the CLKSEL pin is in a High state, then the system clock is switched over to using the external clock on the XTAL[1:0] pins. All bootloader operations are performed using the internal oscillator operating at 50 MHz until the CLKSEL pin is checked. After the clock selection is performed, the program counter is set to point to the beginning of the transferred code and code execution starts.

#### 1.6.2 Boot Mode 1 (BOOTCFG = 2'b01)

Reserved.

#### 1.6.3 <u>Boot Mode 2</u> (BOOTCFG = 2'b10)

This mode describes the loading of the firmware image over UART (UART0) mode of operation. In this mode, the bootloader first performs a system initialization where the device is placed in the default state. The bootloader then configures the UART0 for operating at 19200 baudrate/x-bits/x-parity/stop bit. After configuring the UART0, the bootloader loads the firmware image transmitted over UART0 to the addressed memory of the internal Flash memory location based on the image number selected. All bootloader operations are performed using the internal oscillator operating at 50 MHz. To execute the firmware, the BOOTCFG pins must be set to 2'b00 and a reset applied.

#### 1.6.4 Boot Mode 3 (BOOTCFG = 2'b11)

This mode describes the loading of the firmware image over the CAN bus (CAN0) mode of operation. In this mode, the bootloader first performs a system initialization where the device is placed in the default state. The bootloader

then configures the CANO for operating at 125 kHz. A fter configuring the CANO, the bootloader copies the firmware image transmitted over CANO to the addressed location as prescribed by the image number. A fter a successful load of the firmware, the BOOTCFG pins must be set to 2'b00 and a reset applied for the firmware to start executing. All bootloader operations are performed using the internal oscillator operating at 50 MHz.

#### 1.7 GPIO – General Purpose Inputs/Outputs

The pins of the UT32M0R500 support operating as general purpose I/O or as alternative functions. Configuration registers control the functionality of the pin and its connectivity to the on-chip peripherals for the alternate functions. When configuring for use as the alternative function, the peripheral should be connected to the appropriate pins prior to being activated and prior to any related interrupts being enabled. Dedicated GPIO are initialized as input, whereas GPIO with alternate functions are initialized to use the alternate function. The GPIO are configured in three banks of 16 pins each: Bank 0[15:0] = GPIO[15:0], Bank 1[15:0] = GPIO[31:16], Bank 2[15:0] = GPIO[47:32] in MSB:LSB order for each bank. Each bank has a shared interrupt (for the 16 pins within the bank). In addition, each of the inputs to the GPIO (when configured as input) can be used as an IRQ. All pins can be configured to have a pull-up, pulldown, or tri-state (for open-drain operation). The GPIO are half-word (16 bit), byte (8 bit) or half-byte (4 bit) addressable where read or writes occur in a single cycle. The GPIO support upper/lower by te mask registers for access control.

#### Table 3: GPIO Reference

| GPIO number          | Bankx[15:0] | Bank AHB Address        |

|----------------------|-------------|-------------------------|

| GPIO 2 = GPIO[47:32] | Bank 2      | 0x40022000 - 0x40022FFF |

| GPIO 1 = GPIO[31:16] | Bank 1      | 0x40021000 - 0x40021FFF |

| GPIO 0 = GPIO[15:0]  | Bank 0      | 0x40020000 - 0x40020FFF |

The GPIO pins have the following features:

- State programmable

- A fter power-up the dedicated I/O pins are configured as inputs. All other pins are configured to use the alternate function.

- Most digital pins can be a peripheral function or be driven by GPIO logic

- GPIO logic organized into banks of 16 pins

- GPIO can be software controlled to be high, low, tri-state, pull-up or pull-down

- GPIO can be programmed to generate a shared interrupt for any pin for each bank

- Stay alive functionality supported

#### 1.8 Memory

#### 1.8.1 On-chip Flash Memory

The UT32M0R500 contains 64Mb of on-chip flash program memory. The flash memory has 384KB dedicated for user application firmware allocated in increments of 96KB. The flash memory can be programmed through the UART0 or CAN0 interfaces.

Further details about the flash memory can be referenced in the UT32M0R500 User/Functional Manual.

#### 1.8.2 On-chip SRAM

The UT32M0R500 includes a total of 96KB on-chip dual-port static RA M (SRAM) data memory to be used for firmware and data. The dual port architecture, which consists of a single memory array, supports access from two independent ports – each having a set of address, data, and control signals. The device allows simultaneous access to a single SRAM memory location from both ports. The SRAM allocates 96KB of memory for user application firmware accessible by the CPU. The SRAM includes error detection and correction (EDAC) with bit scrubbing. The EDAC implements a Single Error C orrection Double Error D etection (SECDED) protection algorithm. The SRAM module includes provisions for providing single bit error (SBE) and multiple bit error (MBE) counts for user processing with programmable interrupt support for the MBE.

Note: Only 90KB of SRAM is available during boot with the full 96KB available during program execution.

#### 1.8.3 MPU

The UT32M0R500 has a Memory Protection Unit (MPU) which can be used to improve the robustness of an embedded system by protecting critical data within the user application. The MPU divides the memory map into a number of regions with privilege permissions and access rules preventing disallowed accesses.

#### **1.9 Analog Components**

#### 1.9.1 12-bit Analog-to-Digital Converter

The UT32M0R500 contains one ADC. It is a single 12-bit Delta Sigma ADC with 16 input channels and programmable gain amplifier. It has the following features:

- 12-bit Output Data

- Selectable Oversample Rate of Delta Sigma Modulator

- Up to 100 ksps conversion rate

- A PB-protocol control and status access from M0+ system bus

- Input multiplexing among sixteen pins

- Supports auto-sequence of 17 signal inputs, or a single input enable

- Single-ended or differential inputs controlled by enable registers

- Programmable gain amp enable and gain setting, SINC4 filter enable per channel

- Two selectable decimation filters (COI3 or SINC 4)

- Individual result register for each input channel

- Programmable gain amplifier

- Power-down mode

#### 1.9.2 12-bit Digital-to-Analog Converters

The UT32M0R500 contains two voltage output DACs. Each of the DACs operates independently and allow for generating a variable analog output. The maximum output of each DAC is VREFP. Each DAC has the following features:

- Buffered output

- Synchronous or Independent update

- Power-down mode

- Soft-Reset supported by enable bit

#### 32-Bit A rm $^{\mbox{\tiny B}}$ C ortex $^{\mbox{\tiny B}}$ -M0+ Microcontroller

### UT32M0R500

#### 1.9.3 Comparators

The UT32M0R500 contains two high speed comparators with hysteresis.

#### 1.10 Pulse Width Modulators

The UT32M0R500 contains three standard 16-bit PWMs. The modules are multi-purpose timer/counter systems allowing for complex timing or waveform generation. The PWM has an internal prescalar.

- Each PWM has three individual outputs, or two paired (Push/Pull) Outputs

- Programmable Dead-Band Scaler

- Can divide the system clock up to a total dead band range of 20ns to 81,920ns

- Programmable Clock Scaler per PWM Individual Output

- Support a 335 ms pulse

- Single Combined Interrupt for all three PWMs

- Interrupt counter to reduce M0+ ISR activity

#### **1.11 General Purpose Timers**

The UT32M0R500 includes four 32-bit programmable timer/counters. The timer/counter is designed to count cycles of the system derived clock or an externally-supplied clock. It can optionally generate interrupts, or perform other actions at specified timer values. Each of the timers support three modes of operation: free-running, periodic (with interrupt), one-shot (interrupt and halt)

#### 1.11.1 Real-Time Clock

- Programmable 32-bit free-running up-counter

- Clocked only by system clock (Not truly "real time")

- Current Value register can be read through A PB interface

- Counter wrap at value = match register, or at maximum count

- Counter wrap to a "load register" value

#### 1.11.2 WDT – Watchdog Timer

The UT32M0R500 includes a Watchdog Timer (WDT) which is a system for monitoring correct program operation. The WDT supports two modes of operation: Timeout and Window. In Timeout mode, the WDT is configured to a predefined time-out period and is constantly running when enabled. If the WDT is not cleared within the time-out period, it will issue a system reset. In Window mode, the WDT has a defined window within the total time-out period during which the WDT must be cleared. If the WDT is cleared outside this window, either too early or too late, a system reset will be issued.

- A system (soft)reset is issued if the WDT is not cleared before its time-out period

- Two modes of operation

- Timeout

- Window

- 32 bit Selectable time-out periods (both Timeout and Window Modes)

- Circuit meant to detect stuck or runaway code and restore system to functionality

- Countdown timer that generates first an interrupt then a system reset if not cleared

- Window mode will reset system if the timer is cleared before a programmable count

### UT32M0R500

#### **1.12 Communication Interfaces**

#### 1.12.1 CAN - Controller Area Network (CANO, CAN1)

In the UT32M0R500, there are two independent CAN controller peripherals. The CAN is a serial communications protocol which efficiently supports distributed real-time control with a very high level of robustness and reliability. Each of the CAN controllers is based on the Philips SJA 1000 and supports both BasicCAN (CAN 2.0A) and PeliCAN (CAN 2.0B) mode with a few exceptions. Each mode of operation utilizes a 64-byte RX buffer and 8-byte TX buffers. The mode of operation is user selectable through the Clock Divider register. Each CAN controller operate independently with the following features:

- CAN 2.0B supported with max speed of 1 Mbps.

- Based on the Philips SJA 1000 and has a compatible register map with a few exceptions.

- Supports both BasicCAN (PCA82C200 like) and PeliCAN mode.

- In PeliCAN mode the extended features of CAN 2.0B is supported.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- 64-byte RX Buffer, 8-Byte TX Buffer.

- 32 user configurable registers.

- Includes acceptance filters with support mask filters.

Further details about the CAN interface can be referenced in the UT32M0R500 User/Functional Manual.

#### 1.12.2 I2C (I2C0, I2C1)

The UT32M0R500 contains two I2C controllers. The I2C -bus is a simple 2-wire serial multi-master bus with collision detection and arbitration. The bus consists of a serial data line (SDA) and a serial clock line (SCL). Each I2C interface is Standard Mode (Sm, up to 100 kbit/s) compliant and Fast Mode (Fm, up to 400 kbit/s), Fast Mode Plus (Fm+, up to 1 Mbit/s) compatible. Each of the interfaces support 7-bit and 10-bit addressing modes, with a user-selectable bit filtering length.

- Standard (up to 100 kbps), Fast (up to 400 kbps), and Fast+ (1 Mbps) transfer speeds.

- Two wire serial communication: Serial Clock Line(SCL) for clock and Serial Data Line(SDA) for data

- Supports master or slave mode of operations

- Collision detection and clock synchronization procedure for multi master bus operation

- Supports 7-bit or 10-bit addressing

- User-selectable bit filtering length

- Dynamic updating of I2C address without losing the bus

- 14 maskable interrupts combined to one M0+ interrupt

#### 1.12.3 SPI – Serial Peripheral Interface

The UT32M0R500 contains one SPI controller. The SPI controller is capable of operation on a SPI bus. It can interact with multiple slaves on the bus. Only a single master and a single slave can communicate on the bus. The SPI controller has the following features:

- SPI Master operation using Motorola SPI protocol

- Up to 10 MHz transfer rate

- Tx and Rx FIFOs with a 16 word depth

- User-selectable SPI data width of 4-16 bits

- Programmable RX sample point delay, to support long transmission lines

- User-selectable SPI Baud rate, at even-integer division of system clock

- Supports all 4 SPI SC PH and SCPOL modes

- Supports EEPROM read mode

- Supports up to 3 slave selects

#### 1.12.4 UART – Universal Asynchronous Receiver-Transmitter (UARTO, UART1)

The UT32M0R500 contain two UARTs. Standard baud rates such as 115200 Bd can be achieved without the need for external crystal.

- Independent transmit and receive for each of the modules

- 8-bit Data

- Supports parity bit and one stop bit

- Low pass filter on start bit

#### 1.13 Memory Map

#### Table 4. AHB Memory Map Table

| Address Range                     | UT32M0R500 Modules                                 |

|-----------------------------------|----------------------------------------------------|

| 0x0000 0000 - 0x0000 7FFF (32KB)  | Boot ROM                                           |

| 0x0100 0000 - 0x0100 FFFF (64KB)  | NOR Flash                                          |

| 0x2000 0000 - 0x2001 7FFF (96KB)  | SRAM                                               |

| 0x4000 0000 - 0x4001 FFFF (128KB) | APB Peripherals                                    |

| 0x4002 0000 - 0x4002 0FFF (4KB)   | AHB GPIO Bank 0                                    |

| 0x4002 1000 - 0x4002 1FFF (4KB)   | AHB GPIO Bank 1                                    |

| 0x4002 2000 - 0x4002 2FFF (4KB)   | AHB GPIO Bank 2                                    |

| 0x4002 3000 - 0x4002 3FFF         | AHB CAN 0                                          |

| 0x4002 4000 - 0x4002 4FFF         | AHB CAN 1                                          |

| 0x4002 FFFF - 0x4002 F000 (4KB)   | System Controller                                  |

| 0xE000 0000 - 0xE00F FFFF         | Private peripheral bus addresses in the Cortex-M0+ |

| 0xF000 0000 - 0xF000 0FFF (4KB)   | System ROM                                         |

| 0xF020 0000 - 0xF020 0FFF (4KB)   | MTB SFR                                            |

| 0xF021 0000 - 0xF021 FFFF (64KB)  | 4kB MTB SRAM                                       |

| 0xF022 0000 - 0xFFFF FFFF         | Cortex M0+                                         |

### UT32M0R500

#### Table 5. APB Peripheral Memory Map Table

| Address Range             | UT32M0R500 Modules         |

|---------------------------|----------------------------|

| 0x4000 0000 - 0x4000 0FFF | RTC                        |

| 0x4000 1000 - 0x4000 1FFF | Dual Timer0                |

| 0x4000 2000 - 0x4000 2FFF | Dual Timer1                |

| 0x4000 3000 - 0x4000 3FFF | PWM                        |

| 0x4000 4000 - 0x4000 4FFF | UART0                      |

| 0x4000 5000 - 0x4000 5FFF | UART1                      |

| 0x4000 6000 - 0x4000 6FFF | SPI                        |

| 0x4000 7000 - 0x4000 7FFF | DACs                       |

| 0x4000 8000 - 0x4000 8FFF | Watchdog                   |

| 0x4000 9000 - 0x4000 9FFF | 12C0                       |

| 0x4000 A000 - 0x4000 AFFF | I2C1                       |

| 0x4000 B000 - 0x4000 BFFF | Trim Control               |

| 0x4000 C000 - 0x4000 CFFF | NFC (NOR Flash Controller) |

| 0x4000 D000 - 0x4000 DFFF | SRAM EDAC/Scrub            |

| 0x4000 E000 - 0x4000 EFFF | Comparators                |

| 0x4000 F000 - 0x4000 FFFF | ADC                        |

#### 2 Pinlist

| Abbreviation | Description                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------|

| IPU          | LVTTL Compatible                                                                                              |

| I/O          | LVCMOS Compatible Tri-State Bi-Direct with Internal Pull-up/Pull-down                                         |

| I            | LVCMOS Compatible Input                                                                                       |

| 0            | LVCMOS Compatible Output                                                                                      |

| AI           | Analog Input                                                                                                  |

| AO           | Analog Output                                                                                                 |

| SN           | Selectable Pull-up/Pull-down, neither selected on power-up                                                    |

| NC           | No connect. Required for pin to remain floating.                                                              |

| Х            | Unknown                                                                                                       |

| Z            | Tri-State, Floating or High Impedance                                                                         |

| NUIL         | Not used input low. Need to be connected by user to Vss through a $\geq 10 \text{ k}\Omega \pm 10\%$ resistor |

#### Table 6: Pinlist

| Pin No.                                           | Name                | Туре   | Default<br>State | Value<br>During POR | Reset Value<br>After POR | PU/<br>PD | Description                        |

|---------------------------------------------------|---------------------|--------|------------------|---------------------|--------------------------|-----------|------------------------------------|

| D5, E5, E7, F5, F7, G5,<br>G7, H5, H7, J5, J7     | V <sub>DD</sub> (3) | Power  | -                | -                   | -                        | -         | Digital Supply voltage             |

| C5, D4, E4, E6, F4, F6,<br>G4, G6, H4, H6, J4, J6 | Vss <sup>(3)</sup>  | Ground | -                | -                   | -                        | -         | Digital Ground                     |

| C6, C8, D6, D8, E8,<br>F8, G8, H8, J8, K8, L8     | VDDA <sup>(3)</sup> | Power  | -                | -                   | -                        | -         | Analog Supply Voltage              |

| C7, 9, D7, D9, E9, F9,<br>G9, H9, J9, K9, L9      | Vssa <sup>(3)</sup> | Ground | -                | -                   | -                        | -         | Analog Ground                      |

| E12                                               | AIN0                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 0             |

| F12                                               | AIN1                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 1             |

| G12                                               | AIN2                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 2             |

| H12                                               | AIN3                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 3             |

| F11                                               | AIN4                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 4             |

| G11                                               | AIN5                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 5             |

| H11                                               | AIN6                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 6             |

| J11                                               | AIN7                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 7             |

| J12                                               | AIN8                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 8             |

| K12                                               | AIN9                | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 9             |

| L12                                               | AIN10               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 10            |

| M12                                               | AIN11               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 11            |

| K11                                               | AIN12               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 12            |

| L11                                               | AIN13               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 13            |

| M11                                               | AIN14               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 14            |

| M10                                               | AIN15               | AI     | Input            | Х                   | Z                        | -         | Analog Input Channel 15            |

| J10                                               | Reserved            | -      | -                | -                   | -                        | -         | NC                                 |

| E11                                               | Reserved            | -      | -                | -                   | -                        | -         | NC                                 |

| D10                                               | LDO<br>15_BYP       | Ι      | Input            | -                   | -                        | -         | Connect to VSSA                    |

| C10                                               | LDO<br>28_BYP       | Ι      | Input            | -                   | -                        | -         | Connect to VSSA                    |

| F10                                               | Reserved            | -      | -                | -                   | -                        | -         | NC                                 |

| E10                                               | Reserved            | -      | -                | -                   | -                        | -         | NC                                 |

| G10                                               | Reserved            | -      | -                | -                   | -                        | -         | NC                                 |

| M9                                                | PCS                 | 0      | Output           | -                   | -                        | -         | Precision Current Source<br>Output |

| D12                                               | DAC0                | AO     | Output           | Х                   | 0                        | -         | DAC Output Channel 0               |

| C12                                               | DAC1                | AO     | Output           | Х                   | 0                        | -         | DAC Output Channel 1               |

#### 32-Bit A rm $^{\mathbb{R}}$ C ortex $^{\mathbb{R}}$ -M0+ Microcontroller

| Pin<br>No. | Name                | Туре       | Default<br>State      | Value<br>During POR | Reset Value<br>After POR | PU/<br>PD | Description                                                               |

|------------|---------------------|------------|-----------------------|---------------------|--------------------------|-----------|---------------------------------------------------------------------------|

| B12        | CMP0+               | AI         | Input                 | х                   | Z                        | -         | Voltage Comparator 0<br>Positive Input                                    |

| A12        | CMP0-               | AI         | Input                 | Х                   | Z                        | -         | Voltage Comparator 0<br>Negative Input                                    |

| D11        | CMP1+               | AI         | Input                 | Х                   | Z                        | -         | Voltage Comparator 1 Positive<br>Input                                    |

| C11        | CMP1-               | AI         | Input                 | х                   | Z                        | -         | Voltage Comparator 1 Negative<br>Input                                    |

| M4         | C AN0_RXD           | Ι          | Input                 | Х                   | 0                        | SN        | CAN 0 Receive Data                                                        |

| M5         | C AN0_TXD           | 0          | Output                | Х                   | 1                        | SN        | CAN 0 Transmit Data                                                       |

| M6         | UART0_TXD           | 0          | Output                | Х                   | 1                        | SN        | UART 0 Channel Transmit Data                                              |

| M7         | UART0_RXD           | Ι          | Input                 | х                   | Z                        | SN        | UART 0 Channel Receive Data                                               |

| A2         | CAN1_RXD<br>GPIO32  | I<br>I/O   | CAN1_RXD<br>(Input)   | х                   | Z                        | SN<br>SN  | CAN 1 Receive Data<br>General purpose digital<br>input/output             |

| B1         | CAN1_TXD<br>GPIO33  | O<br>I/O   | CAN1_TXD<br>(Output)  | х                   | 1                        | SN<br>SN  | CAN 1 Transmit Data<br>General purpose digital<br>input/output            |

| C1         | UART1_TXD<br>GPIO34 | O<br>I/O   | UART1_TXD<br>(Output) | х                   | 1                        | SN<br>SN  | UART 1 Channel Transmit Data<br>General purpose digital<br>input/output   |

| D1         | UART1_RXD<br>GPIO35 | I<br>I/O   | UART1_RXD<br>(Input)  | x                   | Z                        | SN<br>SN  | UART 1 Channel Receive Data<br>General purpose digital<br>input/output    |

| E1         | SCL0<br>GPIO36      | I/O<br>I/O | SCL0<br>(Input)       | x                   | Z                        | SN<br>SN  | I2C 0 Serial Clock<br>General purpose digital<br>input/output             |

| F1         | SDA0<br>GPIO37      | I/O<br>I/O | SDA0<br>(Input)       | x                   | Z                        | SN<br>SN  | I2C 0 Serial Data<br>General purpose digital<br>input/output              |

| J1         | SCL1<br>GPIO38      | I/O<br>I/O | SCL1<br>(Input)       | х                   | Z                        | SN<br>SN  | I2C 1 Serial Clock<br>General purpose digital<br>input/output             |

| К1         | SDA1<br>GPIO39      | I/O<br>I/O | SDA1<br>(Input)       | х                   | Z                        | SN<br>SN  | I2C 1 Serial Data<br>General purpose digital<br>input/output              |

| L1         | SCLK<br>GPIO40      | I/O<br>I/O | SCLK<br>(Output)      | х                   | 0                        | SN<br>SN  | SPI Master Clock<br>General purpose digital<br>input/output               |

| M1         | Mosi<br>Gpio41      | I/O<br>I/O | MOSI<br>(Input)       | Х                   | Z                        | SN<br>SN  | SPI Master Output, Slave Input<br>General purpose digital<br>input/output |

#### 32-Bit A $rm^{\circledast}$ C $ortex^{\circledast}$ -M0+ Microcontroller

| Pin<br>No. | Name           | Туре       | Default<br>State | Value<br>During POR | Reset Value<br>After POR | PU/<br>PD | Description                                                                  |

|------------|----------------|------------|------------------|---------------------|--------------------------|-----------|------------------------------------------------------------------------------|

| M2         | MISO<br>GPIO42 | I/O<br>I/O | MISO<br>(Input)  | х                   | Z                        | SN<br>SN  | SPI Master Input, Slave Output<br>General purpose digital<br>input/output    |

| М3         | SSN0<br>GPIO43 | O<br>I/O   | SSN0<br>(Output) | х                   | 1                        | SN<br>SN  | SPI Slave 0 Select<br>General purpose digital<br>input/output                |

| B2         | PWM0<br>GPIO44 | 0<br>I/O   | PWM0<br>(Output) | х                   | 0                        | SN<br>SN  | Pulse Width Modulated<br>Signal 0<br>General purpose digital<br>input/output |

| B3         | PWM1<br>GPIO45 | O<br>I/O   | PWM1<br>(Output) | х                   | 0                        | SN<br>SN  | Pulse Width Modulated Signal 1<br>General purpose digital<br>input/output    |

| C2         | PWM2<br>GPIO46 | O<br>I/O   | PWM2<br>(Output) | х                   | 0                        | SN<br>SN  | Pulse Width Modulated Signal 2<br>General purpose digital<br>input/output    |

| С3         | PWM3<br>GPIO47 | O<br>I/O   | PWM3<br>(Output) | х                   | 0                        | SN<br>SN  | Pulse Width Modulated Signal 3<br>General purpose digital<br>input/output    |

| D2         | GPIO0          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| D3         | GPIO1          | I/O        | Input            | Х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| E2         | GPIO2          | I/O        | Input            | Х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| E3         | GPIO3          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| F2         | GPIO4          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| F3         | GPIO5          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| G2         | GPIO6          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| G3         | GPIO7          | I/O        | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| H2         | GPIO8          | I/O        | Input            | Х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| H3         | GPIO9          | I/O        | Input            | Х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| J2         | GPIO10         | I/O        | Input            | Х                   | Z                        | SN        | General purpose digital<br>input/output                                      |

| Pin<br>No. | Name    | Туре | Default<br>State | Value<br>During POR | Reset Value<br>After POR | PU/<br>PD | Description                             |

|------------|---------|------|------------------|---------------------|--------------------------|-----------|-----------------------------------------|

| J3         | GPIO11  | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output |

| К2         | GPIO12  | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output |

| К3         | GPIO13  | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output |

| L2         | GPIO14  | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output |

| L3         | GPIO15  | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output |

| B10        | GPIO16  | I/O  | GPIO16           | x                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR17  | Ι    | (Input)          |                     |                          | SN        | External interrupt 17                   |

| B9         | GPIO17  | I/O  | GPIO17           | x                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR18  | Ι    | (Input)          |                     |                          | SN        | External interrupt 18                   |

| B8         | GPIO18  | I/O  | GPIO18           | x                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR19  | Ι    | (Input)          |                     |                          | SN        | External interrupt 19                   |

| B7         | GPIO19  | I/O  | GPIO19           | х                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR20  | Ι    | (Input)          |                     |                          | SN        | External interrupt 20                   |

| B6         | GPIO20  | I/O  | GPIO20           | х                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR21  | Ι    | (Input)          |                     |                          | SN        | External interrupt 21                   |

| B5         | GPIO21  | I/O  | GPIO21           | х                   | Z                        | SN        | General purpose digital<br>input/output |

|            | INTR22  | I    | (Input)          |                     |                          | SN        | External interrupt 22                   |

| 54         | GPIO22  | I/O  | GPIO22           | Ň                   | _                        | SN        | General purpose digital                 |

| B4         | INTR23  | Ι    | (Input)          | Х                   | Z                        | SN        | input/output<br>External interrupt 23   |

|            | GPIO23  | I/O  | GPIO23           |                     |                          | SN        | General purpose digital                 |

| A3         |         | -    |                  | х                   | Z                        |           | input/output                            |

|            | INTR24  | Ι    | (Input)          |                     |                          | SN        | External interrupt 24                   |

| A11        | GPIO24  | I/O  | GPIO24           | v                   | Z                        | SN        | General purpose digital<br>input/output |

| AII        | CMP0OUT | 0    | (Input)          | Х                   | Z                        | SN        | Comparator 0 Output                     |

|            | GPIO25  | I/O  | GPIO25           |                     |                          | SN        | General purpose digital                 |

| A10        | CMP1OUT | 0    | (Input)          | Х                   | Z                        | SN        | input/output<br>Comparator 1 Output     |

|            | GPIO26  | I/O  | GPIO26           | , v                 | -                        | SN        | General purpose digital                 |

| A9         | RTCK    | 0    | (Input)          | Х                   | Z                        | SN        | input/output<br>Real-time clock output  |

#### 32-Bit A rm $^{\mbox{\tiny B}}$ C ortex $^{\mbox{\tiny B}}$ -M0+ Microcontroller

### UT32M0R500

| Pin<br>No. | Name                   | Туре | Default<br>State | Value<br>During POR | Reset Value<br>After POR | PU/<br>PD | Description                                                               |

|------------|------------------------|------|------------------|---------------------|--------------------------|-----------|---------------------------------------------------------------------------|

| A8         | GPIO27                 | I/O  | GPIO27           | х                   | Z                        | SN        | General purpose digital<br>input/output                                   |

|            | SSN1                   | 0    | (Input)          |                     |                          | SN        | SPI Slave 1 Select                                                        |

|            | GPIO28                 | I/O  | GPIO28           |                     |                          | SN        | General purpose digital                                                   |

| A7         | SSN2                   | 0    | (Input)          | Х                   | Z                        | SN        | input/output<br>SPI Slave 2 Select                                        |

|            | GPIO29                 | I/O  | GPIO29           |                     |                          | SN        | General purpose digital                                                   |

| A6         | SSNM                   | Ι    | (Input)          | Х                   | Z                        | SN        | input/output<br>SPI Slave input for multi-<br>master select               |

| A5         | GPIO30                 | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                   |

| A4         | GPIO31                 | I/O  | Input            | х                   | Z                        | SN        | General purpose digital<br>input/output                                   |

| H1         | XTAL1                  | Ι    | Input            | -                   | -                        | -         | External Clock Signal Input<br>(Crystal or Oscillator)                    |

| G1         | XTAL2                  | 0    | Output           | -                   | -                        | -         | External Clock Signal Crystal<br>Feedback                                 |

| К6         | Reserved               | -    | -                | -                   | -                        | -         | NUIL                                                                      |

| B11        | Reserved               | -    | -                | -                   | -                        | -         | NUIL                                                                      |

| K4         | TRST <sup>(1)(2)</sup> | Ι    | Input            | -                   | -                        | SN        | JTAG Reset; Active LOW                                                    |

| L7         | TMS <sup>(1)(2)</sup>  | Ι    | Input            | -                   | -                        | -         | JTAG Test Mode Select                                                     |

| L6         | TCK <sup>(1)(2)</sup>  | Ι    | Input            | -                   | -                        | SN        | JTAG Clock Signal                                                         |

| K5         | TDI <sup>(1)(2)</sup>  | Ι    | Input            | -                   | -                        | SN        | JTAG Data Input                                                           |

| L4         | TDO <sup>(1)(2)</sup>  | 0    | Output           | Х                   | 0                        | -         | JTAG Data Output                                                          |

| L10        | CLKSEL                 | Ι    | Input            | -                   | -                        | SN        | System Clock Select<br>(Internal = Active LOW,<br>External = Active HIGH) |

| K10        | RSTN                   | Ι    | Input            | -                   | -                        | SN        | Pin for system reset; Active<br>LOW                                       |

| M8         | BOOTCFG [0]            | Ι    | Input            | -                   | -                        | SN        | Select Boot Mode Bit 0                                                    |

| K7         | BOOTCFG [1]            | Ι    | Input            | -                   | -                        | SN        | Select Boot Mode Bit 1                                                    |

| L5         | Reserved               | -    | -                | -                   | -                        | -         | NUIL                                                                      |

| H10        | Reserved               | -    | -                | -                   | -                        | -         | NC                                                                        |

| C4         | Reserved               | -    | -                | -                   | -                        | -         | NC                                                                        |

- When JTAG is being used for debugging, 10K pullup resistors should be placed upon the TRST, TMS, TCK, and TDI signals, with TDO floating. When JTAG is NOT being used (Ex. During Flight) TRST MUST have a 10K pulldown resistor, TMS, TCK, and TDI should stay pulled up, and TDO should stay floating.

- 2) The Keil ULINK2 JTAG pod has a variety of pin headers. Please ensure the correct signals are in use. (Ex. TRST is not the same signal as RESET)

- 3) See Section 1.5.1 for the recommended power and ground configuration.

### UT32M0R500

#### 2.1 Pinout Package Arrangement (Top View)

|    | 12    | 11                 | 10                 | 9                 | 8                 | 7                 | 6                 | 5                 | 4                 | 3                 | 2                   | 1                       |     |

|----|-------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------------|-----|

| Μ  | AIN11 | AIN14              | AIN15              | PCS               | BOOTCFG<br>[0]    | UAR TØ_RX D       | UAR T0_TX D       | CAN0_TXD          | CANØ_RXD          | SSN<br>/GPIO43    | MISO<br>/GPIO42     | MOSI<br>/GPI041         | Μ   |

| L. | AIN10 | AIN13              | CLKSEL             | VSSA              | VDDA              | TMS               | тск               | Reserved          | TDO               | GPI015            | GPI014              | SCLK<br>/GPI040         | L.  |

| к  | AIN9  | AIN12              | RSTN               | VSSA              | VDDA              | BOOTCFG<br>[1]    | Reserved          | TDI               | TRST              | GPI013            | GPI012              | SDA1<br>/GPI039         | к   |

| J  | AIN8  | AIN7               | Reserved           | VSSA              | VDDA              | VDD               | VSS               | VDD               | VSS               | GPI011            | GPI010              | SCL1<br>/GPI038         | . J |

| (H | AIN3  | AIN6               | Reserved           | VSSA              | VDDA              | VDD               | VSS               | VDD               | VSS               | GPI09             | GPI08               | XTAL1                   | н   |

| G  | AIN2  | AIN5               | Reserved           | VSSA              | VDDA              | VDD               | VSS               | VDD               | VSS               | GPI07             | GPI06               | XTAL2                   | G   |

| F  | AIN1  | AIN4               | Reserved           | VSSA              | VDDA              | VDD               | VSS               | VDD               | VSS               | GPI05             | GPI04               | SDAØ<br>/GPIO37         | F   |

| E  | AINØ  | Reserved           | Reserved           | VSSA              | VDDA              | VDD               | VSS               | VDD               | VSS               | GPI03             | GPI02               | SCL0<br>/GPI036         | E   |

| D  | DAC0  | CMP1+              | LD015_BYP          | VSSA              | VDDA              | VSSA              | VDDA              | VDD               | VSS               | GPI01             | GPI00               | UAR T1_RXD<br>/GP IO3 5 | D   |

| с  | DAC1  | CMP1-              | LD028_BYP          | VSSA              | VDDA              | VSSA              | VDDA              | VSS               | Reserved          | PWM3<br>/GPIO47   | PWM2<br>/GPI046     | UAR T1_TXD<br>/GP IO34  | с   |

| В  | CMP0+ | Reserved           | GPIO16<br>/INTR17  | GPI017<br>/INTR18 | GPIO18<br>/INTR19 | GPIO19<br>/INTR20 | GPIO20<br>/INTR21 | GPIO21<br>/INTR22 | GPIO22<br>/INTR23 | PWM1<br>/GPI045   | PWMØ<br>/GPIO44     | CAN1_TXD<br>/GPI033     | в   |

| A  | CMP0- | GPI024<br>/CMP0OUT | GPIO25<br>/CMP1OUT | GPI026<br>/RTCK   | GPIO27<br>/SSN1   | GPIO28<br>/SSN2   | GPI029            | GPIO30            | GPI031            | GPIO23<br>/INTR24 | CAN1_RXD<br>/GPI032 |                         | A   |

|    | 12    | 11                 | 10                 | 9                 | 8                 | 7                 | 6                 | .5                | 4                 | 3                 | 2                   | 1                       |     |

#### 3 Absolute Maximum Ratings (1,2)

#### **Table 7: Absolute Maximum Ratings**

| Symbol         | Parameter                            | MIN        | ΜΑΧ        | Units |

|----------------|--------------------------------------|------------|------------|-------|

| Vdd            | Positive Digital Supply Voltage      | -0.3       | +4.2       | V     |

| VDDA           | Positive Analog Supply Voltage       | -0.3       | +4.2       | V     |

| PD             | Max Power Dissipation <sup>(3)</sup> |            | 4.5        | W     |

| τı             | Junction Temperature                 | -55        | +150       | °C    |

| θις            | Thermal resistance, junction-to-case |            | 10         | °C/W  |

| Tstg           | Storage Temperature                  | -65        | +150       | °C    |

| <b>ESD</b> HBM | ESD Protection <sup>(4)</sup>        |            | 2000       | V     |

| Vid            | Digital Pin Input Voltage            | Vss - 0.3  | VDD + 0.3  | V     |

| VIA            | Analog Pin Input Voltage             | Vssa - 0.3 | VDDA + 0.3 | V     |

#### Notes:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification are not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2) All  $V_{DD}$  voltages referenced to  $V_{SS}$  and all  $V_{DDA}$  voltages referenced to  $V_{SSA}$ .

- 3) Per MIL-STD-883, method 1012.1, section 3.4.1,  $P_D = [T_J(max)-T_C(max))/\theta_{JC}]$ . Using  $T_C = 105^{\circ}C$ .

- 4) Per MIL-STD-883, method 3015.9, Table 3.

#### **4 Operational Environment**

#### **Table 8: Operational Environment**

| Symbol | Parameter                                      | Limit                      | Units                   |

|--------|------------------------------------------------|----------------------------|-------------------------|

| TID    | Total Ionizing Dose (1, 2, 3)                  | 50                         | krad(Si)                |

| SEL    | Single Event Latchup Immunity <sup>(4)</sup>   | ≤ 80                       | MeV-cm <sup>2</sup> /mg |

| SERHI  | Heavy Ion Soft Error Rate <sup>(5, 6, 7)</sup> | $\leq 8.30 \times 10^{-8}$ | errors/device-day       |

- For devices procured with a total ionizing dose tolerance guarantee, post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to maximum TID level procured.

- 2) Per MIL-STD-883, method 1019.9, condition A.

- 3) For internal NOR Flash Memory Only. Irradiated per MIL-STD-883 Method 1019.9 Condition C at 50-300 rad(Si)/s using an in-situ 900 rad(Si) device unpowered and 100 rad(Si) device statistically biased duty cycle repeated 50 times to achieve a TID level of 50 krad(Si). This irradiation in-situ biasing method is predicated on an application which may allow the device to be unpowered during 90% of the mission life.

- 4) SEL characterization is performed at  $V_{DD} = V_{DDA} = 3.6 \text{ V}$  and Tc  $\geq 105^{\circ}$ C. Contact factory for additional information.

- 5) SEU characterization is performed at  $V_{DD} = V_{DDA} = 3.0$  V at 25°C. Contact factory for additional information.

- 6) The error rate calculation was performed using Adams 90% worst case environment, Geosynchronous Orbit, 100 mils Aluminum and applies to the internal SRAM.

- Heavy Ion Soft-Reset Error Rate (SER) is defined as an erroneous output signal from the microcontroller device that can be corrected by performing one or more normal functions of the device. Soft errors can be generated from SEU, SEFI, MBU, MCU, and/or SET.

#### 5 Recommended Operating Conditions (1)

#### **Table 9: Recommended Operating Conditions**

| Symbol | Parameter                        | MIN  | MAX  | Units |

|--------|----------------------------------|------|------|-------|

| Тор    | Temperature Range                | -55  | +105 | °C    |

| Тс     | Case Operating Temperature Range | -55  | +105 | °C    |

| Vdd    | Positive Digital Supply Voltage  | +3.0 | +3.6 | V     |

| VDDA   | Positive Analog Supply Voltage   | +3.0 | +3.6 | V     |

| Vss    | Digital Ground                   | +0.0 |      | V     |

| VSSA   | Analog Ground                    | +0   | ).0  | V     |

#### Note:

1) VDD referenced to VSS and VDDA referenced to VSSA.

#### **6** General Electrical Characteristics

Unless otherwise noted,  $T_{\rm C}$  is per the temperature range ordered.

For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

#### **6.1 Test Conditions**

#### 6.1.1 Typical Values

The typical values are based on  $T_c = 25^{\circ}$ C.  $V_{DD} = 3.3$  V, and  $V_{DDA} = 3.3$  V which are guaranteed by simulation and/or technology characterization unless otherwise specified. Typical values are for reference only and are not tested in production.

#### 6.1.2 Minimum and Maximum Values

The minimum and maximum limits represent the test conditions based on supply voltages of  $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{DDA} = 3.3 \text{ V} \pm 0.3 \text{ V}$ , and temperature range of -55°C < T<sub>c</sub> < +105°C by electrical test during production unless otherwise specified.

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests.

#### 32-Bit A rm $^{\ensuremath{\mathbb{R}}}$ C ortex $^{\ensuremath{\mathbb{R}}}$ -M0+ Microcontroller

### UT32M0R500

#### Table 10. General Electrical Characteristics

| Symbol          | Parameter                  | Conditions                                        | MIN | ТҮР | MAX | Units |

|-----------------|----------------------------|---------------------------------------------------|-----|-----|-----|-------|

| <b>f</b> sysclk | System clock frequency     |                                                   |     | 50  |     | MHz   |

| QIDD            | VDD supply current         | All analog peripherals disabled, system clock off |     |     | 6   | mA    |

| Qidda           | VDDA supply current        | All analog peripherals disabled                   |     |     | 5   | mA    |

| AIDD            | VDD active supply current  | fsysclk = 50 MHz                                  |     |     | 80  | mA    |

| AIDDA           | VDDA active supply current | All analog peripherals enabled                    |     |     | 20  | mA    |

#### 6.2 General Purpose I/O Characteristics

#### 6.2.1 DC Characteristics (1)

#### Table 11: I/O DC Characteristics

| Symbol  | Parameter                                                         | Conditions                           | MIN       | MAX | Units |

|---------|-------------------------------------------------------------------|--------------------------------------|-----------|-----|-------|

| Vih     | High Level Input Voltage                                          | $VOUT \ge VOH(min)$                  | 2         |     | V     |

| Vil     | Low Level Input Voltage                                           | $VOUT \leq VOL(max)$                 |           | 0.8 | V     |

| Іін     | High Level Input Leakage<br>Current                               | VIN = VDD                            |           | 1   | μA    |

| IIL     | Low Level Input Leakage Current                                   | $V_{IN} = 0V$                        | -1        |     | μA    |

| Сю      | Input Capacitance <sup>(2)</sup>                                  |                                      |           | 15  | pF    |

| Mari    | Lish Lovel Output Mathema                                         | $V_{DD} = min, I_{OL} = -100 \mu A$  | VDD - 0.2 |     | V     |

| Vон     | High Level Output Voltage                                         | $V_{DD} = min, I_{OH} = -8 mA$       | 2.4       |     | V     |

| Vol     | Low Lovel Output Voltage                                          | $V_{DD} = min, I_{OL} = 100 \ \mu A$ |           | 0.2 | v     |

| VOL     | Low Level Output Voltage                                          | $V_{DD} = min, I_{OL} = 8 mA$        |           | 0.4 | v     |

| Ios     | Output short circuit current (3)                                  | Vout = 0V or Vout = VDD              | -70       | +70 | mA    |

| IINPU   | Input leakage; pull-up state                                      | $V_{IN} = 0V$                        | 10        | 65  | μA    |

| IINPD   | Input leakage; pull-down state                                    | VIN = VDD                            | -65       | -10 | μA    |

| Ііна    | Analog High Level Input Leakage<br>Current <sup>(4)</sup>         | VIN = 2.9V                           |           | 60  | μA    |

| IIH_DAC | High Level Input Leakage<br>Current for DACx <sup>(5)</sup>       | VIN = VDD                            |           | 35  | μA    |

| IIL_DAC | Analog Low Level Input Leakage<br>Current for DACx <sup>(5)</sup> | Vin = 0V                             | -10       |     | μA    |

- 1) All voltages referenced to V<sub>SS</sub>.

- 2) Measured only for initial qualification and after process or design changes that could affect input/output capacitance.

- 3) Guaranteed by design, not production tested.

- 4) Refers to AIN14 and AIN15 pins only.

- 5) Refer to DACx pins only.

### UT32M0R500

#### 6.2.2 AC Characteristics (1)

#### Table 12: I/O AC Characteristics

| Symbol | Parameter | Conditions | MIN | MAX | Units |

|--------|-----------|------------|-----|-----|-------|

| tr     | Rise time |            |     | 5   | ns    |

| tr     | Fall time |            |     | 5   | ns    |

#### Note:

1) Guaranteed by design, not production tested.

#### 6.3 I<sup>2</sup>C PIN Characteristics (1,2,3)

#### Table 13: I<sup>2</sup>C I/O Characteristics

|         |                                                                       |                                           | Standa  | d-Mode  | Fast-Mo        | ode <sup>(15)</sup> | Fast-Mode | Plus <sup>(15)</sup> | Units |

|---------|-----------------------------------------------------------------------|-------------------------------------------|---------|---------|----------------|---------------------|-----------|----------------------|-------|

| Symbol  | Parameter                                                             | Conditions                                | MIN     | MAX     | MIN            | MAX                 | MIN       | MAX                  |       |

| VIH     | High Level Input<br>Voltage                                           |                                           | 0.7*VDD |         | 0.7*Vdd        |                     | 0.7*VDD   |                      | V     |

| VIL     | Low Level Input<br>Voltage                                            |                                           | -0.5    | 0.3*VDD | -0.5           | 0.3*VDD             | -0.5      | 0.3*VDD              | v     |

| Іін     | Input Leakage<br>Current                                              | 0.1*VDD < VIN < 0.9*VDD(max)              | -10     | +10     | -10            | +10                 | -10       | +10                  | μA    |

| Сіо     | Input Capacitance <sup>(5)</sup>                                      |                                           |         | 10      |                | 10                  |           | 10                   | pF    |

| Vol     | Low Level Output<br>Voltage <sup>(4)</sup>                            | VDD > 2 V, IoL =<br>3 mA (open-<br>drain) | 0       | 0.4     | 0              | 0.4                 | 0         | 0.4                  | V     |

| Iol     | Low Level Output                                                      | Vol = 0.4 V                               | 3       |         | 3              |                     | 20        |                      | mA    |

| IOL     | Current <sup>(4)</sup>                                                | Vol = 0.6 V                               |         |         | 6              |                     |           |                      | mA    |

| tof     | Output fall time from<br>VIH(min) to VIL(max) <sup>(4)</sup>          |                                           |         | 250     |                |                     |           |                      | ns    |

| fscl    | SCL clock frequency                                                   |                                           | 0       | 100     | 0              | 400                 | 0         | 1000                 | kHz   |

| tr      | Rise time <sup>(4)</sup>                                              | For both SDC<br>and SCL signals           |         | 1000    | 20             | 300                 |           | 120                  | ns    |

| tf      | Fall time <sup>(4, 7, 8, 9, 10)</sup>                                 | For both SDC<br>and SCL signals           |         | 300     | 20+0.1<br>x Cb | 300                 |           | 120                  | ns    |

| tlow    | Low period of the SCL clock <sup>(4)</sup>                            |                                           | 4.7     |         | 1.3            |                     | 0.5       |                      | μS    |

| thigh   | High period of SCL<br>clock <sup>(4)</sup>                            |                                           | 4.0     |         | 0.6            |                     | 0.26      |                      | μS    |

| tsu;sta | Setup time for a<br>repeated START<br>condition <sup>(4)</sup>        |                                           | 4.7     |         | 0.6            |                     | 0.26      |                      | μS    |

| thd;dat | Data hold time (4,11)                                                 |                                           | 0       |         | 0              |                     | 0         |                      | μS    |

| tsu;dat | Data setup time <sup>(4)</sup>                                        |                                           | 250     |         | 100            |                     | 50        |                      | μS    |

| tsu:sto | Setup time for STOP condition <sup>(4)</sup>                          |                                           | 4.0     |         | 0.6            |                     | 0.26      |                      | μS    |

| tbuf    | Bus free time<br>between a STOP and<br>START condition <sup>(4)</sup> |                                           | 4.7     |         | 1.3            |                     | 0.5       |                      | μS    |

| tvd;dat | Data valid time <sup>(4,12,13)</sup>                                  |                                           |         | 3.45    |                | 0.9                 |           | 0.45                 | μS    |

| tvd;ack | Data valid time <sup>(4,13,14)</sup>                                  |                                           |         | 3.45    |                | 0.9                 |           | 0.45                 | μS    |

### JT32M0R500

- 1) All voltages referenced to V<sub>SS</sub>.

- 2) See the I2C-Bus specification UM10204 for details.

- 3) All related AC (timing) related parameters tested with a load capacitance of 50 pf.

- 4) Guaranteed by design, not production tested.

- 5) Measured only for initial qualification and after process or design changes that could affect input/output capacitance.

- 6) Guaranteed by characterization.

- 7) A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the  $V_{IH(min)}$  of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 8) Cb = total capacitance of one bus line in pF. Max of 400 pF in Standard- and Fast-Modes, and 550 pF in Fast-Plus Mode.

- 9) The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- 10) In Fast-Mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- 11)  $t_{HD;DAT}$  is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge.

- 12) t<sub>VD;DAT</sub> = time for data signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

- 13) The  $t_{HD;DAT}$  could be 3.45 us and 0.9 us for Standard-mode and Fast-mode, but must be less than the maximum of  $t_{VD;DAT}$  or  $t_{VD;ACK}$  by a transition time. This maximum must only be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the setup time before it releases the clock.

- 14) t<sub>VD;ACK</sub> = time for Acknowledgement signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

- 15) Compatible with Fast Mode and Fast Mode Plus specifications.

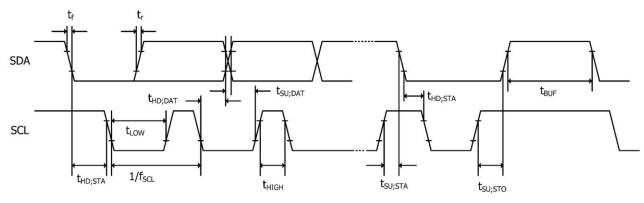

Figure 3: Timing definition for F/S mode of operation for I2C bus

#### **6.4 SPI Characteristics**

#### Table 14: SPI I/O Characteristics

| Symbol                  | Parameter                          | Conditions | MIN          | MAX | Units |

|-------------------------|------------------------------------|------------|--------------|-----|-------|

| fsск <sup>(1)</sup>     | SPI Clock frequency                |            |              | 10  | MHz   |

| tscк <sup>(1)</sup>     | SPI Clock period                   |            | 100          |     | ns    |

| tH <sup>(1)</sup>       | SCK High Time                      |            | 50           |     | ns    |

| tL <sup>(1)</sup>       | SCK Low Time                       |            | 50           |     | ns    |

| tr <sup>(2)</sup>       | SCK Rise time                      |            |              | 25  | ns    |

| tf <sup>(2)</sup>       | SCK Fall Time                      |            |              | 25  | ns    |

| tps (1)                 | Data input setup time wrt SCK edge |            | 30           |     | ns    |

| tdh (1)                 | Data input hold time wrt SCK edge  |            | 30           |     | ns    |

| tvd <sup>(1)</sup>      | Data out valid after SCK edge      |            |              | 30  | ns    |

| tdr (2)                 | Data out rise time                 |            |              | 30  | ns    |

| tdf <sup>(2)</sup>      | Data out fall time                 |            |              | 30  | ns    |

| thd (1)                 | Data out hold time after SCK edge  |            | 5            |     | ns    |

| tsu(ssn) <sup>(1)</sup> | SSN low to first SCK edge          |            | 1 SCK Period |     | ns    |

#### Notes:

- 1) Guaranteed by design, not production tested.

- 2) Provided as a design limit only, neither production tested or guaranteed.

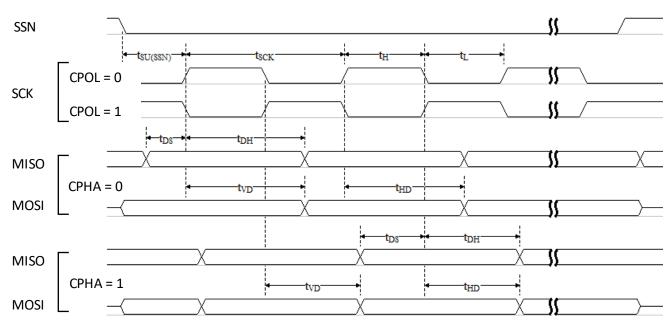

Figure 4: SPI Timing Diagram (Master Mode)

#### 32-Bit Arm® Cortex®-M0+ Microcontroller

### UT32M0R500

#### 6.5 Oscillator Characteristics

#### 6.5.1 Internal Clock Source Characteristics

#### **Table 15: Internal Clock Source Characteristics**