### UT16MX113/114/115

### Features

- 16-to-1 Analog Mux

- 100Ω Signal paths (typical)

- 5V single analog supply

- Rail-to-Rail signal handling

- Asynchronous RESET input

- SPI™/QSPI™ and MICROWIRE™ compatible serial interface (UT16MX115)

- Asynchronous parallel input Interface (UT16MX113)

- Synchronous parallel input Interface (UT16MX114)

- LVCMOS/LVTTL compatible inputs

- 2kV ESD Protection (per MIL-STD-883, Method 3015.7)

- Operational environment:

- Total ionizing dose: 300 krad(Si)

- SEL immune to a LET of 110 MeV-cm<sup>2</sup>/mg

- SEU immune to a LET of 62.3 MeV-cm<sup>2</sup>/mg

- Packaging: 28-lead Ceramic Flatpack

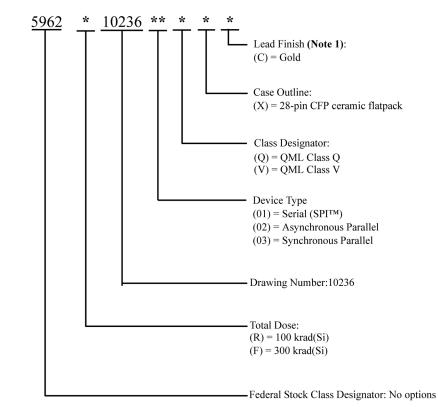

- Standard Microcircuit Drawing 5962-10236

- QML Q, QML V

### Introduction

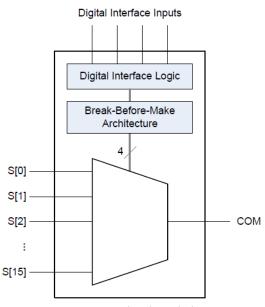

The UT16MX113/114/115 are low voltage analog multiplexers with a convenient LVCMOS (3.3V) or CMOS digital interface. The analog muxes have Break- Before-Make architecture with a low channel resistance. The muxes support rail-to-rail input signal levels. The multiplexer supports serial (SPI<sup>™</sup>), or parallel (asynchronous or synchronous) interface.

The UT16MX113/114/115 operates with a single 5V ( $\pm$ 10%) analog power supply. An external 3.3V digital voltage supply is required, for the digital circuitry and the digital I/O.

Figure 1. UT16MX113/114/115 Block Diagram

# UT16MX113/114/115

### **Functional Description**

All mux decoding (whether for the UT16MX113, UT16MX114, or UT16MX115 device) operation utilizes a Break-Before-Make process to prevent shorting between analog inputs during address transitions.

### UT16MX113:

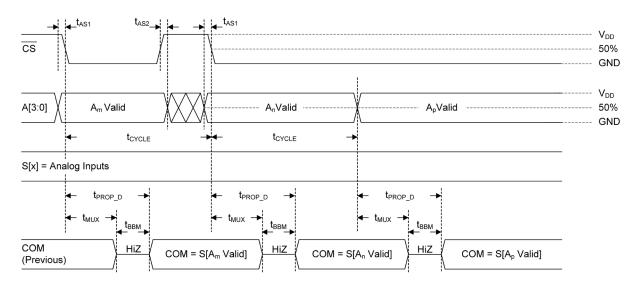

The UT16MX113 utilizes a parallel interface which operates in asynchronous mode much like discrete logic switches. The UT16MX113 requires the following operation in order to properly initialize the part following power-up: All address states for the A[3:0] address lines must be exercised following AVDD power-up to ensure correct addressing. Once this operation has been completed, normal asynchronous addressing can then be used to select the desired input channel (i.e. one of S[15:0]) to connect to the COM output. The S[15:0] analog channels are routed asynchronously via the binary decoding of A[3:0] static logic levels after initialization. The address pins A[3:0] are required to hold static levels for proper mux operation. Any change in A[3:0] pins directs the COM connection to the appropriate S[x] input after approximately 100ns propagation delay (including the Break-Before-Make delay). All bits (A[3:0]) of any address change should be received by the UT16MX113 within 18 ns of the first bit change for proper operation. The asynchronous parallel interface mode requires  $\overline{CS}$  to be low for accepting a change on the address pins A[3:0]. When  $\overline{CS}$  is high, the UT16MX113 disables the address pins A[3:0], as well as holding the last valid address state, thereby mitigating against any single-event upsets or transients on the address bus.

### UT16MX114:

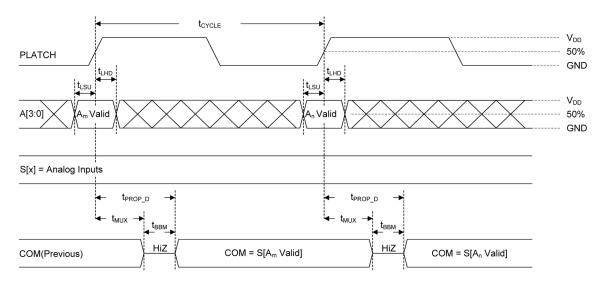

The UT16MX114 utilizes a parallel interface which operates in a synchronous mode which utilizes the PLATCH input as the latching clock. Upon rising edge of PLATCH, logic level at the A[3:0] pins will be registered and retained internally to decode the mux. Based on the values of the A[3:0] pins, COM is connected to the appropriate S[x] input after approximately 100ns propagation delay (including the Break-Before-Make delay).

### UT16MX115:

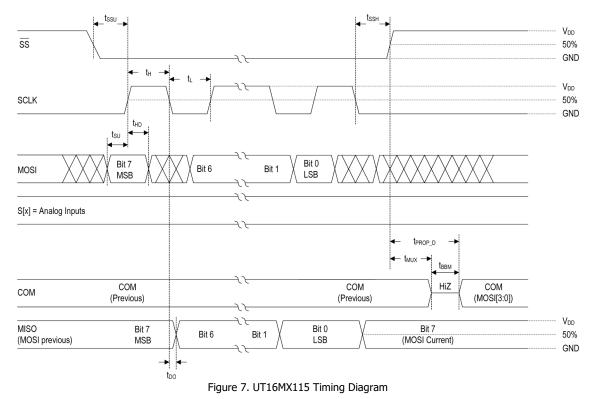

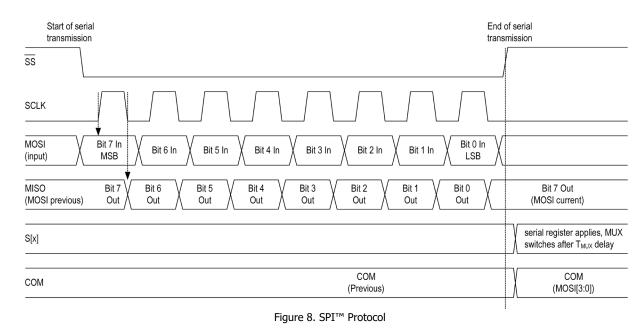

The UT16MX115 utilizes a serial interface that supports the standard that is compatible with MICROWIRE<sup>™</sup>, SPI<sup>™</sup>, and QSPI<sup>™</sup>. The UT16MX115 SPI<sup>™</sup> interface can be depicted as an 8-bit serial shift register controlled by  $\overline{SS}$ , clocked by the rising edge of SCLK. The 8-bit shift register is for compatibility purposes, even though this UT16MX115 serial address setting requires only 4 bits. The four LSB of the 8-bit shift register are the four bits decoding the mux address. When shifting data into the part, the MSB enters the part first. The four MSB may be set to zeroes, e.g., the 8-bit command "00001001" would set the mux to connect COM to S[9].

The UT16MX115 is considered a slave SPI<sup>TM</sup> device with MOSI (Master Out Slave In) as the data input pin to the device. The data is shifted with D7 as the first bit into the shift register, and also the first bit out to the MISO (Master In Slave Out) output pin after eight clock cycles of SCLK. The signal on the  $\overline{SS}$  pin defines the window when the address bits are shifted into the device. This occurs when signal on  $\overline{SS}$  is low. Only when  $\overline{SS}$  is high at the close of the shifting window, does the mux decoding get updated and COM is directed to the decoded S[x] input (after Break-Before-Make delay).

# UT16MX113/114/115

### **SPI™** Operations:

The SPI<sup>TM</sup> (Serial Peripheral Interface) is implemented as a synchronous 8-bit serial shift register controlled by four pins: MOSI, MISO, SCLK, and  $\overline{SS}$ . This is compatible with the SPI<sup>TM</sup>/QSPI<sup>TM</sup> standard as defined by Motorola on the MC68HCxx line of microcontrollers. This SPI<sup>TM</sup> also conforms to the MICROWIRE<sup>TM</sup> interface, an SPI<sup>TM</sup> subset interface, as defined by National Semiconductor.

The UT16MX115 SPI<sup>m</sup> is always a slave device, where MOSI, SCLK, and  $\overline{SS}$  are controlled by a master device. MISO output is used as receiving slave data or to daisy chain several SPI<sup>m</sup> devices in appropriate applications.

The MUX select functionality is controlled by the four LSB of the 8-bit SPI<sup>™</sup> shift registers. When shifting, the first SCLK rising edge clocks in the MSB first. The first falling edge of the SCLK clocks out the 6th bit of the current values in the SPI<sup>™</sup> registers, since the 7th bit already appears at the MISO at the start of a serial transmission before the first SCLK (Figures 7 and 8).

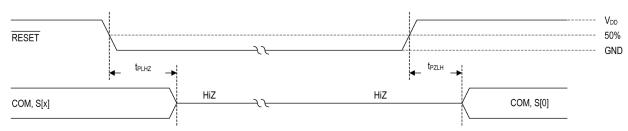

### Reset Function (UT16MX114/115 Only):

The RESET pin is used to reset all internal logic circuits. RESET held low also keeps all COM and S[15:0] analog I/Os in a high impedance state. This is the recommended condition at system power-up.

Asserting  $\overline{\text{RESET}}$  (active low) resets all of the internal address decoding registers to 0, thus steering the COM to connect to S[0] while in the high impedance state. When  $\overline{\text{RESET}}$  is de-asserted (high), both COM and S[0] will come out of the high impedance state and COM will be driven by S[0].

| Pin No. | Name             | I/O    | Туре    | Description                                           |

|---------|------------------|--------|---------|-------------------------------------------------------|

| 1       | AV <sub>DD</sub> |        | Power   | Analog Positive Supply <sup>1</sup>                   |

| 2       | NC               |        |         | No Connection                                         |

| 3       | NC               |        |         | No Connection                                         |

| 4-11    | S[15:8]          | Input  | Analog  | Muxed Inputs                                          |

| 12      | GND              |        | Power   | Digital Ground                                        |

| 13      | V <sub>DD</sub>  |        | Power   | Digital Positive Supply <sup>1</sup>                  |

| 14      | A3               | Input  | Digital | Parallel A3                                           |

| 15      | A2               | Input  | Digital | Parallel A2                                           |

| 16      | A1               | Input  | Digital | Parallel A1                                           |

| 17      | A0               | Input  | Digital | Parallel A0                                           |

| 18      | 20               | Input  | Digital | Active Low Parallel Chip Select with Internal Pull-up |

| 19-26   | S[0:7]           | Input  | Analog  | Muxed Inputs                                          |

| 27      | AV <sub>SS</sub> |        | Power   | Analog Negative Supply                                |

| 28      | СОМ              | Output | Analog  | Muxed Output <sup>2</sup>                             |

### Table 1: UT16MX113 Pin Description

Notes:

1) For proper operation,  $V_{DD}$  must be applied before or simultaneously with  $AV_{DD}$ .

2) Continuous operation with low load resistance is not recommended. (See Figure 11)

### UT16MX113/114/115

|      | r  |           |    | 1 |                        |

|------|----|-----------|----|---|------------------------|

| AVDD | 1  |           | 28 |   | СОМ                    |

| NC   | 2  |           | 27 |   | AVSS                   |

| NC   | 3  |           | 26 |   | S7                     |

| S15  | 4  |           | 25 |   | S6                     |

| S14  | 5  |           | 24 |   | S5                     |

| S13  | 6  |           | 23 |   | S4                     |

| S12  | 7  | UT16MX113 | 22 |   | S3                     |

| S11  | 8  |           | 21 |   | S2                     |

| S10  | 9  |           | 20 |   | S1                     |

| S9   | 10 |           | 19 |   | S0                     |

| S8   | 11 |           | 18 |   | $\overline{\text{CS}}$ |

| GND  | 12 |           | 17 |   | A0                     |

| VDD  | 13 |           | 16 |   | A1                     |

| A3   | 14 |           | 15 |   | A2                     |

|      |    |           |    |   |                        |

### Table 2: UT16MX114 Pin Description

| Pin No. | Name             | I/O    | Туре    | Description                            |  |

|---------|------------------|--------|---------|----------------------------------------|--|

| 1       | AV <sub>DD</sub> |        | Power   | Analog Positive Supply <sup>1</sup>    |  |

| 2       | RESET            | Input  | Digital | Active Low Reset with Internal Pull-up |  |

| 3       | PLATCH           | Input  | Digital | Parallel Latch with Internal Pull-down |  |

| 4-11    | S[15:8]          | Input  | Analog  | Muxed Inputs                           |  |

| 12      | GND              |        | Power   | Digital Ground                         |  |

| 13      | V <sub>DD</sub>  |        | Power   | Digital Positive Supply <sup>1</sup>   |  |

| 14      | A3               | Input  | Digital | Parallel A3                            |  |

| 15      | A2               | Input  | Digital | Parallel A2                            |  |

| 16      | A1               | Input  | Digital | al Parallel A1                         |  |

| 17      | A0               | Input  | Digital | Parallel A0                            |  |

| 18      | NC               |        |         | No Connection                          |  |

| 19-26   | S[0:7]           | Input  | Analog  | Muxed Inputs                           |  |

| 27      | AVss             |        | Power   | Analog Negative Supply                 |  |

| 28      | COM              | Output | Analog  | Muxed Output <sup>2</sup>              |  |

#### Notes:

1) For proper operation,  $V_{\text{DD}}$  must be applied before or simultaneously with  $AV_{\text{DD}}$ .

2) Continuous operation with low load resistance is not recommended. (See Figure 11).

# DATASHEET

### Analog Multiplexer

# UT16MX113/114/115

Figure 3. UT16MX114 Pinout

### Table 3: UT16MX115 Pin Description

| Pin No. | Name             | I/O    | Туре    | Description                                          |

|---------|------------------|--------|---------|------------------------------------------------------|

| 1       | AV <sub>DD</sub> |        | Power   | Analog Positive Supply <sup>1</sup>                  |

| 2       | RESET            | Input  | Digital | Active Low Reset with Internal Pull-up               |

| 3       | NC               |        |         | No Connection                                        |

| 4-11    | S[15:8]          | Input  | Analog  | Muxed Inputs                                         |

| 12      | GND              |        | Power   | Digital Ground                                       |

| 13      | V <sub>DD</sub>  |        | Power   | Digital Positive Supply <sup>1</sup>                 |

| 14      | NC               |        |         | No Connection                                        |

| 15      | SCLK             | Input  | Digital | SPI™ Clock                                           |

| 16      | MOSI             | Input  | Digital | Master-out-Slave-in (Din)                            |

| 17      | MISO             | Output | Digital | Master-in-Slave-out (Dout)                           |

| 18      | SS               | Input  | Digital | SPI <sup>™</sup> Shift Control with Internal Pull-up |

| 19-26   | S[0:7]           | Input  | Analog  | Muxed Inputs                                         |

| 27      | AV <sub>SS</sub> |        | Power   | Analog Negative Supply                               |

| 28      | СОМ              | Output | Analog  | Muxed Output <sup>2</sup>                            |

### Notes:

1) For proper operation,  $V_{\text{DD}}$  must be applied before or simultaneously with  $AV_{\text{DD}}.$

2) Continuous operation with low load resistance is not recommended. (See Figure 11)

### UT16MX113/114/115

### Table 4: UT16MX113 Truth Table

| CS | A3 | A2 | A1 | AO | СОМ                   |

|----|----|----|----|----|-----------------------|

| 1  | х  | Х  | Х  | Х  | Previous Decide State |

| 0  | 0  | 0  | 0  | 0  | S0                    |

| 0  | 0  | 0  | 0  | 1  | S1                    |

| 0  | 0  | 0  | 1  | 0  | S2                    |

| 0  | 0  | 0  | 1  | 1  | S3                    |

| 0  | 0  | 1  | 0  | 0  | S4                    |

| 0  | 0  | 1  | 0  | 1  | S5                    |

| 0  | 0  | 1  | 1  | 0  | S6                    |

| 0  | 0  | 1  | 1  | 1  | S7                    |

| 0  | 1  | 0  | 0  | 0  | S8                    |

| 0  | 1  | 0  | 0  | 1  | S9                    |

| 0  | 1  | 0  | 1  | 0  | S10                   |

| 0  | 1  | 0  | 1  | 1  | S11                   |

| 0  | 1  | 1  | 0  | 0  | S12                   |

| 0  | 1  | 1  | 0  | 1  | S13                   |

| 0  | 1  | 1  | 1  | 0  | S14                   |

| 0  | 1  | 1  | 1  | 1  | S15                   |

## UT16MX113/114/115

### Table 5: UT16MX114 Truth Table

| RESET | PLATCH      | A3 | A2 | A1 | AO | СОМ                         |

|-------|-------------|----|----|----|----|-----------------------------|

| 0     | Х           | Х  | Х  | Х  | Х  | Tri-State (S[15:0] and COM) |

| 1     | Rising Edge | 0  | 0  | 0  | 0  | S0                          |

| 1     | Rising Edge | 0  | 0  | 0  | 1  | S1                          |

| 1     | Rising Edge | 0  | 0  | 1  | 0  | S2                          |

| 1     | Rising Edge | 0  | 0  | 1  | 1  | S3                          |

| 1     | Rising Edge | 0  | 1  | 0  | 0  | S4                          |

| 1     | Rising Edge | 0  | 1  | 0  | 1  | S5                          |

| 1     | Rising Edge | 0  | 1  | 1  | 0  | S6                          |

| 1     | Rising Edge | 0  | 1  | 1  | 1  | S7                          |

| 1     | Rising Edge | 1  | 0  | 0  | 0  | S8                          |

| 1     | Rising Edge | 1  | 0  | 0  | 1  | S9                          |

| 1     | Rising Edge | 1  | 0  | 1  | 0  | S10                         |

| 1     | Rising Edge | 1  | 0  | 1  | 1  | S11                         |

| 1     | Rising Edge | 1  | 1  | 0  | 0  | S12                         |

| 1     | Rising Edge | 1  | 1  | 0  | 1  | S13                         |

| 1     | Rising Edge | 1  | 1  | 1  | 0  | S14                         |

| 1     | Rising Edge | 1  | 1  | 1  | 1  | S15                         |

### **Operational Environment**

| Parameter                          | Limit | Units                   |

|------------------------------------|-------|-------------------------|

| Total Ionizing Dose (TID)          | 300   | krad(Si)                |

| Single Event Latchup (SEL)         | >110  | MeV-cm <sup>2</sup> /mg |

| Single Event Upset Threshold (SEU) | >62.3 | MeV-cm <sup>2</sup> /mg |

### Absolute Maximum Ratings<sup>1</sup>

| Symbol           | Parameter                                      | Limits          |

|------------------|------------------------------------------------|-----------------|

| AV <sub>DD</sub> | Analog Positive Supply Voltage                 | 7.5V            |

| AVss             | Analog Negative Supply Voltage                 | -0.3V           |

| V <sub>DD</sub>  | Digital Supply Voltage (referenced to GND)     | 4.5V            |

| PD               | Static Power Dissipation                       | 150 mW          |

| τ                | Junction Temperature                           | -55°C to +130°C |

| Tstg             | Storage Temperature                            | -65°C to +150°C |

| ESDнвм           | Electrostatic Discharge using Human Body Model | 2kV             |

Notes:

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

# UT16MX113/114/115

### **Recommended Operating Conditions**

| Symbol           | Parameter                                   | Limits                               |

|------------------|---------------------------------------------|--------------------------------------|

| AV <sub>DD</sub> | Analog Positive Supply Voltage              | 4.5V to 5.5V                         |

| AV <sub>SS</sub> | Analog Negative Supply Voltage              | 0.0V                                 |

| V <sub>DD</sub>  | Digital Supply Voltage (referenced to GND)  | 3.0V to 3.6V                         |

| V <sub>IN</sub>  | Analog Switch Input Voltage                 | AV <sub>ss</sub> to AV <sub>DD</sub> |

| VI               | Digital Input Voltage                       | 0V to V <sub>DD</sub>                |

| Tc               | Case Operating Temperature Range            | -55°C to +125°C                      |

| τı               | Junction Operating Temperature <sup>1</sup> | -55°C to +130°C                      |

#### Note:

1) Thermal resistance,  $\Theta_{3C}$ , of junction-to-case is 4.8°C/W.

### **DC Electrical Characteristics<sup>1</sup>**

$(AV_{DD}=5.0V \pm 0.5V, V_{DD}=3.3V \pm 0.3V, GND=0V; -55^{\circ}C \le T_{C} \le +125^{\circ}C)$

| Symbol                       | Parameter                                                                                                          | Condition                                                                                              | MIN                  | ТҮР | MAX               | Unit           |

|------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|-----|-------------------|----------------|

| VIL                          | Digital input low                                                                                                  | V <sub>DD</sub> = 3.0V                                                                                 | -0.3                 |     | 0.8               | V              |

| VIH                          | Digital input high                                                                                                 | $V_{DD} = 3.0V$                                                                                        | 2.0                  |     |                   | V              |

| Vol                          | Digital output low (UT16MX115)                                                                                     | $\begin{array}{l} V_{\text{DD}}=3.0V\\ I_{\text{OL}}=100\mu\text{A} \end{array}$                       |                      |     | 0.2               | v              |

| VOL                          |                                                                                                                    | $V_{DD} = 3.0V$<br>$I_{OL} = 2mA$                                                                      |                      |     | 0.4               | v              |

| Vон                          | Digital output high (UT16MX115)                                                                                    | V <sub>DD</sub> = 3.0V<br>I <sub>OH</sub> = -100µА                                                     | 2.8                  |     |                   | v              |

| VOH                          |                                                                                                                    | V <sub>DD</sub> = 3.0V<br>I <sub>OH</sub> = -2mA                                                       | 2.4                  |     |                   | v              |

| R <sub>ON</sub>              | On resistance                                                                                                      |                                                                                                        | 40                   | 145 | 300               | Ω              |

| Ioff                         | Analog I/O leakage current (switch off) <sup>2</sup>                                                               | $\begin{array}{l} AV_{DD} = 5.5V \\ V_{DD} = 3.6V \\ V_{IN} = AV_{SS} \mbox{ or } AV_{DD} \end{array}$ | -1.6                 |     | 1.6               | μΑ             |

| I <sub>IL</sub>              | Digital input current low<br>LVCMOS / LVTTL inputs<br>Inputs with pull-up<br>Inputs with a pull-down               | $V_{DD} = 3.6V$<br>$V_{IL} = GND$                                                                      | -1.0<br>-380<br>-5.0 |     | 1.0<br>-20<br>5.0 | μΑ<br>μΑ<br>μΑ |

| Іін                          | Digital input current high<br>LVCMOS / LVTTL inputs<br>Inputs with pull-up <sup>3</sup><br>Inputs with a pull-down | $V_{DD} = 3.6V$<br>$V_{IH} = V_{DD}$                                                                   | -1.0<br>-60<br>20    |     | 1.0<br>60<br>380  | μΑ<br>μΑ<br>μΑ |

| QIDD                         | Quiescent analog supply current                                                                                    | $\begin{array}{l} AV_{DD} = 5.5V \\ V_{DD} = 3.6V \\ V_{IH} = V_{DD} \\ V_{IL} = GND \end{array}$      |                      |     | 10                | μΑ             |

| $Q_{\text{IDD}\_\text{VDD}}$ | Quiescent digital supply current                                                                                   | $AV_{DD} = 5.5V$                                                                                       |                      |     | 250               | μA             |

### UT16MX113/114/115

| $V_{DD} = 3.6V$<br>$V_{IH} = V_{DD}$ |  |  |

|--------------------------------------|--|--|

| $V_{IL} = GND$                       |  |  |

#### Notes:

- For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured (see ordering information).

- 2) This parameter cannot be tested on COM for the UT16MX113 device because the pin is continuously on.

- 3) This parameter tested with PLATCH held low on the UT16MX114 device.

### AC Electrical Characteristics 1,2

$(AV_{DD}=5.0V \pm 0.5V, V_{DD}=3.3V \pm 0.3V, GND=0V; -55^{\circ}C \le T_{C} \le +125^{\circ}C)$

| Symbol           | Parameter                                                                     | Condition                                                                                                                           | MIN | ТҮР | MAX | Unit |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| CIN              | Input capacitance (switch off) <sup>3</sup>                                   | F <sub>IN</sub> =1MHz @ 0V                                                                                                          |     | 40  | 50  | pF   |

| CIN_DIGITAL      | Input digital capacitance <sup>3</sup>                                        | FIN=1MHz @ 0V                                                                                                                       |     | 46  | 55  | pF   |

| COUT             | Output capacitance at COM <sup>3</sup>                                        | F <sub>IN</sub> =1MHz @ 0V                                                                                                          |     | 68  | 80  | pF   |

| O <sub>ISO</sub> | Off isolation feed through attenuation (switch off) <sup>4</sup>              | $R_L$ =600 $\Omega$<br>$C_L$ =50pF<br>$F_{IN}$ =1kHz sine wave                                                                      |     |     | -80 | dB   |

| BW               | Bandwidth (frequency response) <sup>4</sup>                                   | $\begin{split} R_{SOURCE} &= 50 \Omega \\ R_L &= 2.2 M \Omega \\ C_L &= 12 p F \\ V_{IN} &= 1 V p \text{-} p \end{split}$           | 51  |     |     | MHz  |

| Xtalk2           | Cross talk (between any 2 channels) <sup>4</sup>                              | $R_L=1k\Omega$<br>$C_L=50pF$<br>$F_{IN}=1kHz$ sine wave                                                                             |     |     | -80 | dB   |

| ts               | Settling time of output at COM within 1% of final output voltage <sup>4</sup> | Within 1% of final<br>output voltage<br>$R_L=100k\Omega$<br>$C_L=50pF$                                                              |     |     | 120 | ns   |

| THD              | Total Harmonic Distortion <sup>4</sup>                                        | $ \begin{array}{l} R_L = 1 k \Omega \\ C_L = 50 p F \\ F_{IN} = 1 M Hz \mbox{ sine wave} \\ V_{IN} = 5 V p \mbox{-} p \end{array} $ |     |     | 5.0 | %    |

- For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured (see ordering information).

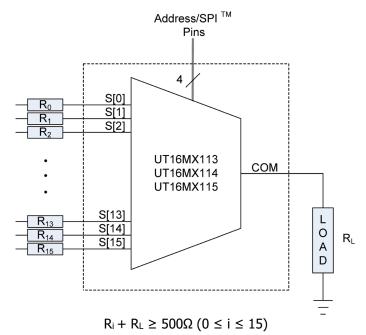

- 2) Continuous operation with low load resistance is not recommended. (See Figure 11)

- 3) Parameters guaranteed by characterization.

- 4) Parameters guaranteed by design.

# UT16MX113/114/115

### Digital Timing Characteristics (UT16MX113)<sup>1,2</sup>

(AV\_{DD}=5.0V  $\pm$  0.5V, V\_{DD}=3.3V  $\pm$  0.3V, GND=0V; -55°C  $\leq$  T\_C  $\leq$  +125°C)

| Symbol           | Parameter                                                                                                                                     | Condition                                              | MIN | ТҮР | MAX | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

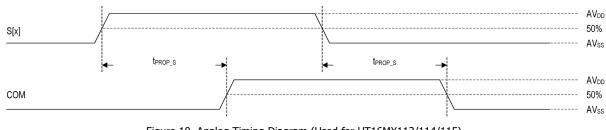

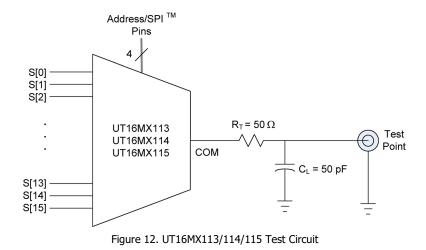

| tprop_s          | Propagation delay of analog input (S[x])<br>to analog output (COM) measured at<br>50%                                                         | $R_T=50\Omega$<br>$C_L=50pF$<br>See Figures 10 & 12    |     |     | 25  | ns   |

| tprop_d          | Propagation delay of any changes in the digital inputs (A[3:0], $\overline{CS}$ , PLATCH, $\overline{SS}$ ) affecting the analog output (COM) | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 5 & 12 | 25  |     | 140 | ns   |

| tмux             | Mux decoding time                                                                                                                             | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 5 & 12 |     |     | 50  | ns   |

| tввм             | Break-Before-Make-Delay                                                                                                                       | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 5 & 12 | 15  |     | 90  | ns   |

| t <sub>AS1</sub> | The minimum amount of time required for the address signals (A[3:0]) to be stable before the falling edge of $\overline{CS}^3$                | See Figure 5                                           | 3.0 |     |     | ns   |

| tas2             | The minimum amount of time required for the address signals (A[3:0]) to be stable after the rising edge of $\overline{CS}^3$                  | See Figure 5                                           | 5.0 |     |     | ns   |

- 1) For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured (see ordering information).

- 2) Continuous operation with low load resistance is not recommended. (See Figure 11)

- 3) Guaranteed by design.

# UT16MX113/114/115

### Digital Timing Characteristics (UT16MX114)<sup>1,2</sup>

$(AV_{DD}=5.0V \pm 0.5V, V_{DD}=3.3V \pm 0.3V, GND=0V; -55^{\circ}C \le T_{C} \le +125^{\circ}C)$

| Symbol  | Parameter                                                                                                                                     | Condition                                               | MIN | ТҮР | MAX | Unit |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| tprop_s | Propagation delay of analog input (S[x]) to analog output (COM) measured at $50\%$                                                            | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 10 & 12 |     |     | 25  | ns   |

| tprop_d | Propagation delay of any changes in the digital inputs (A[3:0], $\overline{CS}$ , PLATCH, $\overline{SS}$ ) affecting the analog output (COM) | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 6 & 12  | 25  |     | 140 | ns   |

| tмих    | Mux decoding time                                                                                                                             | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 6 & 12  |     |     | 50  | ns   |

| tввм    | Break-Before-Make-Delay                                                                                                                       | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 6 & 12  | 15  |     | 90  | ns   |

| tpzlh   | Output enable time from HiZ to low or high once $\overrightarrow{\text{RESET}}$ is pulled high                                                | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 9 & 12  |     |     | 90  | ns   |

| tplhz   | Output disable time from low or high to<br>HiZ once RESET is pulled low                                                                       | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 9 & 12  |     |     | 55  | ns   |

| t∟su    | Address setup time wrt rising edge<br>PLATCH                                                                                                  | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 6 & 12  | 5.0 |     |     | ns   |

| tlhd    | Address hold time wrt rising edge PLATCH                                                                                                      | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 6 & 12  | 10  |     |     | ns   |

- For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured (see ordering information).

- 2) Continuous operation with low load resistance is not recommended. (See Figure 11)

**RELEASED 2/19**

# UT16MX113/114/115

### Digital Timing Characteristics (UT16MX115)<sup>1,2</sup>

$(AV_{DD}=5.0V \pm 0.5V, V_{DD}=3.3V \pm 0.3V, GND=0V; -55^{\circ}C \le T_{C} \le +125^{\circ}C)$

| Symbol            | Parameter                                                                                                                                     | Condition                                              | MIN | ТҮР | MAX | Unit |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| tprop_s           | Propagation delay of analog input (S[x]) to analog output (COM) measured at $50\%$                                                            | $R_T=50\Omega$<br>$C_L=50pF$<br>See Figures 10 & 12    |     |     | 25  | ns   |

| tprop_d           | Propagation delay of any changes in the digital inputs (A[3:0], $\overline{CS}$ , PLATCH, $\overline{SS}$ ) affecting the analog output (COM) | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 7 & 12 | 25  |     | 140 | ns   |

| tмux              | Mux decoding time                                                                                                                             | $R_T=50\Omega$<br>$C_L=50pF$<br>See Figures 7 & 12     |     |     | 50  | ns   |

| t <sub>ввм</sub>  | Break-Before-Make-Delay                                                                                                                       | $R_T=50\Omega$<br>$C_L=50pF$<br>See Figures 7 & 12     | 15  |     | 90  | ns   |

| <b>t</b> pzlh     | Output enable time from HiZ to low or high once RESET is pulled high                                                                          | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 9 & 12 |     |     | 90  | ns   |

| t <sub>PLHZ</sub> | Output disable time from low or high to<br>HiZ once RESET is pulled low                                                                       | $R_T = 50\Omega$<br>$C_L = 50pF$<br>See Figures 9 & 12 |     |     | 55  | ns   |

| <b>f</b> sclk     | SCLK frequency                                                                                                                                | See Figure 7                                           |     |     | 2.0 | MHz  |

| tн                | SCLK high time                                                                                                                                | See Figure 7                                           | 190 |     |     | ns   |

| t∟                | SCLK low time                                                                                                                                 | See Figure 7                                           | 190 |     |     | ns   |

| $t_{SSU}$         | First SCLK setup time (for shifting window)                                                                                                   | See Figure 7                                           | 7.0 |     |     | ns   |

| tssh              | Last SCLK hold time (for shifting window)                                                                                                     | See Figure 7                                           | 10  |     |     | ns   |

| t <sub>su</sub>   | Data In (MOSI) setup time wrt rising edge<br>SCLK                                                                                             | See Figure 7                                           | 3.0 |     |     | ns   |

| t <sub>HD</sub>   | Data In (MOSI) hold time wrt rising edge<br>SCLK                                                                                              | See Figure 7                                           | 5.0 |     |     | ns   |

| t <sub>DO</sub>   | Data out (MISO) valid (after falling edge<br>of SCLK)                                                                                         | C∟=50pF<br>See Figure 7                                |     |     | 43  | ns   |

| t <sub>DR</sub>   | Data out (MISO) rise time                                                                                                                     | 10-90% V <sub>DD</sub> C <sub>L</sub> =50pF            |     |     | 30  | ns   |

| t <sub>DF</sub>   | Data out (MISO) fall time                                                                                                                     | 10-90% V <sub>DD</sub> C <sub>L</sub> =50pF            |     |     | 20  | ns   |

- For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured (see ordering information).

- 2) Continuous operation with low load resistance is not recommended. (See Figure 11)

**RELEASED 2/19**

Analog Multiplexer

# UT16MX113/114/115

### UT16MX113/114/115

### **Timing Diagrams**

### Multiplexer Asynchronous Parallel Timing (UT16MX113)

#### Notes:

- 1)  $\overline{\text{CS}}$  may be held in a continuous low state, holding  $\overline{\text{CS}}$  high provides protection for false address change.

- 2) t<sub>CYCLE</sub> is the minimum cycle time between the falling edges of  $\overline{\text{CS}}$  and/or any address changes. If t<sub>CYCLE</sub> is shorter than t<sub>PROP\_D</sub>, an addressing error may occur.

- 3) All bits (A[3:0]) of any address change should be received by the UT16MX113 within 18ns of the first bit change for proper operation.

### Multiplexer Synchronous Parallel Timing (UT16MX114)

- 1) When PLATCH is in a high or low state, it provides protection for false address change.

- 2) tcycle must not be less than the maximum value of tPROP\_D.

### UT16MX113/114/115

### Multiplexer Serial Timing (UT16MX115)

### Multiplexer Load Conditions for Test (UT16MX113/114/115)

Note:

PIONEERING ADVANCED ELECTRONICS

1) See FIGURE 7. Multiplexer serial timing (UT16MX115), for detailed timing.

### UT16MX113/114/115

### Multiplexer RESET Enable/Disable Timing (UT16MX114/115)

Figure 9: RESET Timing Diagram (Used for UT16MX114/115 only)

#### Note:

1) S[x] represents the analog signal channel connected to COM prior to the falling edge of  $\overline{\text{RESET}}$ .

### Multiplexer Analog Timing (UT16MX113/114/115)

Figure 10. Analog Timing Diagram (Used for UT16MX113/114/115)

### Note:

1) S[x] represents the analog signal channel connected to COM while in active mode of all device types with the address already set and all digital inputs held constant.

### UT16MX113/114/115

### Minimum Multiplexer Total Path Resistance (UT16MX113/114/115)

Figure 11. Minimum Total Path Resistance for Continuous DC Operation on Any Single Channel

#### Note:

1) Continuous DC operation on any single channel where Ri + RL < 500  $\Omega$  will degrade device reliability and performance.

### Multiplexer Load Conditions for Test (UT16MX113/114/115)

## UT16MX113/114/115

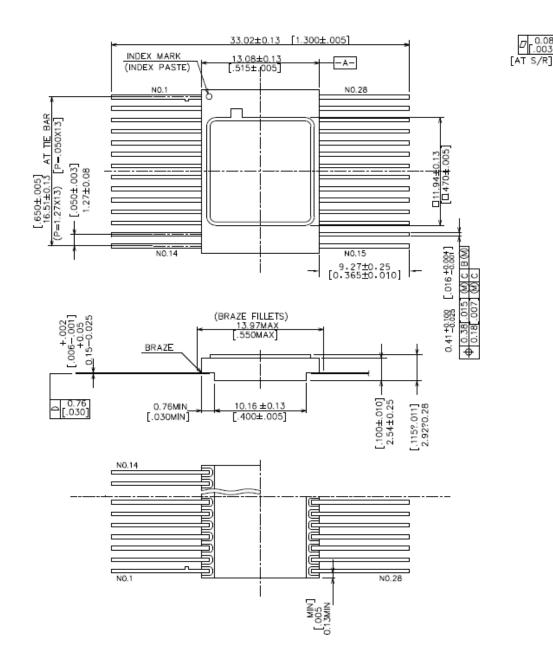

### Packaging

- 1) Gold plated 100 to 225 microinches over electroplated nickel 100 to 350 microinches per MIL-PRF-38535

- 2) Seal ring is electrically connected to VSS

# UT16MX113/114/115

### Trademarks:

SPI<sup>™</sup> /QSPI<sup>™</sup> are trademarks of Motorola, Inc. MICROWIRE<sup>™</sup> is a trademark of National Semiconductor

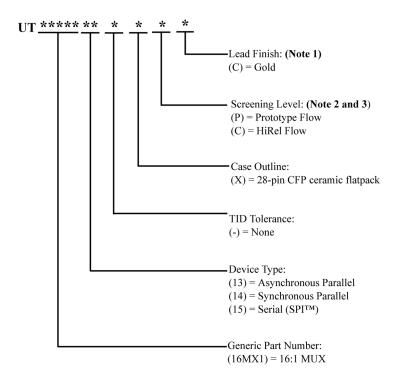

### **Ordering Information**

### UT16MX113/114/115 Analog Multiplexer

- 1) Lead finish is "C" (Gold) only.

- 2) Prototype flow per CAES Manufacturing Flows Document. Tested at 25°C only. Lead finish is Gold "C" only. Radiation neither tested nor guaranteed.

- 3) HiRel Flow per CAES Manufacturing Flows Document.

### UT16MX113/114/115

### UT16MX113/114/115 Analog Multiplexer: SMD

#### Note:

1) Lead finish is "C" (Gold) only.

### **Datasheet Revision History**

| 2-29 | Page 2: Functional Description edits                                                                           | BM |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | UT16MX113:                                                                                                     |    |

|      | UT16MX113 requires the following operation in order to properly initialize the part following power-up: All    |    |

|      | address states for the A[3;0] address lines must be exercised following AVDD power-up to ensure correct        |    |

|      | addressing. Once this operation has been completed, normal asychronous addressing can then be used to          |    |

|      | select the desired input channel (i.e. one of S[15:0]) to connect to the COM output. The S[15:0] analog        |    |

|      | channels are routed asynchronously via the binary decoding of A[3:0] static logic levels after initialization. |    |

DATASHEET

#### Analog Multiplexer

### UT16MX113/114/115

### Datasheet Definitions

|                       | DEFINITION                                                                                                                                                                                                                                                                                              |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet <b>is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                             |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.