| PRODUCT NAME   | MANUFACTURER<br>PART NUMBER | SMD #      | DEVICE TYPE | INTERNAL PIC<br>NUMBER |

|----------------|-----------------------------|------------|-------------|------------------------|

| 64Mb NOR FLASH | UT8QNF8M8                   | 5962-12204 | 01 - 04     | RQ11                   |

#### **Table 1: Cross Reference of Applicable Products**

#### **Overview**

The UT8QNF8M8 64Mbit NOR Flash Memory specifies a maximum total ionizing dose of 50 krad(Si) in an operational environment where the device is unpowered for 90% of its mission life. The application consistent with the NOR Flash being unpowered for the greater part of its design life is when the device is implemented as boot load memory. As the boot loader, the device is typically only accessed during system power up or processor reset. During the time after the boot code has been read by the processor, the device is idle and therefore may be powered down and isolated. A good method for the power down and isolation functionality is to implement the NOR Flash interface using a combination of Bus Switch products.

#### **Table of Contents**

| 1 | Scope                                       | 2 |

|---|---------------------------------------------|---|

| 2 | Applicable Device(s)                        | 2 |

| 3 | Referenced Documents                        |   |

| 4 | Acronyms                                    | 2 |

| 5 | Background Information                      | 2 |

| 6 | Example of Notional Design Implementation   | 2 |

|   | 6.1 LEON 3FT UT700 Microprocessor Interface | 3 |

|   | 6.1.1 Address, Data and Control             |   |

|   | 6.1.2 GPIO                                  |   |

|   |                                             |   |

|   | 6.1.2.1 GPIO[3]                             | 4 |

|   |                                             | 4 |

|   | 6.1.2.2 GPIO[4]                             | 4 |

|   | 6.1.2.3 GPIO[5]                             | 4 |

|   |                                             |   |

|   | 6.1.2.4 GPIO[6]                             | 4 |

|   | 613 UT700 Reset                             | 7 |

|   |                                             |   |

|   | 6.2 NOR Flash Interface                     |   |

|   | 6.2.1 Address Bus                           |   |

|   | 6.2.2 Data Bus                              |   |

|   | 6.2.3 Control Signals                       |   |

|   | 6.2.4 Write Protect (WP#)                   |   |

|   | 6.2.5 RESET#                                |   |

|   | 6.2.6 10k ohm Vcc Pulldown                  |   |

| 7 | Board Layout Considerations                 | 5 |

| 8 | Additional Notional Design Notes            |   |

| 9 | Conclusion                                  | 5 |

### **Table of Figures**

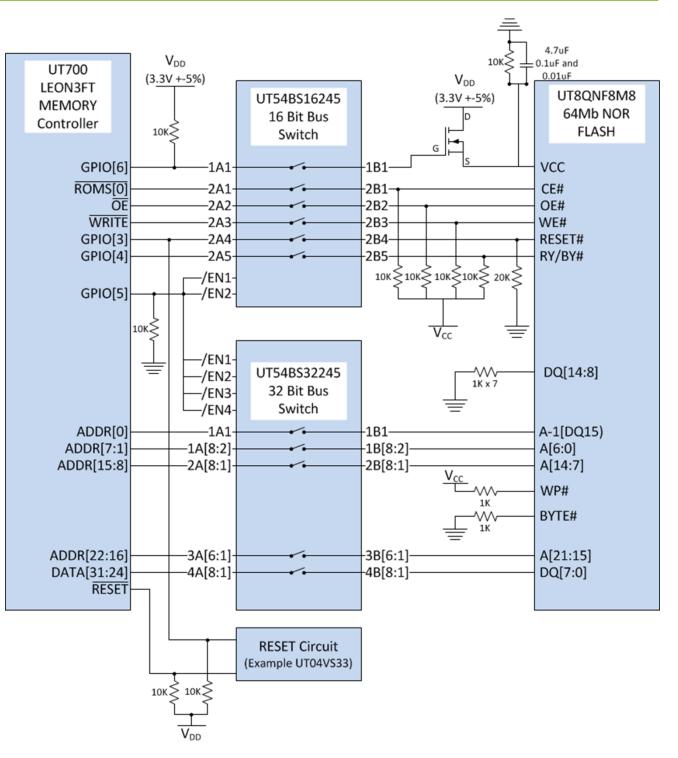

| Figure 1 50 krad(Si) TID Example Design |

|-----------------------------------------|

|-----------------------------------------|

# 1.0 Scope

This document outlines a design example for achieving 50 krad(Si) TID implementation of the Cobham Semiconductor Solutions UT8QNF8M8 64Mb NOR Flash memory device. The approach implements Cobham Semiconductor Solutions Bus Switches, that when disabled isolate the power and I/O signals to and from the NOR Flash.

# 2.0 Applicable Device(s)

UT8QNF8M8 64Mb NOR Flash https://cobhamaes.com/IsoveraURL/datasheets/UT8QNF8M8.pdf

# 3.0 Referenced Documents

UT54BS16245 16 bit Bus Switch https://cobhamaes.com/IsoveraURL/datasheets/UT54BS16245.pdf

UT54BS32245 32 bit Bus Switch https://cobhamaes.com/IsoveraURL/datasheets/UT54BS32245.pdf

UT04VS33P 4 channel Voltage Supervisor https://cobhamaes.com/IsoveraURL/datasheets/vSupUT04VS33P.pdf

UT700 LEON 3FT Processor https://cobhamaes.com/IsoveraURL/datasheets/leon/UT700LEON3FTDatasheet.pdf

Previously released Application Note (NOR Flash/Bus Switch Design Note) https://cobhamaes.com/IsoveraURL/appnotes/DesignNote Bus Switch NOR Flash.pdf

# 4.0 Acronyms

- TID Total Ionizing Dose

- GPIO General Purpose Input Output

# 5.0 Background Information

The UT8QNF8M8 NOR Flash TID performance is increased to 50 krad(Si) if the device is powered down during 90% of its design life. In order to prevent the UT8QNF8M8 device from being powered through the I/O signals, the entire device must be isolated not only from V<sub>DD</sub> but the I/O signals as well when it is not being accessed. One good way to implement this functionality is to use Bus Switches that when disabled, isolates power, as well as the paths for the I/O to and from the device.

# 6.0 Example of Notional Design Implementation

The example shown in Figure 1 implements a UT700 microprocessor interfacing to the NOR Flash using two Bus Switches. The additional device Cobham Semiconductor Voltage Supervisor, the UT04VS33, is an example of what is required to handle the power on reset condition.

# 6.1 LEON 3FT UT700 Microprocessor Interface

The UT700 requires all of the signals shown in Figure 1 to access the NOR Flash connected to the appropriate Bus Switches. For the NOR Flash isolation example, additional signals in the form of GPIO are required to control when the processor requires access to the NOR Flash and when it enables the isolation feature.

## 6.1.1 Address, Data and Control

Connect the Address, Data and control signals from the UT700 Microprocessor are connected to the appropriate signals on the Bus Switch device identified in the drawing Figure 1.

## 6.1.2 GPIO

There are three GPIO signals required to implement the NOR Flash Isolation example design. Two of them are required for the isolation and the third is simply for interfacing to the NOR Flash device itself. Note, the pulldown 10K resistor is required for power up and enables the NOR Flash to be accessible by the UT700 Microprocessor after power is stable. In this example the NOR Flash is the boot ROM for the UT700.

# 6.1.2.1 GPIO[3]

The GPIO[3] signal manages the RESET# signal on the NOR Flash during accesses that do not involve power up. It gives users the ability to control when the UT700 resets the NOR Flash. For the power up reset condition, the Voltage Supervisor holds the RESET# low for the programmed duration and once that time has been reached, the 10K resistor will pull RESET# high. User's may then program GPIO[3] to toggle whenever they wish to reset the NOR. Note that the UT700 defaults all GPIO to inputs on power up or reset.

The timing of the resets from the Voltage Supervisor must be set such that the NOR Flash comes out of reset first and the reset to the UT700 is release some time after that. The timing must meet the specifications for both the UT700 and the NOR Flash.

## 6.1.2.2 GPIO[4]

The GPIO[4] signal is used to monitor the RY/BY# signal. The active low signal indicates when the NOR Flash is busy servicing a transaction.

## 6.1.2.3 GPIO[5]

The GPIO[5] signal is used to control when to enable or disable the isolation feature of the example design. All /EN signals on the Bus Switches are active low. The 10k ohm pulldown resistor ensures the Bus Switch has all of the signals and  $V_{CC}$  enabled during power up. Note again that all GPIO signals on the UT700 are set as inputs during power up or reset.

## 6.1.2.4 GPIO[6]

The GPIO[5] signal is implemented to turn on the power FET which in turn controls the power on the NOR Flash. Notice the 10k pulldown which drives  $V_{CC}$  low when the FET is turned off.

## 6.1.3 UT700 Reset

The RESET signal into the UT700 is controlled by the Voltage Supervisor. The UT700 must be reset on power up and as previously stated, the UT700 must come out of reset last on the board. Additional reset circuitry may be desired by individual users and are UT700 user implementation specific.

## 6.2 NOR Flash Interface

The NOR Flash requires some specific design setup in order for it to properly function when powered through the Bus Switch.

### 6.2.1 Address Bus

Addresses are connected directly from the Bus Switch to the address bus on the NOR Flash as shown in Figure 1.

### 6.2.2 Data Bus

The NOR Flash is set in 8 bit mode by connecting the BYTE# pin to ground using a 1k ohm pulldown resistor. This places the upper data bits (DQ[14:8]) in a tristate mode. The tri-stated DQ signals are also pulled low using 1k pulldown resistors. The other data bits are connected directly to the appropriate Bus Switch.

### 6.2.3 Control Signals

All control signals are pulled high using 10k ohm resistors. The result is unwanted accesses during power up of the device are disabled.

### 6.2.4 Write Protect (WP#)

For this example the write protect bit (WP#) is tied high using a 1K resistor disabling write protect. For designers that want to control this signal, one more Bus Switch channel is needed along with an additional GPIO on the UT700.

#### 6.2.5 RESET#

The RESET# signal is handled by GPIO[3] or the voltage supervisor during the power on condition.

#### 6.2.6 10k ohm Vcc Pulldown

The pulldown resistor on the  $V_{CC}$  supply of the NOR Flash is used to bleed off voltage on  $V_{CC}$  when the device is powered down.

### 7.0 Board Layout Considerations

The layout of the NOR Flash must include a separate plane for the  $V_{CC}$  power rail. Since the NOR Flash will be powered down during much of the mission life of the system, no other devices should be getting power from that plane.

### 8.0 Additional Notional Design Notes

It is always recommended to use series termination for the Address and Data lines as well as Control Signals from the UT700 to the NOR Flash. Users may also wish to have the data bus pulled high or low so that when data from memory interfaces is not being driven, the data bus is not floating.

Also please refer to a prior one-page design note referred to in Section 3, which is less detailed than this subject white paper, and uses sever parallel bus switch channels to supply power to the NOR Flash as opposed to the PowerFET reference in this paper.

Please note that this white paper and the prior design note are only recommended approaches that should User's chose to implement, that all implementations for broader system impact should be reviewed and accessed.

#### 9.0 Conclusion

The UT8QNF8M8 NOR Flash offers excellent non-volatile memory density vs. footprint size for space flight applications. For designers requiring a non-volatile solution with 50 krad (Si) TID, the use of Bus Switches with the NOR Flash is a reasonable approach with limited impact on overall board real estate.

# **REVISION HISTORY**

| Date       | Rev. # | Change Description |  |  |  |

|------------|--------|--------------------|--|--|--|

| 08/26/2016 | -      | Initial Release    |  |  |  |

|            |        |                    |  |  |  |

|            |        |                    |  |  |  |

|            |        |                    |  |  |  |

|            |        |                    |  |  |  |

|            |        |                    |  |  |  |

|            |        |                    |  |  |  |

|            | Date   | Date Rev. #        |  |  |  |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.