# FRONTGRADE

# **DATASHEET UT8MR8M8**

64Megabit Non-Volatile MRAM

2/1/2023

Version #: 1.0.0

#### **Features**

- Single 3.3-V power supply

- Fast 50ns read/write access time

- · Functionally compatible with traditional asynchronous SRAMs

- · Equal address and chip-enable access times

- HiRel temperature range (-40°C to +105°C)

- · Automatic data protection with low-voltage inhibit circuitry to prevent writes on power loss

- · CMOS and TTL compatible

- Data non-volatile for > 20 years (-40°C to+105°C)

- Read/write endurance: Unlimited for 20 years (-40°C to+105°C)

- 64-pin ceramic flatpack package (21.99 grams)

- Operational environment:

- Total dose: 1Mrad(Si)

- SEL Immune: 112 MeV-cm<sup>2</sup>/mg @125°C

- SEU Immune: Memory Cell 112 MeV-cm<sup>2</sup>/mg @25°C

- Standard Microelectronics Drawing (SMD) 5962-13207

- QML Q, Q+, and V

### Introduction

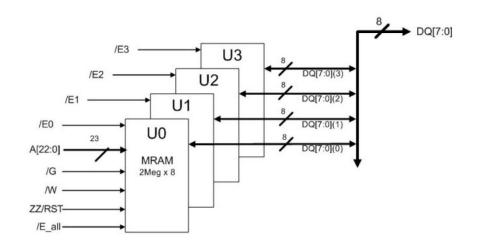

The Frontgrade 64Megabit Non-Volatile magnetoresistive random access memory (MRAM) is a high-performance memory multichip module (MCM) compatible with traditional asynchronous SRAM operations, organized as either four 2M words by 8 bits or one 8M words by 8 bits.

The MRAM is equipped with five chip enables (/En), a single write enable (/W), and a single output enable (/G) pins, allowing for significant system design flexibility without bus contention. Data is non-volatile for > 20 years at temperature and data is automatically protected against power loss by a low voltage write inhibit.

The 64Mb MRAM is designed specifically for operation in HiREL environments. As shown in Table 4, the magneto-resistive bit cells are immune to Single Event Effects (SEE). To guard against transient effects, an Error Correction Code (ECC) is included within the device. ECC check bits are generated and stored within the MRAM array during writes. The MBE (multiple-bit-error) pin identifies that ECC logic has detected two bit errors during the current read cycle.

Figure 1: UT8MR8M8 MRAM Block Diagram

## **Pin Names**

#### Table 1: 8M x 8 Pin Functions

| Signal Name          | Function                                         |

|----------------------|--------------------------------------------------|

| A[22:0]              | Address Input                                    |

| /E[3:0] <sup>1</sup> | Chip Enable                                      |

| /E_AII               | Chip Enable All                                  |

| /W                   | Write Enable                                     |

| /G                   | Output Enable                                    |

| DQ[7:0]              | Data I/O                                         |

| $V_{DD}$             | Power Supply                                     |

| V <sub>SS</sub>      | Ground                                           |

| ZZ/RST               | Deep Power Down/Reset (Internal pull down)       |

| MBE <sup>2</sup>     | Multi-Bit Error Flag                             |

| NUO                  | Not used output Do not connect Driven internally |

- 1. Only one /E[3:0] pin may be active at any time.

- 2. MBE pin is not functionally tested for prototypes.

| VSS——1                                                                                      | 64 —VDD              |

|---------------------------------------------------------------------------------------------|----------------------|

|                                                                                             | 63 — VSS             |

| $\begin{array}{c} \text{VDD} \longrightarrow 2 \\ \text{VSS} \longrightarrow 3 \end{array}$ | 62VSS                |

| VSS—4                                                                                       | 61 —-VSS             |

| /E0——5                                                                                      | 60 ——/E3             |

| A4——6                                                                                       | 59 ——A20             |

| A3—7                                                                                        | 58 ——A15             |

| A2——8                                                                                       | 57 ——A16             |

| A1——9                                                                                       | 56 ——A17             |

| A0—— 10                                                                                     | 55 ——A18             |

| A19—— 11                                                                                    | 54 — VSS             |

| ZZ/RST—12                                                                                   | 53 —/G               |

| NUO—— 13                                                                                    | 52 — VSS             |

| DQ4——14                                                                                     | 51 — DQ3             |

| DQ5——15                                                                                     | 50 ——DQ2<br>49 ——VSS |

| VDD———————————————————————————————————                                                      | .,                   |

|                                                                                             | 48 ——VDD<br>47 ——DQ1 |

| DQ6————————————————————————————————————                                                     | 46 DQ0               |

| $/E1 \longrightarrow 20$                                                                    | 45 ——/E2             |

| $/E\_All$ $20$                                                                              | 44 — VSS             |

| $\overline{A21}$ $\overline{A21}$ $\overline{22}$                                           | 43 ——MBE             |

| A22 $23$                                                                                    | 42 —/W               |

| $\stackrel{\sim}{A9}$ $\stackrel{\sim}{\longrightarrow}$ $\stackrel{\sim}{24}$              | 41 ——A10             |

| A8—— 25                                                                                     | 40 ——A11             |

| A7—— 26                                                                                     | 39 ——A12             |

| A6—— 27                                                                                     | 38 ——A13             |

| A5—— 28                                                                                     | 37 ——A14             |

| VSS—— 29                                                                                    | 36VSS                |

| VSS——30                                                                                     | 35 ——VSS             |

| VSS——31                                                                                     | 34 — VDD             |

| VDD——32                                                                                     | 33 ——VSS             |

|                                                                                             |                      |

Figure 2: 40ns MRAM Pinout (64)

# **Device Operation**

The UT8MR8M8 has control inputs called Chip Enable (E[3:0]), Chip Enable All (/E\_ALL), Write Enable (/W), Output Enable (/G), and sleep/reset mode (ZZ/RST); 23 address inputs, A[22:0]; eight bidirectional data lines, DQ[7:0]; and a Multi-bit Error Flag (MBE). /E[3:0] controls device selection, active, and standby modes. Asserting /E[3:0] enables the device, causes IDD to rise to its active value, and decodes the 21 address inputs, A[20:0], to select one of 16,777,216 words in the memory. Note: Only one Chip Enable may be active at any time. Asserting / E\_ALL allows the device to be addressed as a single, 64Mb memory using address bits A21 and A22 to decode and select 1 of 4 MRAM die. /W controls read and write operation. During a read cycle, /G must be asserted to enable the outputs. ZZ/RST controls the sleep/reset mode operation and provides device reset capability. Enabling sleep/reset mode causes all other inputs to be don't cares. ZZ/RST places all die into internal low power even while system power is still applied to V<sub>DD</sub>. The MBE pin is an open drain output pin which allows for wired-OR of multiple MBE when using multiple MRAMs. The MBE pin requires an external pull up to reach the high inactive state. See MRAM FAQ to determine the resistor value. After MBE initialization and only during data output valid time, an MBE low indicates that a two bit error exists for the read cycle.

**Table 2: Chip Enable Functions Table**

| /E_ALL | /E_0 | /E_1 | /E_2 | /E_3 | A22 | A21 | Comment            |

|--------|------|------|------|------|-----|-----|--------------------|

| 0      | 1    | 1    | 1    | 1    | 0   | 0   | MRAM Die 0 Enabled |

| 0      | 1    | 1    | 1    | 1    | 0   | 1   | MRAM Die 1 Enabled |

| 0      | 1    | 1    | 1    | 1    | 1   | 0   | MRAM Die 3 Enabled |

| 0      | 1    | 1    | 1    | 1    | 1   | 1   | MRAM Die 2 Enabled |

| 1      | 0    | 1    | 1    | 1    | Х   | х   | MRAM Die 0 Enabled |

| 1      | 1    | 0    | 1    | 1    | х   | х   | MRAM Die 1 Enabled |

| 1      | 1    | 1    | 0    | 1    | х   | х   | MRAM Die 2 Enabled |

| 1      | 1    | 1    | 1    | 0    | х   | х   | MRAM Die 3 Enabled |

#### Note:

1. Only one /E[3:0] pin may be active at any time.

#### **Table 3: Device Operation Truth Table**

| ZZ/ RST | /E[3:0]* | /G | /W | Mode                      | V <sub>DD</sub> Current | DQ[7:0]          |

|---------|----------|----|----|---------------------------|-------------------------|------------------|

| н       | x        | x  | x  | Deep Sleep/ Reset<br>Mode | Q <sub>IZZ</sub>        | HI-Z             |

| L       | Н        | х  | х  | Not Selected              | Q <sub>IDD</sub>        | HI-Z             |

| L       | L        | Н  | Н  | Output Disabled           | I <sub>DDR</sub>        | HI-Z             |

| L       | L        | L  | Н  | Byte Read                 | I <sub>DDR</sub>        | D <sub>OUT</sub> |

| L       | L        | х  | L  | Byte Write                | I <sub>DDW</sub>        | D <sub>IN</sub>  |

#### Note:

1. Only one /E[3:0] pin may be active at any time.

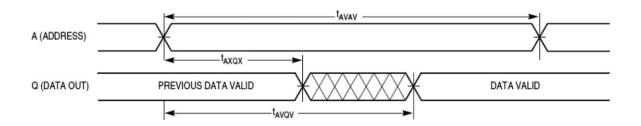

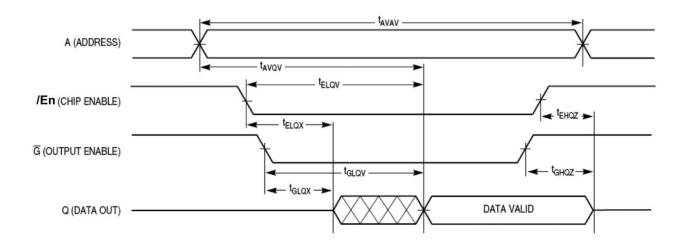

# **Read Cycle**

A combination of /W greater than  $V_{IH}$  (min) and a single /En less than  $V_{IL}$  (max) defines a read cycle. Read access time is measured from the latter of chip enable, output enable, or valid address to valid data output.

MRAM Read Cycle 1, the Address Access in Figure 6a, is initiated by a change in address inputs after a single /En is asserted, /G asserted and /W deasserted. Valid data appears on data outputs DQ[7:0] after the specified  $t_{AVQV}$  is satisfied. Outputs remain active throughout the entire cycle. As long as a single chip enable and output enable are active, the address inputs may change at a rate equal to the minimum read cycle time ( $t_{AVAV}$ ).

MRAM Read Cycle 2, the Chip Enable-controlled Access in Figure 6b, is initiated by a single /En going active while

/G remains asserted, /W remains deasserted, and the addresses remain stable for the entire cycle. After the specified tELQV is satisfied, the eight-bit word addressed by A[20:0] is accessed and appears at the data outputs DQ[7:0].

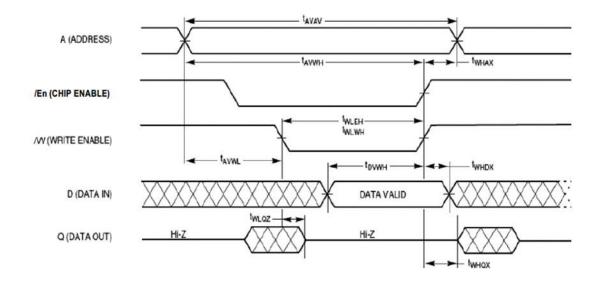

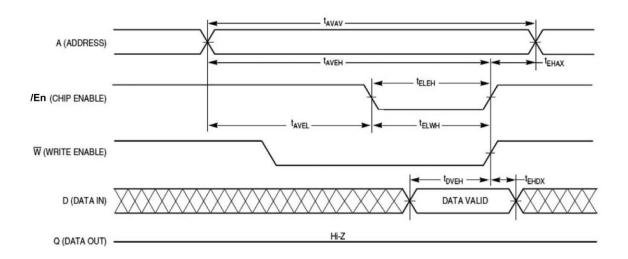

# **Write Cycle**

A combination of /W and a single /En less than  $V_{IL}(max)$  defines a write cycle. The state of /G is a "don't care" for a write cycle. The outputs are placed in the high-impedance state when either /G is greater than  $V_{IH}(min)$ , or when /W is less than  $V_{IL}(max)$ . Write Cycle 1, the Write Enable-controlled Access in Figure 7a, is defined by a write terminated by /W going high, with a single /En still active. The write pulse width is defined by tWLWH when the write is initiated by /W, and by tETWH when the write is initiated by a single /En. Unless the outputs have been previously placed in the high-impedance state by /G, the user must wait tWLQZ before applying data to the nine bidirectional pins DQ[7:0] to avoid bus contention.

Write Cycle 2, the Chip Enable-controlled Access in Figure 7b, is defined by a write terminated by a single /En going inactive. The write pulse width is defined by  $t_{WLEH}$  when the write is initiated by /W, and by  $t_{ELEH}$  when the write is initiated by a single /En going active. For the /W initiated write, unless the outputs have been previously placed in the high-impedance state by /G, the user must wait tWLQZ before applying data to the eight bidirectional pins DQ[7:0] to avoid bus contention.

# **Operational Environment**

The UT8MR8M8 MRAM incorporates special design and layout features which allows operation in harsh environments.

**Table 4: Operational Environment Design Specifications**

| Parameter                             | Limit | Units                   |

|---------------------------------------|-------|-------------------------|

| TID                                   | 1     | Mrad(Si)                |

| SEL Immunity <sup>1</sup>             | ≤ 112 | MeV-cm <sup>2</sup> /mg |

| SEU Memory Cell Immunity <sup>2</sup> | ≤ 112 | MeV-cm <sup>2</sup> /mg |

#### Notes:

- 1. SEL test performance at  $V_{DD}$  = 3.6V and temperature= 125°C.

- 2. SEU test performance at  $V_{DD}$  = 3.0V and unpowered at room temperature.

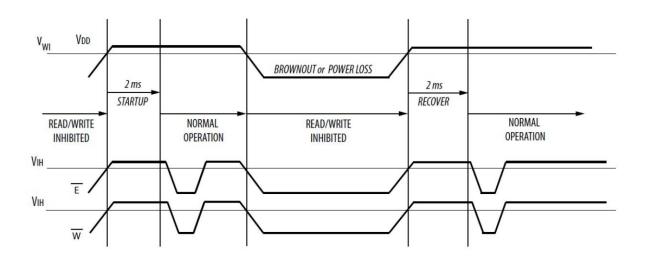

# **Power Up and Power Down Sequencing**

The MRAM is protected from write operations whenever  $V_{DD}$  is less than VWI. As soon as  $V_{DD}$  exceeds  $V_{DD}$ (min), there is a startup time of 2 ms before read or write operations can start. This time allows memory power supplies to stabilize. The /En and /W control signals should track  $V_{DD}$  on power up to  $V_{DD}$ -0.2 V or  $V_{IH}$  (whichever is lower) and remain high for the startup time. In most systems, this means that these signals should be pulled up with a resistor so the signal remains high if the driving signal is Hi-Z during power up. Any logic that drives /En and /W should hold the signals high with a power-on reset signal for longer than the startup time. During power loss or brownout where  $V_{DD}$  goes below VWI, writes are protected and a startup time must be observed when power returns above  $V_{DD}$ (min).

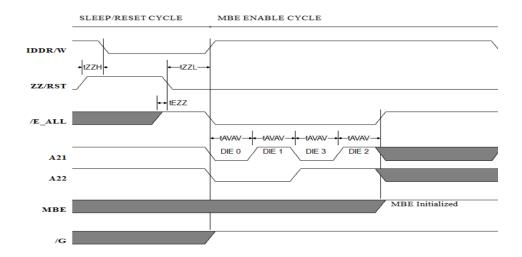

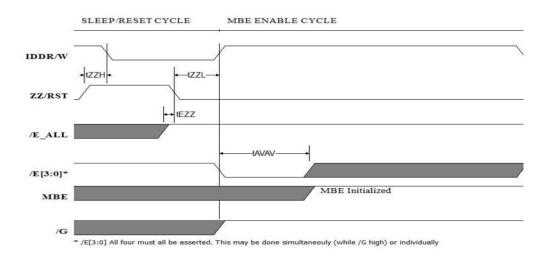

The MRAM supports sleep/reset mode operation using the ZZ/RST control pin. To enter sleep mode/reset, ZZ/RST must be pulled high. The device will enter sleep/reset mode within 40ns. In order to exit sleep/reset mode, /En and/W must be high before ZZ/RST is pulled low. As soon as ZZ/RST is driven low, the user must allow 100us before performing any other operation in order for the device to properly initialize. Frontgrade recommends designing a system level method to toggle the ZZ/RST pin in order to reset the MRAM device.

Figure 3: UT8MR8M8 Power Up and Power Down Sequencing Diagram

# **MBE Output Initialization**

The 64M MRAM is a Multi-Chip Module (MCM) made up of four 16M MRAM die. Each die has its own open drain MBE output. These four MBE outputs are wired-OR connected within the UT8MR8M8 package to produce a single MCM MBE output. This MBE output is not defined after power up or after coming out of sleep/reset until the MRAM is enabled for the first time. In order to initialize the MBE pin after power up or reset, all die within the package must be accessed. This can be accomplished by toggling the four separate enable pins (/En[0:3]), or by toggling through A[22:21] with /En\_ALL held low. After initialization, MBE is a device output with the same valid time as the data outputs. Spurious MBE low pulses can occur during the initiation of any read cycle. MBE is only valid if low after the minimum read access time has been satisfied (tavav or tELQV). It is suggested that users poll the MBE pin at the same time the data is being polled (see Figures 4 and 5).

Figure 4: Post Reset MBE Initialization using A21, A22, & /E\_AII

Figure 5: Post Reset MBE Initialization using enable pins /E[3:0]

# **Absolute Maximum Ratings<sup>1</sup>**

### (Referenced to V<sub>SS</sub>)

The device contains protection against magnetic fields. Precautions should be taken to avoid device exposure of any magnetic field intensity greater than specified.

| Symbol             | Parameter                                                | Value                        | Unit |

|--------------------|----------------------------------------------------------|------------------------------|------|

| V <sub>DD</sub>    | Supply Voltage <sup>2</sup>                              | -0.5 to 4.3                  | V    |

| V <sub>IN</sub>    | Voltage on any pin <sup>2</sup>                          | -0.5 to V <sub>DD</sub> +0.5 | V    |

| I <sub>IO</sub>    | DC I/O current per pin @ T <sub>J</sub> = 125° for 20yrs | ± 20                         | mA   |

| P <sub>D</sub>     | Package power dissipation <sup>3</sup>                   | 9                            | W    |

| T <sub>J</sub>     | Maximum junction temperature                             | +150                         | °C   |

| $\Theta_{JC}$      | Thermal resistance junction to case - Single Die         | 5                            | °C/W |

| T <sub>STG</sub>   | Storage temperature                                      | -65 to +125                  | °C   |

| E <sub>SDHBM</sub> | ESD                                                      | >2000                        | V    |

| H max_write        | Maximum magnetic field during write                      | 8000                         | A/m  |

| H max_read         | Maximum magnetic field during read or standby            | 8000                         | A/m  |

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. Exposure to excessive voltages or magnetic fields could affect device reliability.

- 2. All voltages are referenced to V<sub>SS</sub>.

- 3. Per MIL-STD-883, Method 1012, Section 3.4.1  $\frac{PD=\left(T_{i}(max)-T_{c}(max)\right)}{\Theta_{ic}}$

# **Recommended Operating Conditions**

| Symbol          | Parameter                  | Limits                        |

|-----------------|----------------------------|-------------------------------|

| T <sub>C</sub>  | Operating case temperature | -40°C to +105°C               |

| $V_{DD}$        | Operating supply voltage   | 3.0V to 3.6V                  |

| V <sub>WI</sub> | Write inhibit voltage      | 2.5V to 3.0V <sup>1, 2</sup>  |

| V <sub>IH</sub> | Input high voltage         | 2.0V to V <sub>DD</sub> +0.3V |

| V <sub>IL</sub> | Input low voltage          | V <sub>SS</sub> -0.3V to 0.8V |

#### Notes:

- 1. After power up or if  $V_{DD}$  falls below VWI, a waiting period of 2 ms must be observed, and /En and /W must remain high for 2 ms. Memory is designed to prevent writing for all input pin conditions if  $V_{DD}$  falls below minimum  $V_{WI}$ .

- 2. The MRAM is guaranteed to activate write inhibit below 2.5V, but may enter write inhibit mode anywhere within this voltage range. It is guaranteed to exit write inhibit mode once recommended operating voltage range is reached.

# DC Electrical Characteristics (Pre and Post-Radiation)\*

$V_{DD}$  = 3.0V to 3.6V; Unless otherwise noted, Tc is per the temperature ordered <sup>5, 6</sup>

| Symbol                          | Parameter                          | Condition                                                                     | Min                  | Max                  | Unit |

|---------------------------------|------------------------------------|-------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>IH</sub>                 | High-level input voltage           |                                                                               | 2.0                  |                      | V    |

| V <sub>IL</sub>                 | Low-level input voltage            |                                                                               |                      | 0.8                  | v    |

| V <sub>OL1</sub>                | Low-level output voltage           | I <sub>OL</sub> = 4mA, V <sub>DD</sub> =V <sub>DD</sub> (min)                 |                      | 0.4                  | v    |

| V <sub>OL2</sub>                | Low-level output voltage           | I <sub>OL</sub> =+100μA, V <sub>DD</sub> =V <sub>DD</sub> (min)               |                      | V <sub>SS</sub> +0.2 | v    |

| V <sub>OH1</sub>                | High-level output voltage          | $I_{OH} = -4mA$ , $V_{DD} = V_{DD}$ (min)                                     | 2.4                  |                      | v    |

| V <sub>OH2</sub>                | High-level output voltage          | $I_{OH}$ = -100 $\mu$ A, $V_{DD}$ = $V_{DD}$ (min)                            | V <sub>DD</sub> -0.2 |                      | v    |

| C <sub>IN</sub> <sup>1</sup>    | Input capacitance                  | ∫ = 1MHz @ 0V                                                                 |                      | 50                   | pF   |

| C <sub>IO</sub> <sup>1</sup>    | Bidirectional I/O capacitance      | ∫ = 1MHz @ 0V                                                                 |                      | 60                   | pF   |

| I <sub>IN</sub>                 | Input leakage current              | $V_{IN} = V_{DD}$ and $V_{SS}$                                                | -1                   | +1                   | μΑ   |

| I <sub>INZZ</sub>               | Input leakage current ZZ/RST       | $V_{IN} = V_{DD}$ and $V_{SS}$                                                | -0.25                | 0.25                 | mA   |

| l <sub>OZ</sub>                 | Three-state output leakage current | $V_O = V_{DD}$ and $V_{SS}$ , $V_{DD} = V_{DD}$ (max) $/G = V_{DD}$ (max)     | -1                   | +1                   | μΑ   |

| I <sub>OS</sub> <sup>2, 3</sup> | Short-circuit output current       | $V_{DD} = V_{DD}$ (max), $VO = V_{DD}$ $V_{DD} = V_{DD}$ (max), $VO = V_{SS}$ | -100                 | +100                 | mA   |

| I <sub>DDR</sub>                | Active read supply current         | Read mode $\int = MAX (IOUT = 0mA; V_{DD} = max)$                             |                      | 140                  | mA   |

| I <sub>DDW</sub>                | Active write supply current        | Write mode $\int = 10 \text{ MHz (V}_{DD} = \text{max)}$                      |                      | 140                  | mA   |

| Symbol                        | Parameter                                | Condition                                                                                           |                | Min | Max | Unit |

|-------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|-----|-----|------|

| $Q_{IDD}$                     | Quiescent supply current                 | CMOS leakage current (/E = V <sub>DD</sub> ; all other                                              | -40°C<br>+25°C |     | 30  | mA   |

|                               |                                          | inputs equal $V_{SS}$ or $V_{DD}$ ; $V_{DD} = max$ )                                                | +105°C         |     | 35  | mA   |

| Q <sub>IZZ</sub> <sup>4</sup> | Deep power down and reset supply current | CMOS leakage current (/E = $V_{DD}$ ; all other inputs equal $V_{SS}$ or $V_{DD}$ ; $V_{DD}$ = max) |                |     | 1   | mA   |

Notes:\*For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. Measured only for initial qualification and after process or design changes that could affect input/output capacitance.

- 2. Supplied as a design limit but not guaranteed or tested.

- 3. Not more than one output may be shorted at a time for maximum duration of one second.

- 4. Allow 100µs to exit sleep/reset mode before performing any other operation.

- 5. MBE pin is an open drain, tested functionally.

- 6. Testing performed with Error Correction Code enabled (ECC-ON), customer use case always utilizes ECC-ON.

# AC Characteristics Read Cycle<sup>1</sup> (Pre and Post-Radiation)\*

### $V_{DD} = V_{DD}$ (min); Unless otherwise noted, Tc is per the temperature ordered <sup>5, 6</sup>

| Symbol                         | Parameter                          | Min | Max | Unit |

|--------------------------------|------------------------------------|-----|-----|------|

| t <sub>AVAV</sub>              | Read cycle time                    | 50  |     | ns   |

| t <sub>AVQV</sub>              | Address access time                |     | 50  | ns   |

| t <sub>ELQV</sub> <sup>2</sup> | Enable access time                 |     | 50  | ns   |

| t <sub>GLQV</sub> <sup>3</sup> | Output enable access time          |     | 25  | ns   |

| t <sub>AXQX</sub>              | Output hold from address change    | 3   |     | ns   |

| t <sub>ELQX</sub> <sup>4</sup> | Enable low to output active        | 3   |     | ns   |

| t <sub>GLQX</sub> <sup>4</sup> | Output enable low to output active | 0   |     | ns   |

| t <sub>EHQZ</sub> <sup>4</sup> | Enable high to output Hi-Z         | 0   | 15  | ns   |

| t <sub>GHQZ</sub> <sup>4</sup> | Output enable high to output Hi-Z  | 0   | 15  | ns   |

Notes:\*For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. /W is high for read cycle. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles.

- 2. Address valid before or at the same time /En goes low.

- 3.  $t_{GLQV}$  output enable valid time unless  $t_{AVAV}$  or  $t_{AVQV}$  have not been satisfied.

- 4. Transition is measured at +/-400mV from the steady-state voltage.

- 5. MBE pin is an open drain, tested functionally.

- 6. Testing performed with Error Correction Code enabled (ECC-ON), customer use case always utilizes ECC-ON.

Figure 6a: MRAM Read Cycle 1

#### Note:

1. Devices is continuously selected (/En  $\leq$  V<sub>IL</sub>, G  $\leq$  V<sub>IL</sub>).

Figure 6b: MRAM Read Cycle 2

# AC Characteristics /W Controlled Write Cycle (Pre and Post-Radiation)\*

V<sub>DD</sub>= V<sub>DD</sub> (min); Unless otherwise noted, Tc is per the temperature ordered <sup>4,5</sup>

| Symbol                         | Parameter                               | Min | Max | Unit |

|--------------------------------|-----------------------------------------|-----|-----|------|

| t <sub>AVAV</sub> <sup>2</sup> | Write cycle time                        | 50  |     | ns   |

| t <sub>AVWL</sub>              | Address set-up time                     | 0   |     | ns   |

| t <sub>AVWH</sub>              | Address valid to end of write (/G high) | 28  |     | ns   |

| t <sub>AVWH</sub>              | Address valid to end of write (/G low)  | 28  |     | ns   |

| Symbol                              | Parameter                          | Min | Max | Unit |

|-------------------------------------|------------------------------------|-----|-----|------|

| t <sub>WLWH</sub> t <sub>WLEH</sub> | Write pulse width (/G high or low) | 28  |     | ns   |

| t <sub>DVWH</sub>                   | Data valid to end of write         | 10  |     | ns   |

| t <sub>WHDX</sub>                   | Data hold time                     | 0   |     | ns   |

| t <sub>WLQZ</sub> <sup>3</sup>      | Write low to data Hi-Z             | 0   | 15  | ns   |

| t <sub>WHQX</sub> <sup>3</sup>      | Write high to output active        | 3   |     | ns   |

| t <sub>WHAX</sub>                   | Write recovery time                | 16  |     | ns   |

Notes: \*For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. All write occurs during the overlap of /En low and /W low. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles. If /G goes low at the same time or after /W goes low, the output will remain in a high impedance state.

- 2. All write cycle timings are referenced from the last valid address to the first transition address.

- 3. Transition is measured +/-400mV from the steady-state voltage.

- 4. MBE pin is an open drain, tested functionally.

- 5. Testing performed with Error Correction Code enabled (ECC-ON), customer use case always utilizes ECC-ON.

Figure 7a: MRAM Write Cycle 1 (/W Controlled Access)

# AC Characteristics / En Controlled Write Cycle<sup>1</sup> (Pre and Post-Radiation)\*

V<sub>DD</sub>= V<sub>DD</sub> (min); Unless otherwise noted, Tc is per the temperature ordered <sup>5, 6</sup>

| Symbol                                                           | Parameter                               | Min | Max | Unit |

|------------------------------------------------------------------|-----------------------------------------|-----|-----|------|

| t <sub>AVAV</sub> <sup>2</sup>                                   | Write cycle time                        | 50  |     | ns   |

| t <sub>AVEL</sub>                                                | Address set-up time                     | 0   |     | ns   |

| t <sub>AVEH</sub>                                                | Address valid to end of write (/G high) | 28  |     | ns   |

| t <sub>AVEH</sub>                                                | Address valid to end of write (/G low)  | 28  |     | ns   |

| t <sub>eleh</sub>                                                | Enable to end of write (/G high)        | 28  |     | ns   |

| t <sub>eleh</sub> <sup>3</sup><br>t <sub>elwh</sub> <sup>3</sup> | Enable to end of write (/G low)         | 28  |     | ns   |

| t <sub>DVEH</sub>                                                | Data valid to end of write              | 10  |     | ns   |

| t <sub>EHDX</sub> <sup>4</sup>                                   | Data hold time                          | 0   |     | ns   |

| t <sub>EHAX</sub> <sup>4</sup>                                   | Write recovery time                     | 16  |     | ns   |

Notes:\*For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. All write occurs during the overlap of /En low and /W low. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles. If /G goes low at the same time or after /W goes low, the output will remain in a high impedance state.

- 2. All write cycle timings are referenced from the last valid address to the first transition address.

- 3. If /En goes low at the same time or after /W goes low, the output will remain in a high-impedance state. If /En goes high at the same time or before /W goes high, the output will remain in a high-impedance state.

- 4. Transition is measured +/-400mV from the steady-state voltage.

- 5. MBE pin is an open drain, tested functionally.

- 6. Testing performed with Error Correction Code enabled (ECC-ON), customer use case always utilizes ECC-ON.

Figure 7b: MRAM Write Cycle 2 (/En Controlled)

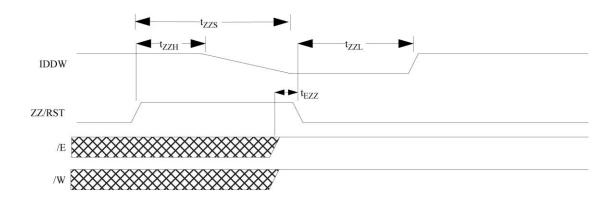

# AC Characteristics SLEEP/RESET Mode (Pre and Post-Radiation)\*

V<sub>DD</sub>= V<sub>DD</sub> (min); Unless otherwise noted, Tc is per the temperature ordered <sup>4,5</sup>

| Symbol                           | Parameter                        | MIN | MAX | Unit |

|----------------------------------|----------------------------------|-----|-----|------|

| t <sub>ZZL</sub> <sup>1, 3</sup> | Sleep/reset mode exit delay      |     | 100 | μs   |

| t <sub>ZZH</sub> <sup>2, 3</sup> | Sleep/reset mode access time     | 50  |     | ns   |

| t <sub>EZZ</sub> <sup>3</sup>    | Sleep/reset mode exit setup time | 0   |     | ns   |

| t <sub>ZZS</sub> <sup>3</sup>    | Sleep/reset mode settle time     |     | 200 | μς   |

Notes: For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. /En and /W must be high for the entire time when ZZ/RST is pulled low in order to exit sleep/reset mode.

- 2. ZZ/RST must be high for 40ns in order to enter sleep/reset mode.

- 3. Parameters are supplied as a design limit, but are not tested nor guaranteed.

- 4. MBE pin is an open drain, tested functionally.

- 5. Testing performed with Error Correction Code enabled (ECC-ON), customer use case always utilizes ECC-ON.

Figure 8: MRAM Sleep/Reset Mode Timing Diagram

Figure 9: AC Output Test Load or Equivalent

#### Note:

1. Measurement of data output occurs at the low to high or high to low transition mid-point, typically,  $V_{DD}/2$ .

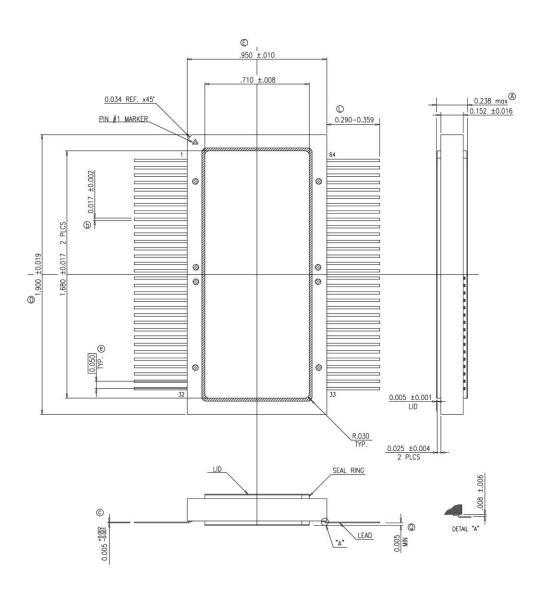

Figure 10: 64-Pin Ceramic Flatpack

- 1. Lid is connected to  $V_{SS}$

- 2. Units are in inches

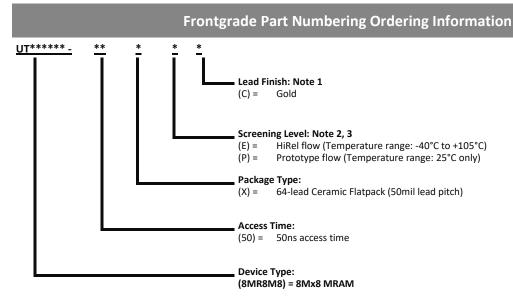

# **Ordering Information**

- 1. Lead finish is "C" (Gold) only.

- 2. Prototype flow per Frontgrade Colorado Springs Manufacturing Flows Document. Radiation neither tested nor guaranteed.

- 3. HiRel Temperature Range flow per Frontgrade Colorado Springs Manufacturing Flows Document. Radiation neither tested nor guaranteed.

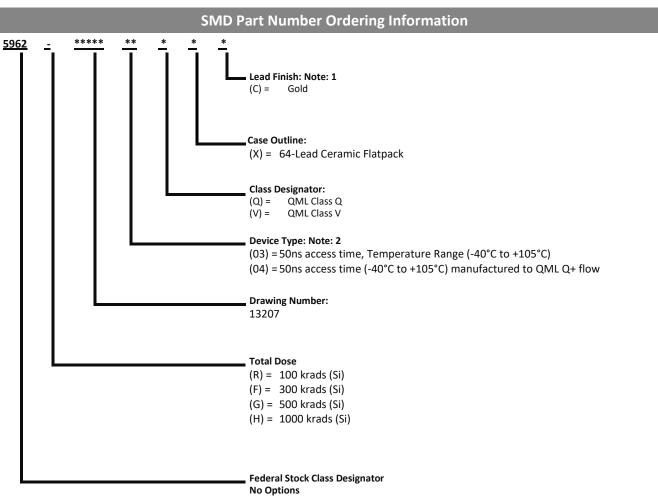

# **Ordering Information**

- 1. Lead finish is "C" (Gold) only.

- 2. Frontgrade Q+ flow, as defined in Section 4.2.2d of SMD, provides QML-Q product through the SMD that is manufactured with Frontgrade standard QML-V flow.

# **Revision History**

| Date             | Revision # | Author | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page #         |

|------------------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| January<br>2016  |            |        | Added new Frontgrade datasheet template, QML V Achieved, added ZZ/RST description of internal pull-down, updated maximum junction temperature to 150C, changed unit from uA to mA for the IINZZ specification, and added MBE Functionality verbiage and diagrams.                                                                                                                                                                                              | All            |

| November<br>2017 |            |        | Removed (T) Prototype flow (Temperature range: -40 to +105C) as an ordering option.                                                                                                                                                                                                                                                                                                                                                                            | 14             |

| July 2018        |            |        | Added package weight. Edited Device Operation paragraph. Edited MBE Pin Functionality and Sequencing paragraph. Edited Recommended Operating Conditions $V_{\text{IH}}$ and added note 2.                                                                                                                                                                                                                                                                      | 1,4,6,8        |

| Sept 2019        |            |        | Marked QML V from page 1 features list as pending. Replaced device type 01 and 02 with 03 and 04 and noted QML V option on page 16 "pending contact factory". Added note 3. to page 7 for tGLQV clarification. Previous note 3 is now 4.                                                                                                                                                                                                                       | 1,2,4,6,12     |

| Dec 2020         |            |        | Removed note from page 1 and page 15 that QML V pending, replaced the word aeroflex with Frontgrade in body of document. Changed PD from 4W to 9W in abs max table, also changed note 3 for abs max table to more common PD= Tjmax-Tcmax/theta JC, added notes that MBE is open drain and tested functionally along with ECC-ON always enabled to all DC and AC char tables. Correct figure 8a as it was distorted in previous datasheet.                      |                |

| Nov 2022         |            |        | Changed format to Frontgrade (all pages). Added (multiple-bit-error) definition after MBE, pg1. Removed yellow border figure 2, clarified MBE low statement under device operation, pg 2. Changed paragraph name MBE Pin Functionality and Sequencing to MBE Output Initialization, made several editorial clarifications in paragraph, corrected figure 5 changing MBE valid to MBE initialization, pg5. Corrected figure 6 MBE valid to initialization, pg6. | 1,2,5,6<br>MJL |

## **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                   |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.