# PRONTGRADE DATASHEET UT54BS16210

20-bit Bus Switch

8/19/2021 Version #: 2.0.5

## **Features**

- 3.3V operating power supply with typical  $11\Omega$  switch connection between ports

- 5.0V operating power supply with typical  $5\Omega$  switch connection between ports

- · Bidirectional operation

- Ultra-low power CMOS technology

- ESD Rating HBM: 2000V, Class 2

- · Signal Isolation: -60dB

- · Channel Bandwidth (3dB): 500MHz

- Standard Microcircuit Drawing (SMD):

- 5962-15245

- QML Q and V compliant part

- Package Options: 48-Lead Flatpack

# **Operational Environment**

• Temperature Range: -55°C to +125°C

• Total Dose: 300 krad(Si)

SEL Immune: ≤100 MeV-cm<sup>2</sup>/mg

# **Applications**

- · Memory Interface

- Bus Isolation

- Redundancy

- Supports Analog Applications

## Introduction

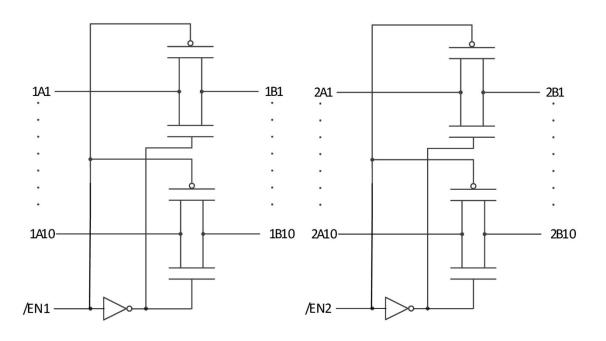

The UT54BS16210 provides 20 bits of high-speed CMOS-compatible bus switching. The low on-state resistance of the switch allows connections to be made with minimal propagation delay. The device is organized as a dual 10-bit bus switch with separate output-enable (/EN) inputs. It can be used as two 10-bit bus switches or as one 20-bit bus switch. When output enable (/EN) is low, the associated 10-bit bus switch is on and port A is connected to port B. When /EN is high, the switch is open and a high-impedance state exists between the two ports.

Figure 1: 20-bit Bus Switch Block Diagram

## **Pinlist**

TO = TTL Output

TTB = Three-State TTL Bidirectional

CI = CMOS Input

TUI = TTL Input (Internally Pulled High)

TI = TTL Input

TTO = Three-State TTL Output

DIO = Differential Input/Output

## **Table 1: Pinlist**

| Number                                                                         | Name            | Description                                    |

|--------------------------------------------------------------------------------|-----------------|------------------------------------------------|

| 2, 3, 4, 5, 6, 7, 9, 10, 11, 12, 13, 14, 16, 18, 19, 20, 21, 22, 23, 24        | nAn             | Port A Pins                                    |

| 25, 26, 27, 28, 29, 30, 31, 33, 34, 35, 36, 37, 38, 39, 40, 42, 43, 44, 45, 46 | nBn             | Port B pins                                    |

| 47, 48                                                                         | /ENn            | Active LOW enable pin                          |

| 8, 17, 32, 41                                                                  | V <sub>ss</sub> | Ground Pin                                     |

| 15                                                                             | V <sub>DD</sub> | Supply Pin, +3.3V -or- +5.0V                   |

| 1                                                                              | NC              | No Connect (electrically not connected to die) |

Version #: 2.0.5

# **Package Pinout Diagram**

| NC   | 1  |           | 48 | /1EN       |

|------|----|-----------|----|------------|

| 1A6  | 2  |           | 47 | /2EN       |

| 1A7  | 3  |           | 46 | 1B10       |

| 1A8  | 4  |           | 45 | 1B9        |

| 1A9  | 5  |           | 44 | 1B8        |

| 1A10 | 6  |           | 43 | 1B7        |

| 1A5  | 7  |           | 42 | 1B6        |

| VSS  | 8  |           | 41 | VSS        |

| 1A4  | 9  |           | 40 | 1B5        |

| 1A3  | 10 | U,        | 39 | 1B3        |

| 1A3  | 11 | Γ5.       | 38 |            |

| 1A2  | 12 | JT54BS162 | 37 | 1B3<br>1B2 |

| 2A1  | 13 | SI        | 36 | 1B2        |

| 2A2  | 14 | 62        | 35 | 2B1        |

| VDD  | 15 | 210       | 34 | 2B2        |

| 2A3  | 16 |           | 33 | 2B3        |

| VSS  | 17 |           | 32 | VSS        |

| 2A4  | 18 |           | 31 | 2B4        |

| 2A5  | 19 |           | 30 | 2B5        |

| 2A6  | 20 |           | 29 | 2B10       |

| 2A7  | 21 |           | 28 | 2B9        |

| 2A8  | 22 |           | 27 | 2B8        |

| 2A9  | 23 |           | 26 | 2B7        |

| 2A10 | 24 |           | 25 | 2B6        |

|      |    |           |    |            |

Version #: 2.0.5

# **Absolute Maximum Ratings**<sup>1, 2</sup>

## **Table 2: Absolute Maximum Ratings**

| Symbol             | Parameter                            | MIN  | MAX                  | Units |

|--------------------|--------------------------------------|------|----------------------|-------|

| V <sub>DD</sub>    | Positive Supply Voltage              | -0.5 | +7.2                 | V     |

| Vı                 | Input Voltage                        | -0.5 | V <sub>DD</sub> +0.3 | V     |

| I <sub>CCC</sub>   | DC Channel Current                   |      | 65                   | mA    |

| P <sub>D</sub>     | Max Power Dissipation <sup>3</sup>   |      | 1.6                  | w     |

| TJ                 | Junction Temperature                 |      | +150                 | °C    |

| ОЈС                | Thermal resistance, junction-to-case |      | 15                   | °C/W  |

| T <sub>STG</sub>   | Storage Temperature                  | -65  | +150                 | °C    |

| ESD <sub>HBM</sub> | ESD Protection <sup>4</sup>          |      | 2000                 | V     |

#### Notes:

- 1. Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification are not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2. All voltages referenced to  $V_{SS}$

- 3. Per MIL-STD-883, method 1012, section 3.4.1, PD= $(T_J(max)-T_C(max))/\theta JC)$

- 4. Per MIL-STD-883, method 3015, Table 3

# Operational Environment<sup>1</sup>

## **Table 3: Operational Environment**

| Symbol | Parameter                                  | Limit | Units                   |

|--------|--------------------------------------------|-------|-------------------------|

| TID    | Total Ionizing Dose <sup>2</sup>           | 300   | krad(Si)                |

| SEL    | Single Event Latchup Immunity <sup>3</sup> | ≤100  | MeV-cm <sup>2</sup> /mg |

- 1. For devices with procured with a total ionizing dose tolerance guarantee, post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to maximum TID level procured.

- 2. Per MIL-STD-883, method 1019, condition A

- 3. SEL is performed at  $V_{DD}$  = Max Voltage at 125°C

# **Recommended Operating Conditions<sup>1</sup>**

**Table 4: Recommended Operating Conditions**

| Symbol           | Parameter                | Conditions                                         | MIN        | MAX             | Units |

|------------------|--------------------------|----------------------------------------------------|------------|-----------------|-------|

| $V_{DD}$         | Positive Supply Voltage  |                                                    | 3.0 or 4.5 | 3.6 or 5.5      | V     |

| V <sub>IN</sub>  | Input Voltage on any pin |                                                    | 0.0        | V <sub>DD</sub> | V     |

| T <sub>C</sub>   | Case Temperature Range   |                                                    | -55        | +125            | °C    |

| t <sub>R</sub>   | Rise time, logic inputs  | Transition from V <sub>IL</sub> to V <sub>IH</sub> |            | 5               | ns    |

| t <sub>F</sub>   | Fall time, logic inputs  | Transition from VIH to VIL                         |            | 5               | ns    |

| I <sub>ccc</sub> | DC Channel Current       |                                                    |            | 60              | mA    |

#### Note:

1. All voltages referenced to V<sub>SS</sub>

## **Electrical Characteristics**<sup>1</sup>

$(V_{DD}=5.0V\pm0.5V, 3.3V\pm0.3V, -55^{\circ}C < T_{C} < +125^{\circ}C)$ ; Unless otherwise noted,  $T_{C}$  is per the temperature range ordered

**Table 5: DC Electrical Characteristics**

| Symbol                 | Parameter                                               | Conditions                                                                                                                              | MIN                  | MAX                  | Units  |

|------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--------|

| V <sub>IH</sub>        | High digital input voltage                              | V <sub>DD</sub> = 3.6, 5.5                                                                                                              | 0.7* V <sub>DD</sub> |                      | V      |

| V <sub>IL</sub>        | Low digital input voltage                               | V <sub>DD</sub> = 3.0, 4.5                                                                                                              |                      | 0.3* V <sub>DD</sub> | V      |

| I <sub>ID</sub>        | Leakage current digital                                 | V <sub>DD</sub> (max); V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub>                                                               | -1                   | 1                    | μΑ     |

| I <sub>IA</sub>        | Leakage current analog                                  | V <sub>DD</sub> (max); V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub>                                                               | -1                   | 1                    | μΑ     |

| I <sub>DD</sub>        | Active supply current                                   | V <sub>DD</sub> = 3.6, 5.5                                                                                                              |                      | 0.1                  | mA/MHz |

| I <sub>DDQ</sub>       | Quiescent Supply Current                                | V <sub>DD</sub> (max); I <sub>O</sub> =0mA; /EN=V <sub>DD</sub>                                                                         |                      | 15                   | μΑ     |

| Cı                     | Input Capacitance (/EN) <sup>2</sup>                    | VI=V <sub>DD</sub> or V <sub>SS</sub>                                                                                                   |                      | 26                   | pF     |

| C <sub>IO(OFF)</sub>   | Channel pin capacitance (channel disabled) <sup>2</sup> | $V_{DD}$ (max); $VO=V_{DD}$ or $V_{SS}$ ; $V_1=V_{DD}/2$ ; $/EN=V_{DD}$                                                                 |                      | 18                   | pF     |

|                        | Resistance through switch                               | V <sub>DD</sub> =4.5V, VI=V <sub>SS</sub> , /EN=0V, I <sub>O</sub> =30mA                                                                |                      | 10                   | Ω      |

| В                      |                                                         | V <sub>DD</sub> =4.5V, VI=V <sub>SS</sub> , /EN=0V, I <sub>O</sub> =15mA                                                                |                      | 10                   | Ω      |

| R <sub>ONL</sub>       | (channel input low) <sup>3</sup>                        | V <sub>DD</sub> =3.0V, VI=V <sub>SS</sub> , /EN=0V, I <sub>O</sub> =30mA                                                                |                      | 12                   | Ω      |

|                        |                                                         | V <sub>DD</sub> =3.0V, VI=V <sub>SS</sub> , /EN=0V, I <sub>O</sub> =15mA                                                                |                      | 12                   | Ω      |

|                        |                                                         | V <sub>DD</sub> =4.5V, VI=V <sub>DD</sub> , /EN=0V, I <sub>O</sub> =-30mA                                                               |                      | 10                   | Ω      |

| В                      | Resistance through switch                               | V <sub>DD</sub> =4.5V, VI=V <sub>DD</sub> , /EN=0V, I <sub>O</sub> =-15mA                                                               |                      | 10                   | Ω      |

| R <sub>ONH</sub>       | (channel input high) <sup>3</sup>                       | V <sub>DD</sub> =3.0V, VI=V <sub>DD</sub> , /EN=0V, I <sub>O</sub> =-30mA                                                               |                      | 12                   | Ω      |

|                        |                                                         | V <sub>DD</sub> =3.0V, VI=V <sub>DD</sub> , /EN=0V, I <sub>O</sub> =-15mA                                                               |                      | 12                   | Ω      |

| _ ,                    | Citah an masiatan as 3                                  | V <sub>DD</sub> =4.5V, /EN=0V, I <sub>O</sub> =+/-15mA,<br>25°C V <sub>IN</sub> = V <sub>SS</sub> , V <sub>DD</sub> /2, V <sub>DD</sub> |                      | 2                    | Ω      |

| R <sub>ON(FLAT</sub> ) | Switch on resistance <sup>3</sup>                       | $V_{DD}$ =3.0V, /EN=0V, $I_{O}$ =+/-15mA,<br>25°C $V_{IN}$ = $V_{SS}$ , $V_{DD}$ /2, $V_{DD}$                                           |                      | 10                   | Ω      |

#### Notes:

- 1. All voltages referenced to V<sub>SS</sub>

- 2. Per MIL-STD-883, method 3012

- 3. Guaranteed by Characterization

## **AC Electrical Characteristics1**

$(V_{DD} = 5.0V \pm 0.5V, 3.3V \pm 0.3V, -55^{\circ}C < T_{C} < +125^{\circ}C)$ ; Unless otherwise noted,  $T_{C}$  is per the temperature range ordered

#### **Table 6: AC Electrical Characteristics**

| Symbol            | Parameter                              | Conditions                                                        | MIN | MAX | Units |

|-------------------|----------------------------------------|-------------------------------------------------------------------|-----|-----|-------|

| t <sub>PD15</sub> | Channel Propagation Delay <sup>1</sup> | V <sub>DD</sub> = 5.0V ± 0.5V, I1=+/-15mA,<br>/EN=V <sub>SS</sub> |     | 250 | ps    |

| t <sub>EN</sub>   | Channel Enable Delay <sup>2</sup>      | V <sub>DD</sub> = 5.0V ± 0.5V                                     | 1   | 6   | ns    |

| t <sub>DIS</sub>  | Channel Disable Delay <sup>2</sup>     | V <sub>DD</sub> = 5.0V ± 0.5V                                     | 1   | 6   | ns    |

| t <sub>PD15</sub> | Channel Propagation Delay <sup>1</sup> | V <sub>DD</sub> = 3.3V ± 0.3V, I1=+/-15mA,<br>/EN=V <sub>SS</sub> |     | 250 | ps    |

| t <sub>EN</sub>   | Channel Enable Delay <sup>2</sup>      | V <sub>DD</sub> = 3.3V ± 0.3V                                     | 1   | 8   | ns    |

| t <sub>DIS</sub>  | Channel Disable Delay <sup>2</sup>     | V <sub>DD</sub> = 3.3V ± 0.3V                                     | 1   | 8   | ns    |

#### Notes:

- 1. The propagation delay through the channel is based on the RC time constant of the channel capacitance and maximum channel resistance for defined  $V_{DD}$

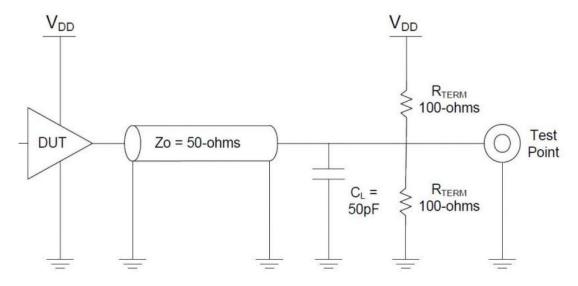

- 2. Measured at 300mV above or below steady state output voltage using output test load circuit

## **Table 7: Signal Characteristics**

| Symbol                          | Parameter                         | Conditions             | MIN | TYP | MAX | Units |

|---------------------------------|-----------------------------------|------------------------|-----|-----|-----|-------|

| X <sub>TALK</sub> <sup>1</sup>  | Channel Cross-Talk <sup>1,2</sup> | V <sub>DD</sub> = 5.0V |     |     | -60 | dB    |

| X <sub>TALK</sub> <sup>1</sup>  | Channel Cross-Talk 1,2            | V <sub>DD</sub> = 3.3V |     |     | -60 | dB    |

| ISO <sub>OFF</sub> <sup>1</sup> | Off Isolation <sup>1,2</sup>      |                        |     |     | -60 | dB    |

- 1. Guaranteed by design

- 2.  $R_L$  = 50 $\Omega$ ,  $C_L$  = 50pF, fin = 1MHz,  $V_{IN}$  = 1VRMS centered at  $V_{DD}/2$

Version #: 2.0.5

# **Timing Diagram**

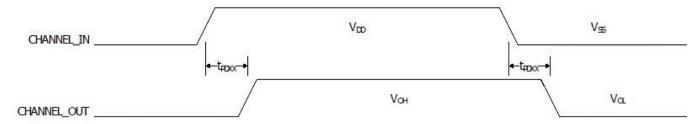

Figure 3: Channel Propagations Delay (/EN = V<sub>SS</sub>)

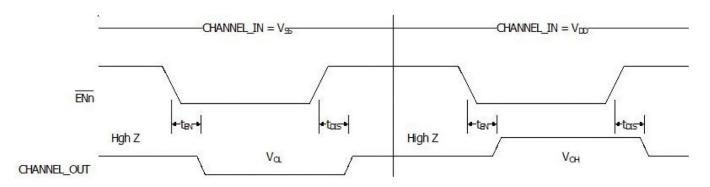

Figure 4: Enable Timing

## **Test Loads**

Figure 5. Standard Test Load

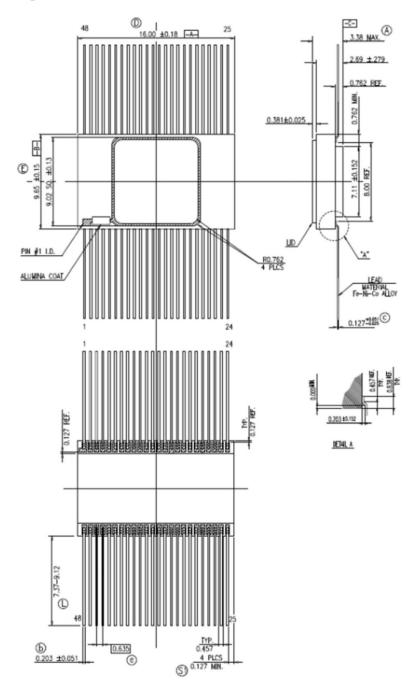

# **Package Drawings**

Figure 6: 48-Lead Flatpack

- 1. Lid is connected to V<sub>SS</sub>.

- 2. Units are in millimeters.

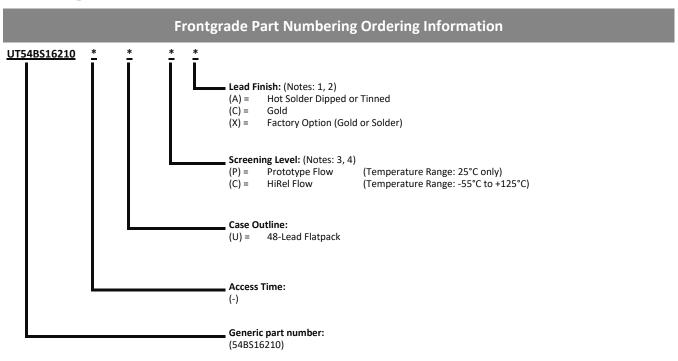

# **Ordering Information**

- 1. Lead finish (A, C, F, or X) must be specified.

- 2. If an "X" is specified when ordering, then the part marking will match the lead finish applied to the device shipped

- 3. Prototype Flow per Frontgrade Manufacturing Flows Document. Lead finish is Factory Option "C" only. Radiation is neither tested nor guaranteed.

- 4. HiRel Flow per Frontgrade Manufacturing Flows Document. Radiation TID tolerance may (or may not) be ordered.

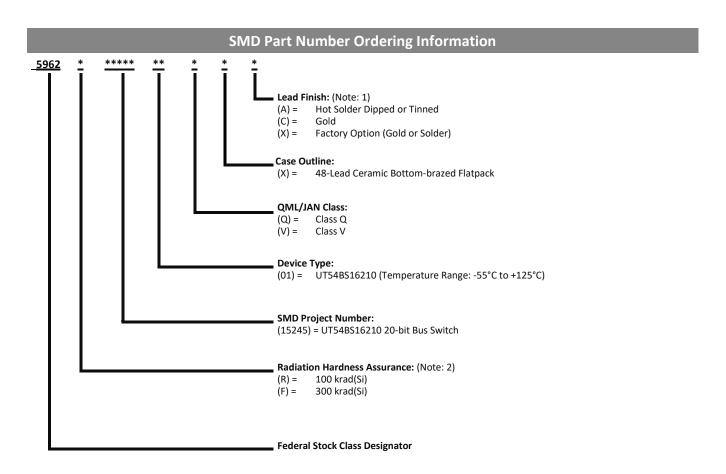

- 1. Lead finish must be specified. If "X" is specified when ordering, the factory will determine lead finish. Part marking will reflect the lead finish applied to the device shipped.

- 2. A radiation hardness assurance level must be selected. The use of "-" indicates no radiation hardness assurance guarantee.

# **Revision History**

| Date       | Revision # | Author | Change Description                                                                                                                                   | Page # |

|------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 05/01/2016 | 1.0.0      | ММ     | Updated datasheet to reflect Frontgrade logo, colors, and modified format. Updated the following specifications: RON, IIA, IDD, IDDQ, TEN, and TDIS. |        |

| 06/23/2016 | 2.0.0      | ВМ     | Released Datasheet. Updated capacitance and propagation delay. Minor formatting.                                                                     |        |

| 06/27/2016 | 2.0.1      | вм     | Package description correction: 48-Lead Flatpack                                                                                                     | 1      |

| 6/30/2016  | 2.0.2      | ВМ     | IDDQ: CONDITIONS: /EN=V <sub>DD</sub>                                                                                                                |        |

| 01/04/2017 | 2.0.3      | ВМ     | FEATURES: QML Q and V compliant part                                                                                                                 |        |

| 08/19/2021 | 2.0.5      | ВМ     | ROC Table: Input tR, tF parameter updates.                                                                                                           | 4      |

## **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> .  Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                             |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                    |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents, rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.