## UT01VS33L

#### **Features**

- 3.15V to 3.6V Operating voltage range

- Power supply (V<sub>DD</sub>) monitor set by the internal voltage reference at 3.08V

- Precision Input Voltage Monitor using an internal 0.6V voltage reference

- Watchdog Timer Circuit monitoring activity on WDI input

- Nominal timeout 1.6s

- RESET output responding to the V<sub>DD</sub> monitor and the manual reset input MR

- Nominal RESET pulse width 200ms

- RESET level valid for V<sub>DD</sub>>=1.2V

- Operating Temperature Range -55°C to +125°C

- Low Power, Typical 400uA

- Operational environment:

- Total dose: 300 krad (Si)

- SEL Immune: ≤110 MeV-cm<sup>2</sup>/mg @125°C

- SET Immune: ≤80 MeV-cm<sup>2</sup>/mg

- Packaging options:

- 8-lead dual-in-line flatpack

- Standard Microelectronics Drawing 5962-11213

- QML Q and V

#### Introduction

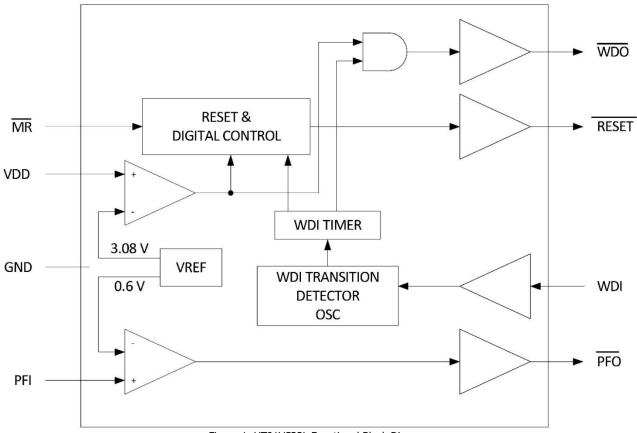

The UT01VS33L's function is to monitor vital supply and signal voltages in microprocessor systems. It provides for safe reset during power up, power down and brownout conditions by using an internal precision voltage reference.

The UT01VS33L monitors activity at an independent watchdog input by employing an internal timer and a watchdog output that goes low if the input is not toggled within 1.6s. It provides for precision voltage threshold detection on an independent voltage input which could be used for battery or supply-low monitoring of a supply voltage other than V<sub>DD</sub>.

The UT01VS33L includes an active low manual reset with a push-pull output.

### **Applications**

- Voltage Supervisor function for various systems including microprocessors, microcontrollers, DSPs and FPGAs

- Critical battery and power supply monitoring

- Replacement of older discrete solutions to improve reliability, accuracy and reduce complexity of the systems

Figure 1. UT01VS33L Functional Block Diagram

### **Pin Descriptions**

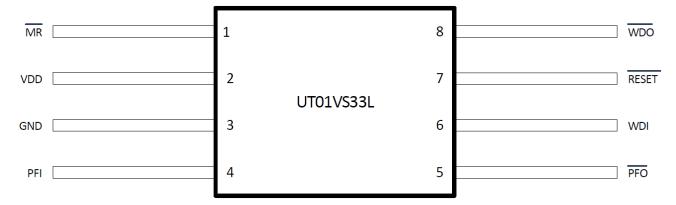

| Number | Pins  | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | MR    | Digital Input  | <b>Manual Reset Input with an internal pull-up</b> . Active low. $\overline{\text{MR}}$ low forces the reset output $\overline{\text{RESET}}$ low. Required minimum $\overline{\text{MR}}$ pulse width is 150ns. $\overline{\text{RESET}}$ is held low for duration of the reset timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

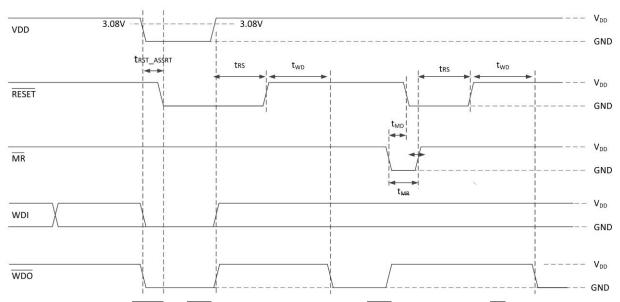

| 2      | VDD   | Supply         | <b>Power supply.</b> Operating voltage range is 3.15V to 3.6V. $V_{DD}$ level is monitored internally by a dedicated comparator circuit, which employs an internal bandgap voltage reference nominally equal to 1.25V. Every time $V_{DD}$ falls below the threshold voltage, nominally 3.08V, $\overline{RESET}$ and $\overline{WDO}$ outputs are forced low. (See $\overline{WDO}$ and $\overline{RESET}$ descriptions.) (Figure 4.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3      | GND   | Supply         | <b>Ground.</b> This pin should be tied to ground and establishes the reference for voltage detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4      | PFI   | Analog Input   | <b>Threshold detector input</b> . Voltage on this input is fed directly to an internal comparator where it is compared to the voltage reference of 0.6V. It can be used for detection of low battery or power failure of voltage supplies other than V <sub>DD</sub> . When voltage at PFI input drops below its threshold value of 0.6V, PFO output is forced low, otherwise, stays high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5      | PFO   | Digital Output | Threshold detector output. Active low push-pull output driver. It responds directly to PFI input. If PFI voltage is below the bandgap reference voltage, PFO is low. If PFI is above the reference voltage, PFO output is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

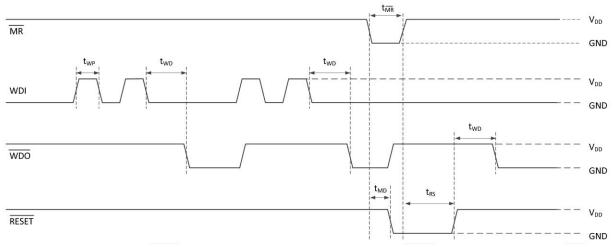

| 6      | WDI   | Digital Input  | Watchdog timer input pin. This pin is typically used to monitor microprocessor activity. It can assume three states: low, high and float. If WDI is floating or connected to a high impedance three state buffer, the watchdog timer is not active, and the corresponding watchdog output WDO is high. Watchdog timer is also not active any time RESET is low. Providing that RESET is not asserted, any change of state at WDI that is longer than 100ns will start the timer, or restart it, if the timer is already running (Figure 3.). If there is no activity within the timeout period, nominally 1.6s, the timer will stop running and WDO output will go low (Figure 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7      | RESET | Digital Output | Reset output. Active low push-pull output driver. This pin is pulled up with a resistor consistent with the sink and voltage current as specified in the electrical characteristics table. This output responds to both: $V_{DD}$ monitoring circuits and the manual reset input $\overline{MR}$ .  On power up, $\overline{RESET}$ is guaranteed to be logic low for all $V_{DD}$ values from 1.2V up to the reset threshold, nominally 3.08V. Once this threshold is reached, an internal $\overline{RESET}$ timer is activated. During the countdown $\overline{RESET}$ output is kept low. It is raised high upon completion of countdown, typically after 200ms. If a brown out condition occurs during the reset timer countdown, the reset timer would be reset and another countdown would start after $V_{DD}$ levels were restored above the reset threshold. On power down, when $V_{DD}$ falls below the threshold voltage, $\overline{RESET}$ goes low and is guaranteed to stay low until $V_{DD}$ drops below 1.2V. If $\overline{MR}$ is asserted low, $\overline{RESET}$ is forced low and the reset timer is kept reset. When $\overline{MR}$ is released high, the timer is activated and $\overline{RESET}$ is kept low until completion of the reset timeout, when it is raised high. |

| Number      | Pins    | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number<br>8 | WDO WDO | Type  Digital Output | <b>Watchdog output.</b> Active low push-pull output driver. This pin is usually connected to a non-maskable interrupt input of a microprocessor. On power up, $\overline{\text{WDO}}$ responds to $V_{\text{DD}}$ monitoring circuitry. It stays low until the reset threshold, 3.08V nominally, is reached. At that point, $\overline{\text{WDO}}$ is raised high. The internal watchdog timer is activated after $\overline{\text{RESET}}$ is released. If there is no activity on WDI input, $\overline{\text{WDO}}$ goes low after the watchdog timer times out, which is typically after 1.6sec. Any activity on WDI will force $\overline{\text{WDO}}$ output to go high and the watchdog timer will be activated. If WDI is floating or connected to a high impedance buffer output, the timer is kept in a reset state and $\overline{\text{WDO}}$ stays high. When VDD drops below 3.08V, $\overline{\text{WDO}}$ goes low regardless of whether the watchdog timer has timed out or not. $\overline{\text{RESET}}$ goes low simultaneously which prevents an interrupt. |

|             |         |                      | If WDI input is left unconnected, WDO can be used as a low line output. Since a floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |         |                      | VDD drops below 3.08V, WDO goes low regardless of whether the watchdog timer has                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |         |                      | WDI disables the internal watchdog timer, $\overline{\text{WDO}}$ goes low when $V_{DD}$ drops below 3.08V, thus, functioning as a low line output. (Figure 4.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 2: UT01VS33L Pin Configuration

### **Operational Environment**

| Parameter                           | Limit | Units                   |

|-------------------------------------|-------|-------------------------|

| Total Ionizing Dose (TID)           | 300   | Krad (Si)               |

| Single Event Latchup Immune (SEL)   | ≤110  | MeV-cm <sup>2</sup> /mg |

| Single Event Transient Immune (SET) | ≤80   | MeV-cm <sup>2</sup> /mg |

## UT01VS33L

### **Absolute Maximum Ratings <sup>1</sup>**

(Referenced to GND)

| Symbol            | Parameter                                | Limits                           | Units |

|-------------------|------------------------------------------|----------------------------------|-------|

| $V_{DD}$          | Voltage supply                           | 7.2                              | V     |

| T <sub>3</sub>    | Maximum junction temperature             | 175                              | °C    |

| Т                 | Storage temperature                      | -65 to +150                      | °C    |

| $P_D$             | Power dissipation                        | 2.5                              | W     |

| $V_{in}$          | Input voltages                           | -0.3V to (V <sub>DD</sub> +0.3V) | V     |

| T <sub>iead</sub> | Lead Temperature (soldering, 10 seconds) | +300                             | °C    |

| Θις               | Thermal resistance, junction-to-case     | 15                               | °C/W  |

| $V_{ESD}$         | ESD <sub>HBM</sub>                       | 1000                             | V     |

#### Note:

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating

only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational

sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods

may affect device reliability.

### **Recommended Operating Conditions**

| Symbol   | Parameter               | Limits      | Units |

|----------|-------------------------|-------------|-------|

| $V_{DD}$ | Positive supply voltage | 3.15 to 3.6 | V     |

| Tc       | Case temperature range  | -55 to +125 | °C    |

| GND      | Negative supply voltage | 0.0         | V     |

### **Electrical Characteristics 1,2**

$(V_{DD} = 3.15V \text{ to } 3.6V: -55^{\circ}C \le T_{C} \le +125^{\circ}C)$

| Symbol                       | Parameter                                                                   | Condition                                                      | MIN                 | MAX   | Unit                     |

|------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|---------------------|-------|--------------------------|

| ower Supp                    | lly                                                                         |                                                                | _                   |       |                          |

| $I_{DD}$                     | V <sub>DD</sub> supply current                                              | V <sub>DD</sub> =3.6V                                          |                     | 450   | μΑ                       |

| igital Inpu                  | ts and Outputs ( $\overline{MR}$ , $\overline{RESET}$ , WDI, $\overline{W}$ | /DO, PFO)                                                      |                     |       |                          |

| $V_{IL\_WDI}$                | Digital input low                                                           | V <sub>DD</sub> =3.15V                                         |                     | 0.6   | V                        |

| $V_{\text{IH\_WDI}}$         | Digital input high                                                          | $V_{DD}=3.6V$                                                  | $0.7xV_{DD}$        |       | V                        |

| $V_{IL\_\overline{MR}}$      | Manual reset input low                                                      | $V_{DD}$ =3.15 $V$                                             |                     | 0.6   | V                        |

| $V_{IH\_\overline{MR}}$      | Manual reset input high                                                     | V <sub>DD</sub> =3.6V                                          | 0.7xV <sub>DD</sub> |       | V                        |

| V <sub>OL</sub>              | Digital output low                                                          | $V_{DD}$ =3.15 $V$ , $I_{SINK}$ = 500 $\mu$ A $\overline{WDO}$ |                     | 0.3   | V                        |

| V <sub>OL</sub>              | Digital output low                                                          | $V_{DD}$ =3.15V, $I_{SINK}$ =1.2mA<br>$\overline{RESET}$       |                     | 0.3   | V                        |

| $V_{OL}$                     | Digital output low                                                          | $V_{DD}$ =3.15V, $I_{SINK}$ =1.2mA $\overline{PFO}$            |                     | 0.3   |                          |

| V <sub>OH</sub> <sup>3</sup> | Digital output high                                                         | $V_{DD}$ =3.15V, $I_{SOURCE}$ =500μA                           | 0.8xV <sub>DD</sub> |       | V                        |

|                              | Threshold Voltages                                                          |                                                                |                     |       |                          |

| t <sub>RST-ASSRT</sub> 4     | V <sub>DD</sub> falling reset assertion                                     | $V_{DD} < 3.0V$                                                | 0.7                 | 1.8   | μS                       |

| t <sub>RS</sub>              | Reset pulse width                                                           | $V_{DD}$ =3.15 $V$                                             | 140                 | 280   | ms                       |

| t <sub>WD</sub>              | Watchdog time-out period                                                    | $V_{DD}=3.6V$                                                  | 1.0                 | 2.25  | S                        |

| t <sub>WP</sub>              | Watchdog input pulse width                                                  | $V_{DD}$ =3.15V, $V_{IL}$ = 0.4V $V_{IH}$ = 0.8 * $V_{DD}$     | 100                 |       | ns                       |

| $V_{RT}$                     | Reset threshold voltage                                                     |                                                                | 3.0                 | 3.15  | V                        |

| $V_{RTHYS}$                  | Reset threshold voltage hysteresis                                          |                                                                | 20                  |       | mV                       |

| t <sub>MR</sub>              | Manual reset (MR) input pulse width                                         | V <sub>DD</sub> =3.15V                                         | 150                 |       | ns                       |

| t <sub>MD</sub>              | Manual reset (MR) to reset out delay                                        |                                                                |                     | 100   | ns                       |

| nalog Inpu                   | it PFI                                                                      |                                                                |                     |       |                          |

| ${ m I_{PFI}}^4$             | Threshold detector input (PFI) current                                      | $V_{DD}$ =3.6 $V$                                              | -20                 | 20    | nA                       |

| $V_{\text{PFI}}$             | Threshold detector input (PFI) threshold voltage                            | V <sub>DD</sub> =3.3V                                          | 0.576               | 0.624 | V                        |

| $I_{\overline{MR}}$          | Manual reset pull-up current                                                | $V_{DD}$ =3.6V, $\overline{MR}$ =0.0V                          | -250                | -25   | μА                       |

| $t_{RPFI}$                   | PFI rising threshold crossing to PFO delay                                  |                                                                |                     | 20    | μS                       |

| $T_{FPFI}$                   | PFI falling threshold crossing to PFO delay                                 |                                                                |                     | 40    | μS                       |

| $I_{WDI}$                    | Watchdog input current                                                      | WDI pin = $V_{DD}$ = 3.6V<br>WDI pin = 0V, $V_{DD}$ = 3.6V     | -20                 | 20    | μ <b>Α</b><br>μ <b>Α</b> |

## UT01VS33L

#### **Notes:**

- 1) For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance at 25°C per MIL-STD-883 Method 1019, Condition A, up to the maximum TID level procured (see ordering information).

- 2) Unless otherwise specified,  $V_{DD} = 3.15V$  to 3.6V,  $-55^{\circ}C \le T_{C} \le +125^{\circ}C$ . RESET is the only parameter operable within 1.2V and the minimum recommended operating supply voltage.

- 3)  $V_{OH}$  characterization applies to  $\overline{WDO}$ ,  $\overline{PFO}$  and  $\overline{RESET}$ .

- 4) Guaranteed by design, but not tested.

Figure 3. WDI and WDO timing waveforms. Reset externally triggered by MR

Figure 4.  $\overline{\text{RESET}}$  and  $\overline{\text{WDO}}$  are driven low for VDD <3.08V.  $\overline{\text{WDO}}$  is driven high when  $\overline{\text{MR}}$  is low

# UT01VS33L

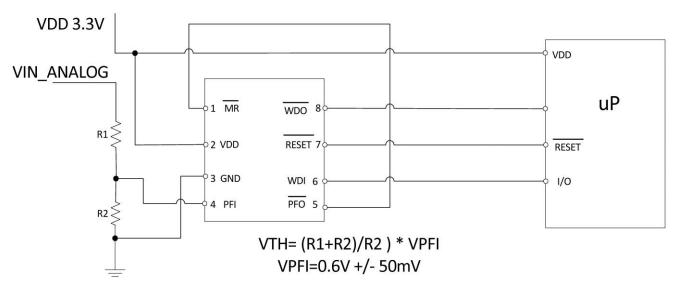

Figure 5. UT01VS33L Under Voltage Monitor and Detection

Shown in Figure 5 is an application for monitoring the under voltage of a power supply connected to a microprocessor or ASIC. If the analog voltage monitored falls below the desired threshold value, the  $\overline{\text{PFO}}$  output connected to the  $\overline{\text{MR}}$  input will transition low causing the  $\overline{\text{RESET}}$  output to be asserted low indicating an under voltage condition.

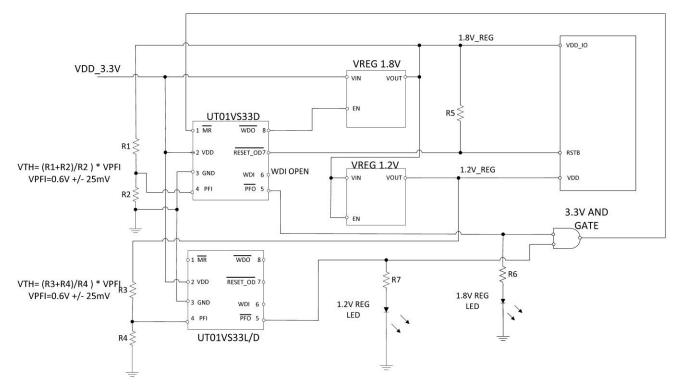

Figure 6. Under Voltage Monitoring and sequencing of 1.8V and 1.2V Power Supplies

Shown in Figure 6 are two Voltage Supervisors configured to monitor both the 1.8V and 1.2V power supplies of a system. The 1.8V regulated supply is monitored by the PFI pin of the top Voltage Supervisor, while the 1.2V regulated supply is monitored by the PF pin of the bottom Voltage Supervisor. The cross coupled connection of  $\overline{\text{PFO}}$  to  $\overline{\text{MR}}$  assures that  $\overline{\text{RESET\_OD}}$  will be asserted when a brown out occurs on either the 1.8V or 1.2V regulated supplies.

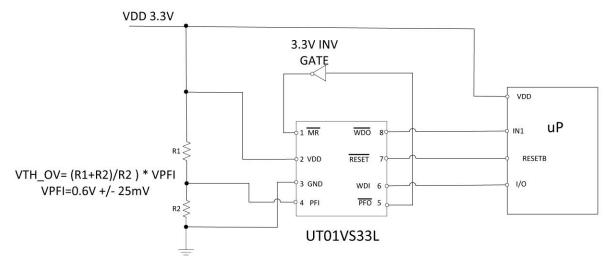

Figure 7. UT01VS33L Over Voltage Power Supply Monitoring and Reset Figure 7. UT01VS33D Over Voltage Power Supply Monitoring and Reset

Shown in Figure 7 is an application to monitor and detect power supply over voltage through the use of the PFI pin. When the voltage at the PFI input, (VTH) exceeds VREF, (0.6V) the  $\overline{\text{PFO}}$  output transitions from low to high causing the  $\overline{\text{MR}}$  output to transition from high to low. This asserts a  $\overline{\text{RESET}}$  indicating the voltage being monitored has exceeded the over voltage monitor limit.

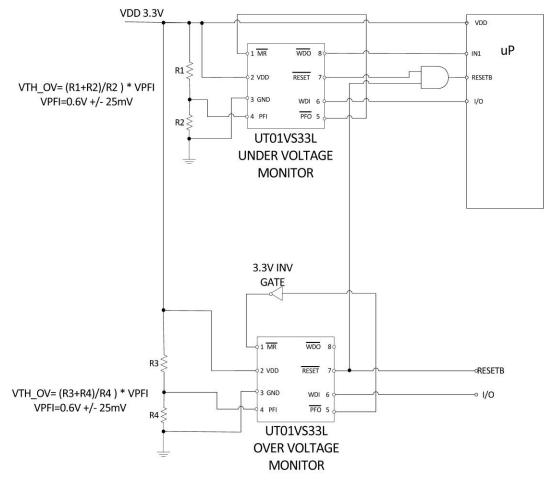

Figure 8. UT01VS33L Under Voltage and Over Voltage Power Supply Monitoring and Reset

Shown in Figure 8 is an application using two UT01VS33L Voltage Supervisors to monitor both under voltage and over voltage of a power supply. In this application the top Voltage Supervisor monitors the under-voltage of a 3.3V power supply while the bottom Voltage Supervisor monitors the over voltage of the same 3.3V power supply.

The 3.3Vsupply is monitored through the PFI input of both Voltage Supervisors. Resistor values for both under voltage and over voltage monitoring can be set to accommodate a range of power supply voltages.

During normal operation where VDD is within the allowed range (VDD\_UND < VDD < VDD\_OV),  $\overline{\text{RESET}}$  of both Voltage Supervisors will be at logic high level. The Table 1 below shows the truth table for functional, under voltage detection and over voltage detection.

#### **Table 1. Under Voltage Over Voltage Truth Table**

| VDD              | PFO_UND | PFO_OV | RESET_UND | RESET_OV | RESET | uP or ASIC Mode |

|------------------|---------|--------|-----------|----------|-------|-----------------|

| Normal Operation | HIGH    | LOW    | HIGH      | HIGH     | HIGH  | Normal          |

| VDD < VDD_UND    | LOW     | LOW    | LOW       | HIGH     | LOW   | Reset Asserted  |

| VDD > VDD_OV     | HIGH    | HIGH   | HIGH      | LOW      | LOW   | Reset Asserted  |

#### Note:

1) UND specifies under voltage case. -OV specifies overvoltage case

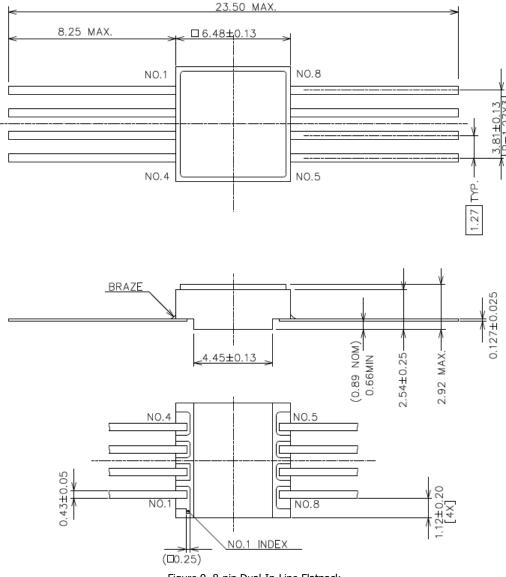

Figure 9. 8-pin Dual-In-Line Flatpack

#### Notes:

- 1) Package material: Opaque 90% minimum alumina ceramic.

- 2) All exposed metal areas must be gold plated 100 to 225 microinches thick over electroplated nickel undercoating 100 to 350 microinches thick per MIL-PRF-38535.

- 3) The seal ring is electrically connected to VSS.

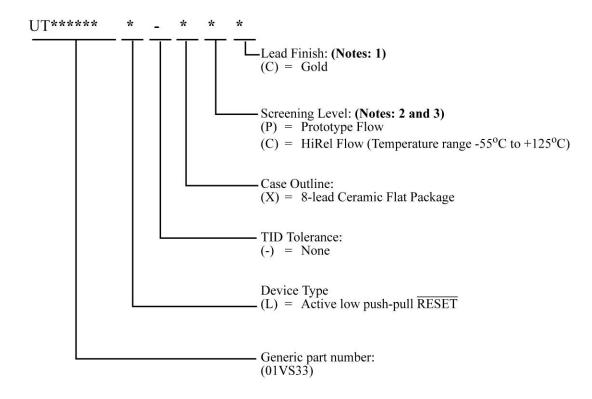

### **Ordering Information**

### **UT01VS33L Voltage Supervisor**

#### Notes:

- 1) Lead finish is "C" (Gold) only.

- 2) Prototype flow per CAES Manufacturing Flows Document. Devices are tested at 25°C only. Radiation neither tested nor guaranteed.

- 3) HiRel Flow per CAES Manufacturing Flows Document. Radiation neither tested nor guaranteed

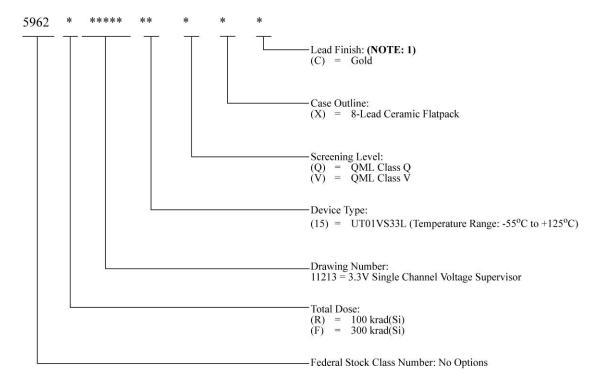

### **UT01VS33L Voltage Supervisor: SMD**

#### Note:

1) Lead finish is "C" (gold) only.

### **Data Sheet Revision History**

| <b>Revision Date</b> | Description of Change                                                                                       | Author |

|----------------------|-------------------------------------------------------------------------------------------------------------|--------|

| 12-16                | CAES Datasheet format added along with edit to SMD Ordering on Device Type and Gold Finish.                 | RL     |

| 10-18                | Page 6 - Electrical Characteristics Table - Edits to $V_{OL}$ , $t_{WP}$ , $V_{RT}$ , $t_{MP}$ to match SMD | BM     |

| 08-22                | Page 12 – Updated Package Drawing to current version.                                                       | BM     |

### UT01VS33L

### **Datasheet Definitions**

|                       | DEFINITION                                                                                                                                                                                                                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the datasheet is subject to change. Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | CAES reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                    |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                     |

The following United States (U.S.) Department of Commerce statement shall be applicable if these commodities, technology, or software are exported from the U.S.: These commodities, technology, or software were exported from the United States in accordance with the Export Administration Regulations. Diversion contrary to U.S. law is prohibited.

Cobham Colorado Springs Inc. d/b/a Cobham Advanced Electronic Solutions (CAES) reserves the right to make changes to any products and services described herein at any time without notice. Consult an authorized sales representative to verify that the information in this data sheet is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing; nor does the purchase, lease, or use of a product or service convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties.